PCI11101 PCIe交换机集成USB3.2主机控制器技术解析

描述

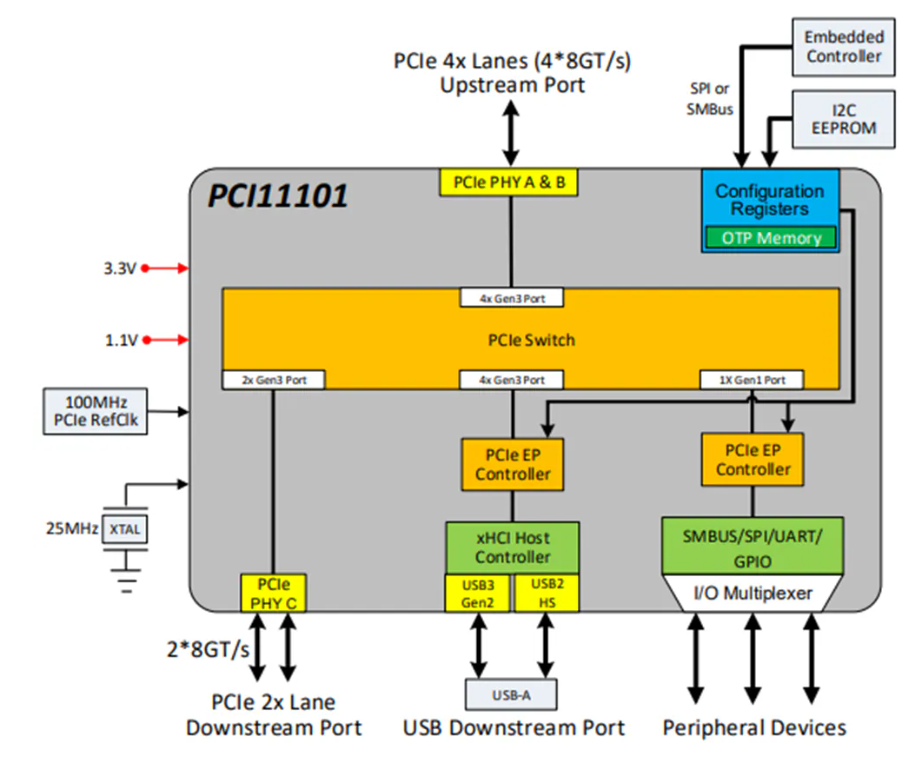

Microchip Technology PCI11101 PCIe交换机(带USB 3.2主机控制器)将USB 3.2 Gen 2主机控制器和可编程I/O相结合。 Microchip Technology PCI11101具有4通道(4x8GT/s)上行端口和2通道(2x8GT/s)下行端口,可满足嵌入式应用对更高带宽PCIe子系统的需求。 该器件通过了PCIe版本4.x规范中GEN4合规性认证,可使用一个或多个通道实现PCIe上行,从而实现灵活的系统架构。PCI11101可确保从外部接口到交换结构和端点控制器的PCIe合规性。

数据手册:*附件:Microchip Technology 带USB3.2主机控制器的PCI11101 PCIe交换机数据手册.pdf

特性

- 集成式PCI交换机结构

- 最大有效载荷:512字节

- 集成式PCIe物理接口

- 4通道 (4x8GT/s) 上行端口

- 支持单通道、双通道或四通道链路

- 2通道 (2x8GT/s) 下行端口

- 集成USB 3.2 Gen 2 (10Gbps) 物理 接口

- 集成式xHCI USB 3.2 Gen 2(10Gbps)USB主机控制器

- 10Gbps Gen 2 PHY

- USB HS/FS/LS PHY

- 两个外部电源:+3.3V、+1.1V

- 全面的电源管理功能

- PCIe 3.1低功耗子状态(LPSS)L2(带AUX 电源)

- 电源和I/O

- 集成上电复位电路,具有可配置的欠压/过压保护

- 闭锁性能超过150mA,符合EIA/JESD 78 II类标准

- JEDEC 3A级ESD性能

- UART

- RS232/RS485 的产品评估板

- 自动方向控制

- 支持标准和高级速度

- 基本或全面信号支持

- 其他功能

- 多功能GPIO

- 可编程引脚多路复用器

- 能够使用低成本25MHz晶体或时钟,以减少BOM

- SPI外设接口

- SMBus目标接口

- SMBus控制器接口

- PVT传感器

- JTAG TAP

- 封装

- 无铅、符合RoHS指令的132引脚DRQFN封装

- 环境条件

- 有商业和工业级可供选择

方框图

PCI11101 PCIe交换机集成USB3.2主机控制器技术解析

一、核心架构与功能特性

- PCIe Gen4交换架构

- 支持8GT/s线速率,通过PCIe 4.x规范认证

- 提供4x8GT/s上行端口(支持单/双/四链路配置)和2x8GT/s下行端口

- 集成512字节最大负载大小的PCIe交换矩阵

- USB 3.2 Gen2主机控制器

- 符合xHCI规范,支持10Gbps传输速率

- 集成USB Type-A/M.2接口PHY层,含过流检测(OCS)和端口控制功能

- 可编程I/O子系统

- 通过引脚复用器支持SMBus/SPI/UART/GPIO灵活配置

- 提供多功能GPIO、JTAG TAP接口及PVT传感器集成

二、关键硬件设计要点

- 电源管理设计

- 双电源输入(+3.3V和+1.1V)

- 支持PCIe 3.1 LPSS低功耗状态(L2需辅助电源)

- 集成电压监控与ESD保护(JEDEC Class 3A标准)

- 时钟架构

- 仅需25MHz外部晶体或时钟输入

- 内置时钟发生器降低BOM成本

- 封装与可靠性

- 132-pin DRQFN封装(RoHS合规)

- 工业级温度支持(-40°C至+85°C)

- 锁存保护电流>150mA(EIA/JESD78 Class II)

三、典型应用场景

- 机器视觉系统

- 通过PCIe高速传输摄像头数据

- 利用USB 3.2 Gen2接口连接多光谱传感器

- 服务器BMC扩展

- 替代传统PCH实现外设管理

- 通过SMBus控制IPMI设备

- 数学加速卸载

- PCIe Gen4带宽满足FPGA/ASIC协处理器互联需求

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

IDT 89HPES32NT24BG2:高性能PCIe Gen2系统互连交换机深度解析2026-02-09 347

-

Microchip PCI11400 PCIe交换机技术解析与应用指南2025-10-10 910

-

Microchip Switchtec™ PFX Gen 5 PCIe交换机技术解析与应用指南2025-10-06 1764

-

Microchip推出全新PCI100x系列Switchtec PCIe 4.0交换机2025-01-20 1779

-

PCIe交换机与路由器的区别2024-11-26 2057

-

如何简化PCIe 6.0交换机的设计2024-07-05 1762

-

汇聚交换机和核心交换机区别2024-01-22 8723

-

以太网交换机的升级版:PCIe交换机2023-07-17 4257

-

pcie2.0交换机资料2023-03-27 861

-

LTC1623:SM巴士双打SMV高级交换机控制器数据Sheet2021-05-22 832

-

工业控制交换机和工业交换机的区别2020-01-21 2909

-

PCIe_交换机产品列表_产品快照2016-01-06 703

-

交换机和路由器2009-01-08 4548

全部0条评论

快来发表一下你的评论吧 !