PCI11414 PCIe交换机技术解析与应用设计指南

描述

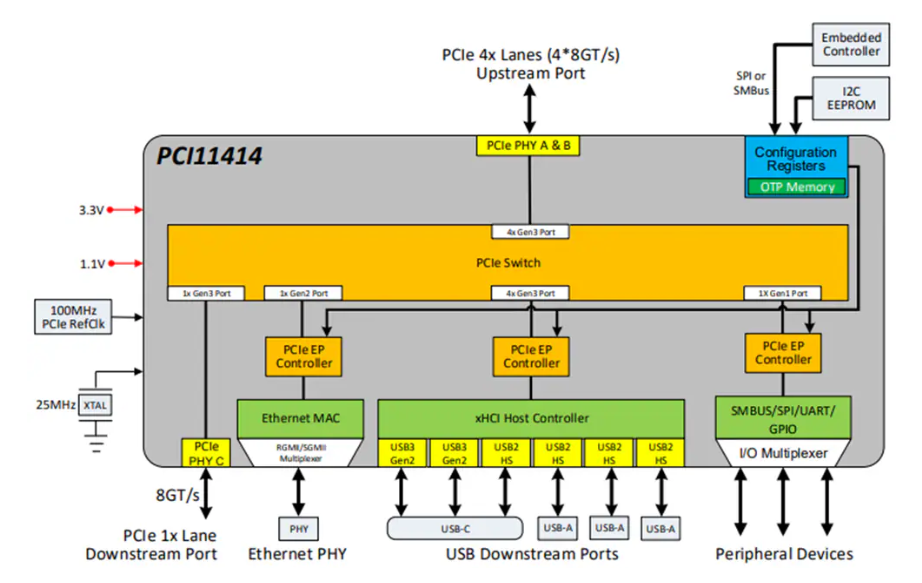

Microchip Technology PCI11414 PCIe交换机(带USB 3.2、MAC和I/O)将USB 3.2 Gen 2主机控制器、以太网MAC和可编程I/O相结合。 Microchip Technology PCI11414拥有4通道(4x8GT/s)上行端口和1通道(1x8GT/s)下行端口,非常适用于提高嵌入式应用中的PCIe带宽。 该器件通过PCIe修订版4.x认证,最大线路速率为8GT/s。根据需要PCIe上行使用单个或多个通道。PCI11414可确保从外部接口到交换结构和端点控制器的PCIe合规性。

数据手册:*附件:Microchip Technology PCI11414 PCIe交换机(带USB 3.2、MAC和IO)数据手册.pdf

特性

- 集成式PCI交换机结构

- 最大有效载荷:512字节

- 集成式PCIe物理接口

- 4通道 (4x8GT/s) 上行端口

- 支持单通道、双通道或四通道链路

- 单通道 (1x8GT/s) 下行端口

- 集成USB 3.2 Gen 2 (10Gbps) 物理 接口

- 集成式xHCI USB 3.2 Gen 2(10Gbps)USB主机控制器

- 2x 10Gbps Gen 2 PHY

- 4x USB HS/FS/LS PHY

- 多种配置选项,适用于USB Type-C®或Type-A 2.5Gbps以太网MAC

- 符合IEEE 802.3标准

- RGMII支持10/100/1000Mbps

- SGMII支持1Gbps

- SGMII+支持2.5Gbps

- 巨型帧支持

- 精密时间协议

- IEEE 1588-2008 E2E和P2P一步和两步支持

- IEEE 1588-2008可编程时间比较输出(例如1PPS)

- 全面的电源管理功能

- PCIe 3.1低功耗子状态(LPSS)L2(带AUX 电源)

- 封装

- 无铅、符合RoHS指令的164引脚DRQFN封装

- 电源和I/O

- 集成上电复位电路,具有可配置的欠压/过压保护

- 闭锁性能超过150mA,符合EIA/JESD 78 II类标准

- JEDEC 3A级ESD性能

- UART

- RS232/RS485 的产品评估板

- 自动方向控制

- 支持标准和高级速度

- 基本或全面信号支持

- 其他功能

- 多功能GPIO

- 可编程引脚多路复用器

- 能够使用低成本25MHz晶体或时钟 ,以减少BOM

- SPI外设接口

- SMBus目标接口

- SMBus控制器接口

- PVT传感器

- JTAG TAP

- 环境条件

- 有商业级和工业级温度等级可供选择

框图

PCI11414 PCIe交换机技术解析与应用设计指南

异构集成架构

PCI11414采用单芯片集成设计,包含:

- PCIe Gen4交换矩阵:4x8GT/s上行端口 + 1x8GT/s下行端口,支持单/双/四链路配置

- USB 3.2 Gen2主机控制器:集成xHCI协议栈,提供1×Type-C(10Gbps)+3×Type-A(USB2.0)接口

- 2.5Gbps以太网MAC:支持RGMII/SGMII/SGMII+接口,兼容802.3bz标准(10/100/1000/2500Base-T)

- 可编程I/O子系统:支持SMBus/SPI/UART/GPIO复用,通过PCIe端点控制器访问

二、硬件设计要点

- 接口时序控制

- PCIe PHY:需满足Gen4眼图规范(8GT/s),参考时钟抖动<1ps RMS

- USB Type-C:CC1/CC2引脚需配置5.1kΩ下拉电阻(标准Type-C检测)

- RGMII时序:TX_CLK与数据偏移需<0.3ns(IEEE 802.3-2018 Clause 35)

- 电源管理设计

电源域 电压 最大纹波 旁路电容要求 PCIe PHY 1.1V ±30mV 4×22μF MLCC USB 3.2 3.3V ±50mV 2×10μF钽电容

三、开发注意事项

PCB布局规范

- 164-DRQFN封装:13×13mm尺寸,0.5mm间距焊盘

- 关键信号线要求:

- PCIe差分对:100Ω阻抗控制,长度匹配±5mil

- USB D+/D-:包地处理,避免与时钟线平行走线

散热设计

- 结温计算:Tj=Ta+(θja×Pd),工业级θja=28°C/W

- 建议使用4层板+2oz铜厚,底部裸露焊盘需8×8mm散热过孔阵列

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Microchip PCI11400 PCIe交换机技术解析与应用指南2025-10-10 902

-

Microchip Switchtec™ PFX Gen 5 PCIe交换机技术解析与应用指南2025-10-06 1751

-

工业级交换机选型指南2025-04-17 1719

-

Microchip发布全新Switchtec™ PCIe 4.0交换机系列2025-01-22 1473

-

Microchip推出全新PCI100x系列Switchtec PCIe 4.0交换机2025-01-20 1763

-

PCIe交换机与路由器的区别2024-11-26 2046

-

如何简化PCIe 6.0交换机的设计2024-07-05 1748

-

P411W-32P PCIe 4.0 NVMe交换机适配器用户指南2023-08-23 1338

-

以太网交换机的升级版:PCIe交换机2023-07-17 4250

-

pcie2.0交换机资料2023-03-27 858

-

核心交换机、汇聚交换机与普通交换机的区别介绍2020-03-19 14215

-

PCIe_交换机产品列表_产品快照2016-01-06 700

全部0条评论

快来发表一下你的评论吧 !