74hc154的引脚功能是什么?74hc154引脚作用详解

应用电子电路

描述

74HC154是一款高速CMOS器件, 兼容低电压ttl电路,遵守jedec标准。 具有8位移位寄存器和一个存储器,三态输出功能。 移位寄存器和存储器是分别的时钟。 数据在schcp的上升沿输入,在stcp的上升沿进入的存储寄存器中去。如果两个时钟连在一起,则移位寄存器总是比存储寄存器早一个脉冲。 移位寄存器有一个串行移位输入(ds),和一个串行输出(q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能oe时(为低电平),存储寄存器的数据输出到总线。

8位串行输入/输出或者并行输出移位寄存器,具有高阻关断状态。三态。

2、特点:8位串行输入 /8位串行或并行输出 存储状态寄存器,三种状态

输出寄存器可以直接清除 100mhz的移位频率

3、输出能力: 并行输出,总线驱动; 串行输出;标准中等规模集成电路

154移位寄存器有一个串行移位输入(ds),和一个串行输出(q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能oe时(为低电平),存储寄存器的数据输出到总线。

4、参考数据:

cpd决定动态的能耗,

pd=cpd×vcc×f1+∑(cl×vcc2×f0)

f1=输入频率,cl=输出电容 f0=输出频率(mhz) vcc=电源电压

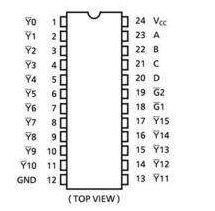

5、引脚说明

符号 引脚 描述

q0…q7 15, 1, 7 并行数据输出

gnd 8 地

q7’ 9 串行数据输出

mr 10 主复位(低电平)

shcp 11 移位寄存器时钟输入

stcp 12 存储寄存器时钟输入

oe 13 输出有效(低电平)

ds 14 串行数据输入

vcc 16 电源

6、功能表

输入 输出 功能

shcp stcp oe mr ds q7’ qn

× × l ↓ × l nc mr为低电平时仅仅影响移位寄存器

× ↑ l l × l l 空移位寄存器到输出寄存器

× × h l × l z 清空移位寄存器,并行输出为高阻状态

↑ × l h h q6 nc 逻辑高电平移入移位寄存器状态0,包含所有的移位寄存器状态 移入,例如,以前的状态6(内部q6”)出现在串行输出位。

× ↑ l h × nc qn’ 移位寄存器的内容到达保持寄存器并从并口输出

↑ ↑ l h × q6’qn’ 移位寄存器内容移入,先前的移位寄存器的内容到达保持寄存器并出。

7、注释

h=高电平状态

l=低电平状态

↑=上升沿

↓=下降沿

z=高阻

nc=无变化

×=无效

当mr为高电平,oe为低电平时,数据在shcp上升沿进入移位寄存器,在stcp上升沿输出到并行端口。

-

设计分享|74HC154译码器实现流水灯2022-12-12 3182

-

74HC154和74HCT154高速硅栅CMOS器件的数据手册免费下载2018-12-05 1430

-

74HC154的简单介绍 74hc154应用电路图分析2018-07-19 25441

-

74ls154与74hc154能通用吗?有什么区别2018-05-07 15781

-

74hc154译码器2017-11-02 10727

-

74HC154级联怎么做?2017-07-03 6617

-

74HC154英文手册2016-11-02 945

-

基于8051的Proteus仿真-74HC154译码器应用2016-09-06 855

-

74HC154英版数据手册2016-08-26 1126

-

74HC595和74HC154在proteus仿真不能正常运行的原因2015-05-31 6660

-

74hc154的工作电流2014-12-29 3169

-

74HC154中文资料2012-12-20 4867

全部0条评论

快来发表一下你的评论吧 !