2020年开发3纳米Foundry制程_芯片设计费将高达15亿

电子说

描述

三星电子先前发布,到2020年开发3纳米Foundry制程。据分析称3纳米Foundry制程芯片设计费用将高达15亿美金。虽芯片设计费用的增长倍数极高,但据专家分析称其电流效率和性能提升幅度并没有与费用成正比,而且考虑到高额的费用,能设计3纳米工程的企业屈指可数。

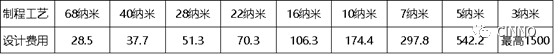

7月17日半导体市调机构International Business Strategy(IBS)分析称3纳米芯片工程的芯片设计费用将高达4亿至15亿美金。IBS说明,在设计复杂度相对较高的GPU等芯片设计费用最高。该公司资料显示28纳米芯片的平均设计费用为5130美金,而采用FinFET技术的7纳米芯片设计费用为2亿9780万美金,是将近6倍的涨幅。半导体芯片的设计费用包含IP、Architecture、检查、物理验证、软件、试产品制作等费用。

这也是半导体行业Fabless工厂一直青睐16纳米FinFET和三星的14纳米FinFET制程的理由。对Foundry厂商来说成本也是颇为伤脑筋的事情,不仅如此3纳米制程难度也颇高。

三星电子的3纳米制程将首次使用GAAE(Gate-All-AroundEarly), GAAP(Gate-All-Around Plus)技术,并起名为MBCFET(MultiBridge Channel FET)。技术的核心为确保每个Gate通道的电流存在。若FinFET结构为3面电流,GAA为Gate的所有面都要确保有电流,电流通道变大后随之性能也将提升。

三星电子的MBCFET技术为美国IBM和GF共同开发。若FinFET为鱼鳞状的Gate竖向排列的话,GAA为Gate横向叠加排列方式。为生产此种Gate结构需要Pattern显影、蒸镀、蚀刻等一系列工程的革新,并且为了减少寄生电容还要导入替代铜的钴、钌等新材料。

业界人士称:3纳米工程开发与芯片设计若有庞大财源的支持下是有可行性,但关键在于是否值得如此投资。而且可使用此种工程的公司也就只有高通、苹果、英伟达、苹果等少数公司,这也将是3纳米工程的绊脚石之一。

制造工程所需半导体设计费用(来源:IBS,单位:百万美金)

-

2020年制造业物联网支出将高达1275亿美元2016-09-01 765

-

传台积电3纳米制程拟转美国设厂2017-03-20 1135

-

台湾科技部宣布40亿半导体射月计划,将主攻3纳米制程技术,力拼2022年量产2018-06-29 4952

-

三星揭露3纳米制程技术路线图以及7纳米投产进度2018-09-05 5220

-

英特尔宣布追加10亿美元用于14纳米制程扩产后 10纳米制程量产或将提早半年2018-10-08 3724

-

台积电2020年上半年7纳米+制程进入量产的消息获得证实2019-01-22 2582

-

三星预计在2021年推出3纳米制程产品 未来将与台积电及英特尔进行抗衡2019-05-15 3898

-

三星将投入7608亿实现3纳米制程2022年量产2020-11-26 2527

-

2020年特斯拉损失高达401亿美元2021-01-07 3578

-

2020年谷歌的云业务亏损高达56.1亿美元2021-02-03 1816

-

2020年全球芯片采购支出高达4498亿美元2021-02-18 2130

-

台积电:预计2022年完成5纳米系统整合单芯片开发2021-09-28 3274

-

现代芯片发展的方向是什么?2023-05-10 2196

-

苹果15芯片是多少纳米?苹果15芯片几纳米的?2023-09-13 18547

-

苹果15芯片几纳米工艺 苹果15芯片是什么型号2023-10-08 9594

全部0条评论

快来发表一下你的评论吧 !