LDPC在SSD中的纠错流程详解

描述

NAND会出错

纠错能力是一个SSD质量的重要指标。最开始的NAND 每个存储单元只放一个bit,叫SLC,后来又有了MLC,现在的主流的是TLC。存储密度不断增加的同时,器件尺寸变小,存储单元电气耦合性变得很复杂。比如氧化层变得很薄,比如读取单个bit需要的读电压控制能力更精密等,总的来说,NAND flash更容易出错了,或者说NAND 上的噪声增加了。

RBER (Raw Bit Error Rate)是衡量NAND质量的重要参数。给定RBER,可以比较各种纠错算法的有效性。

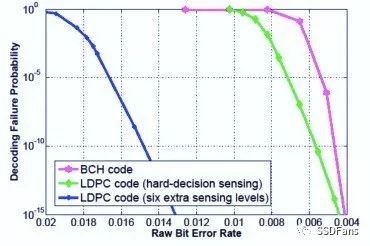

图1 曲线从右到左依次是BCH,LDPC 硬判决算法,LDPC 软判决法,纵轴表示纠错失败的概率,横轴表示RBER

可以看到,LDPC 软判决算法由于有更多的信道信息,相对于BCH 和硬判决LDPC 算法更有优势。所以目前主流的SSD 控制器都采用LDPC 作为纠错算法。

NAND 纠错模型

NAND的基本特性,请参阅第三章。我们存储进NAND的信息通过电子储存起来,读的时候通过探测器件储存的电子多少来恢复数据。

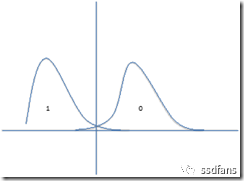

信息0和1在NAND 上的电子分布图(示意图)如下图所示为,以slc 为例。这个分布可以通过大量数据探测出来的。竖直的线,表示此时读取NAND的阈值电压。可见,对于1的概率分布在阈值电压右侧的将会被NAND硬判决成0,从而导致bit翻转。

图2 Slc 两种状态的概率分布示意图,横坐标对应阈值电压。

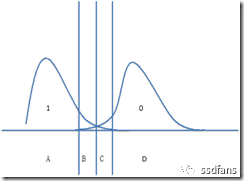

通过调节不同的阈值电压来对NAND 进行多次读取,可以获得额外的信息(得到阈值电压在哪个区间),如下图所示。利用概率论的知识,可以建立统计模型。

图3 多次调整读取电压

假设写入的信息为X,X取值{0,1},其阈值电压为Y, 调节读取电压后将阈值电压分成了4个区间A, B, C,D

已知条件概率密度函数p(Y|X) = f(Y,X) 如上图所示。左右分别为p(Y|X=1) 和 p(Y|X=0) 的曲线。根据之前BP算法章节的介绍,我们感兴趣的是:

P(X|A), P(X|B), P(X|C), 和 P(X|D)。知道这几个概率后,BP 这样的LDPC 的软判决算法就可以工作了。根据前面对条件概率和贝叶斯公式的复习,求解个问题应该不难,交给读者研究。

LDPC纠错流程

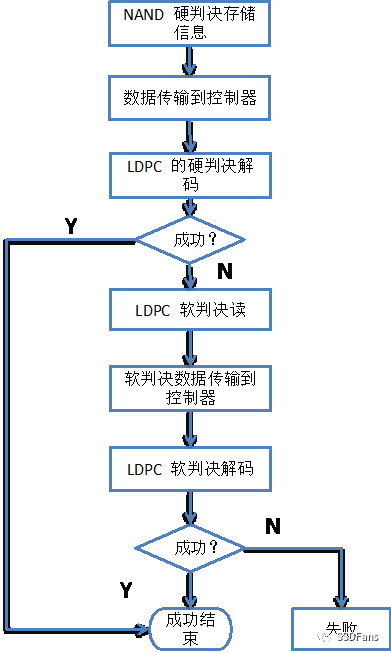

LDPC在SSD中的纠错流程如下图所示,值得注意的是,NAND硬判决,数据传输到控制器,以及硬判决解码这几个过程的速度都很快。软判决要读很多次,传输数据很多次,所以对SSD的性能产生不好的影响。

图4 LDPC 纠错流程

为了提高性能,一种普遍的优化是,把LDPC的软判决的分辨率变成动态可调,这样只有最坏的情况下,才需要最高的分辨率去读。这样在大部分情况下,软判决读和软判决传输数据的时间开销大大变小。

-

一种通用的低成本QC-LDPC码译码结构2010-04-24 1944

-

怎样设计基于CMMB系统的LDPC译码器?2019-08-23 2020

-

LDPC原理与应用2009-07-24 981

-

符合中国数字电视地面广播标准的前向纠错码编码器设计2009-12-13 504

-

规则LDPC码的密度进化方法及其高斯近似2010-01-12 1017

-

LDPC码在无线局域网中的应用分析2011-03-31 881

-

Xilinx宣布推出LDPC纠错IP基础,为云端和数据中心存储市场实现新一代闪存应用2017-02-09 1086

-

LDPC码在基于FH_FSK的AUV水声通信系统中的应用_陈允锋2017-03-19 1217

-

向量子密钥分发的自适应LDPC双码并行机制2017-11-25 1225

-

基于二分图构造LDPC码的校验矩阵算法及性能分析2017-11-30 5995

-

基于卫星通信的多元域LDPC码研究2017-12-29 1419

-

提升SSD寿命的秘密武器——ECC纠错2018-02-08 15405

-

为什么说LDPC码不适合工业存储2020-01-08 1755

-

SSD正面临着新兴应用带来的设计挑战2023-01-11 1118

-

没有强大纠错的工业硬盘,敢叫工业级SSD固态硬盘吗?2025-08-02 1103

全部0条评论

快来发表一下你的评论吧 !