PCIe时钟缓冲器SY7560x系列技术解析与应用指南

描述

Microchip Technology SY75602、SY75603和SY75604 PCIe时钟缓冲器是扇出缓冲器,提供有超低附加抖动:PCIe 5.0的为10fs,PCIe 3.0/4.0的为20fs,12kHz至20MHz频段内为52fs。SY75602、SY75603和SY75604时钟缓冲器可以用于所有PCIe 1/2/3/4/5公共时钟和SRIS应用。这些器件嵌入了低压差稳压器 (LDO),可实现出色的电源噪声抑制。SY75602、SY75603和SY75604时钟缓冲器支持1.8V、2.5V和3.3V电源,电源容差为±10%,超过“PCIe卡机电规范”要求的±9%。

数据手册;*附件:Microchip Technology SY75602、SY75603、SY75604 PCIe时钟缓冲器数据手册.pdf

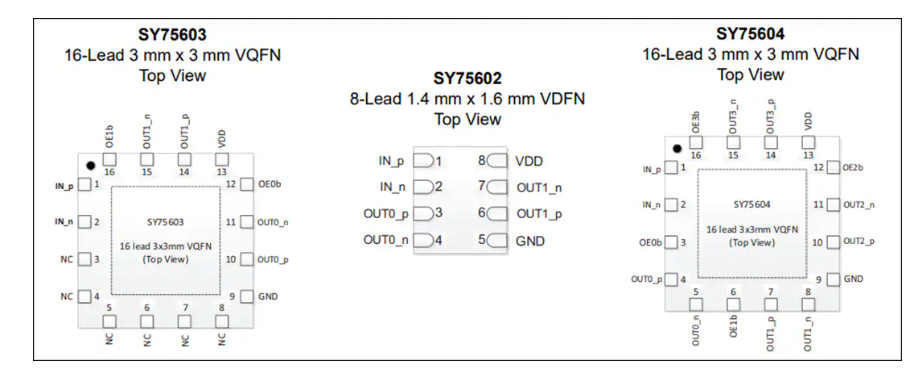

双输出SY75602 PCIe时钟缓冲器采用微型1.4mm x 1.6mm VDFN封装。双输出SY75603和四输出SY75604采用紧凑型3.0mm x 3.0mm VQFN封装。SY75603和SY75604还具有无干扰每输出启用/禁用控制硬件引脚。

Microchip Technology SY7560x PCIe时钟缓冲器具有-40°C至+105°C扩展工作温度范围。

特性

- 两个 (SY75602A/02B/603A/03B) 和四个 (SY75604A/04B) PCIe 1.0、2.0、3.0、4.0和5.0兼容输出。

- 10fs超低附加抖动 (PCIe Gen5)

- 支持高达250MHz的频率

- 对扩频透明

- 支持1.8V±10%、2.5V±10%和3.3V±10%电源

- 输出低功耗HCSL,带嵌入式85Ω (SY75602A/03A/04A) 和100Ω (SY75602B/03B/04B) 端接电阻

- 在SY75603/604上有单独的无干扰输出使能 (OExb) 控制引脚

- 接受直流耦合HCSL输入信号和交流耦合PECL、LVDS和CML

- 扩展温度范围:-40°C至+105°C

- 封装选项

- 1.4mm x 1.6mm x 0.9mm VDFN (SY75602A/02B)

- 3.0mm x 3.0mm x 0.9mm VQFN (SY75603A/03B/604A/04B)

引脚分配

框图

SY75602封装外形

SY75603和SY75604封装外形

PCIe时钟缓冲器SY7560x系列技术解析与应用指南

一、核心特性与行业定位

Microchip SY75602/03/04系列是专为PCIe 1.0至5.0设计的超低附加抖动时钟缓冲器,其核心优势包括:

- 超低抖动性能:10 fs(PCIe 5.0)、20 fs(PCIe 3.0/4.0),满足高速串行总线对时序精度的严苛要求

- 多协议兼容性:支持DC耦合HCSL输入及AC耦合PECL/LVDS/CML信号,适应不同系统架构

- 灵活供电设计:1.8V/2.5V/3.3V ±10%宽电压输入,集成LDO提升电源噪声抑制能力

- 小型化封装:SY75602采用1.4×1.6mm VDFN(业界最小PCIe时钟缓冲器),SY75603/04采用3×3mm VQFN

二、关键技术创新解析

1. 抖动抑制技术

- 相位噪声优化:典型相位噪声曲线显示在100MHz时钟下,12kHz-20MHz带内RMS抖动仅52fs

- 电源噪声隔离:70dB PSNRR(100kHz噪声注入)确保电源波动不影响时钟质量

- 终端集成设计:内置85Ω/100Ω差分终端电阻(A/B版本差异),减少PCB布局阻抗失配

2. 动态控制功能

- 无毛刺输出使能:SY75603/04支持独立OE控制引脚,3.5个时钟周期完成使能/禁用切换(需4个时钟上升沿同步)

- 自适应输入处理:30mV滞回电压防止输入悬空时的随机抖动,支持0-250MHz全频率范围输入

三、典型应用场景设计要点

1. PCIe扩展卡设计

- 布局建议:VQFN封装需注意ePad接地导热,ΨJT=5°C/W(3×3mm封装)

- 信号完整性:差分走线阻抗匹配85Ω/100Ω(对应A/B版本),参考图4-4的嵌入式终端结构

2. 服务器时钟树设计

- 多器件同步:器件间输出偏斜<50ps,建议采用星型拓扑降低时钟分布偏差

- 热管理:θJA=35.7°C/W(无气流),高速场景需增加散热过孔

四、电气参数深度解读

| 关键参数 | SY75602A/03A/04A (85Ω) | SY75602B/03B/04B (100Ω) | PCIe规范要求 |

|---|---|---|---|

| 输出电流消耗 | 4.0mA (典型) | 3.5mA (典型) | - |

| 交叉点电压容差 | ±140mV | ±140mV | <±150mV |

| 使能响应时间 | 3.5时钟周期 | 3.5时钟周期 | - |

| 工作温度范围 | -40°C至+105°C | -40°C至+105°C | 商用级 |

五、设计验证参考

- 测试负载规范(图1-7):

- 15dB@4GHz衰减的差分走线

- 终端配置2pF±5%电容,需使用单端探头测量

- 眼图测试条件:

- 测量窗口:-150mV至+150mV(差分)

- 上升/下降时间要求:1-4V/ns(单调性验证)

六、选型指南

| 型号 | 输出数 | 封装尺寸 | 终端阻抗 | 特色功能 |

|---|---|---|---|---|

| SY75602ATWL | 2 | 1.4×1.6mm VDFN | 85Ω | 超紧凑设计 |

| SY75604BTWL | 4 | 3×3mm VQFN | 100Ω | 全输出独立使能 |

该系列器件已通过PCI-SIG认证,可加速产品合规性测试流程。建议高速设计优先选择B版本(100Ω)以降低反射损耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

9DBL02x2/9DBL04x2/9DBL06x1/9DBL08x1C:PCIe零延迟/扇出缓冲器的卓越之选2025-12-30 86

-

高性能PCIe Gen7 1.8V扇出缓冲器RC191xx:特性、应用与设计指南2025-12-26 1356

-

时钟缓冲器技术选型与设计要点2025-12-16 248

-

Microchip SYA7560系列PCIe时钟缓冲器技术总结2025-10-14 397

-

Texas Instruments CDCDB803用于PCIe®第1代至第5代的8输出时钟缓冲器数据手册2025-09-26 594

-

低附加抖动LVDS缓冲器LMK1D210x技术解析与应用指南2025-09-23 612

-

Diodes公司PCIe 6.0时钟缓冲器介绍2025-04-10 969

-

矽力杰高性能20路PCIe时钟缓冲器2023-12-20 2039

-

什么是时钟缓冲器(Buffer)?时钟缓冲器(Buffer)参数解析2022-10-18 30559

-

使用IDT时钟缓冲器提升应用设计2022-05-05 2698

-

时钟缓冲器选型目录2021-11-19 2136

-

一款九端口PCIe时钟缓冲器2020-08-27 2342

-

业界首家性能和功耗领先的PCI Express Gen 5时钟和缓冲器2019-04-17 5892

-

LMK0033x:最低抖动的PCIe时钟扇形缓冲器2018-06-13 6172

全部0条评论

快来发表一下你的评论吧 !