全加器是什么?全加器和半加器的区别?

电子常识

描述

全加器

英语名称为full-adder,是用门电路实现两个二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位。多个一位全加器进行级联可以得到多位全加器。常用二进制四位全加器74LS283。

全加器是能够计算低位进位的二进制加法电路。与半加器相比,全加器不只考虑本位计算结果是否有进位,也考虑上一位对本位的进位,可以把多个一位全加器级联后做成多位全加器.

全加器和半加器的区别

加法器是产生数的和的装置.加数和被加数为输入,和数与进位为输出的装置为半加器.若加数、被加数与低位的进位数为输入,而和数与进位为输出则为全加器.

半加器:半加器的电路图半加器有两个二进制的输入,其将输入的值相加,并输出结果到和(Sum)和进制(Carry).半加器虽能产生进制值,但半加器本身并不能处理进制值.

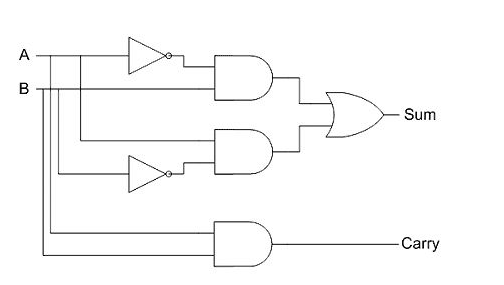

全加器:全加器三个二进制的输入,其中一个是进制值的输入,所以全加器可以处理进制值.全加器可以用两个半加器组合而成.

半加器:HA 有两个代表数字(A0,B0)有两个输出端,用于输出和S0及进位C1(只考虑两个1位二进制数A和B相加,不考虑低进位来的进位数相加称为半加。)

全加器:FA,有三个输入端,以输入Ai、Bi、Ci,有两个输出端Si,Ci+1(除了两个1位二进制数,还与低位向本位的进数相加称为全加器。)

半加器能产生进位但是不能处理进位,而全加器可以。它们本质上是一样的,只是全加器比半加器多一个接收进位的输入端,这样全加器每一次都要考虑来自低位的进位,而半加器不用考虑,直接把两个二进制数相加就行。

半加器没有接收进位的输入端,全加器有进位输入端,在将两个多位二进制数相加时,除了最低位外,每一位都要考虑来自低位的进位,半加器则不用考虑,只需要考虑两个输入端相加即可。

-

半加器和全加器的功能特点2024-10-18 5605

-

层次化设计构成全加器2023-05-22 2499

-

基于FPGA层次化设计构成全加器2023-05-14 2603

-

什么是8位全加器和8为带超前进位的全加器?2022-02-09 1575

-

FPGA入门——1位全加器设计 精选资料分享2021-07-26 1544

-

全加器的真值表2021-06-29 63006

-

全加器逻辑表达式_全加器的逻辑功能2020-04-23 134502

-

半加器和全加器的原理及区别(结构和功能)2018-07-25 345481

-

全加器,全加器是什么意思2010-03-08 87080

-

全加器2009-04-07 10174

全部0条评论

快来发表一下你的评论吧 !