全加器逻辑电路图分析

电子说

描述

全加器

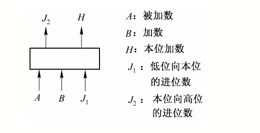

全加器是一个能够完成一位(二进制)数相加的部件。我们先来看一下两个二进制数的加法运算是怎样进行的。两数相加,先从低开始,把对应位上的数相加,还可能有由较低位来的进位数。因此,除第一位外,每一位上参加运算的是三个数。所以,全加器应有三个输入端,分别对应着被加数、加数和较低位来的进位数。相加的结果,得到本位的和数以及向较高位的进位数,因此,全加器有两个输出端,一个对应着本位和数,另一个对应着向较高位的进位数。于是,全加器的逻辑框图如图19-18所示。

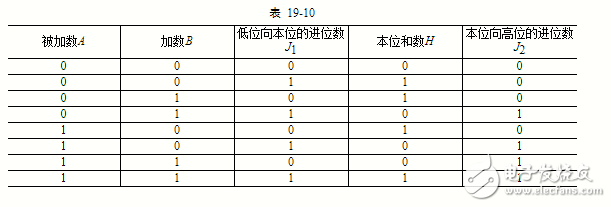

显然,本位和数H、本位向较高位的进位数J2,都是被加数A、加数B和由较低位来的进位数J1的函数,列表如表19-10所示。由此可得H和J2的逻辑表达式的析取范式为:

H = (A'∧B'∧J1)∨(A'∧B∧J'1)∨(A∧B'∧J'1)∨(A∧B∧J1)

J2 = (A'∧B∧J1)∨(A∧B'∧J1)∨(A∧B∧J'1)∨(A∧B∧J1)

化简后得

H = (((A'∧B)∨(A∧B'))∧J'1)∨(((A'∨B)∧(A∨B')))∧J1)

= (H1∧J'1)∨(H'1∧J1)

其中

H1 = (A'∧B)∨(A∧B')

而

J2 = (A∧B)∨(H1∧J1)

为了用与门和非门电路构成全加器,将上式改写为

H1 = ((A'∧B)'∧(A∧B')')'

H = ((H1∧J'1)'∧(H'1∧J1)')'

J2 = ((A∧B)'∧(H1∧J1)')'

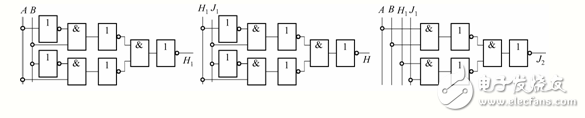

实现H1的开关电路如图19-19a所示;实现H的开关电路如图19-19b所示,它和图19-19a具有相同的结构,只是输入的变量不同;实现J2的开关电路如图19-19c所示。

图 19-19

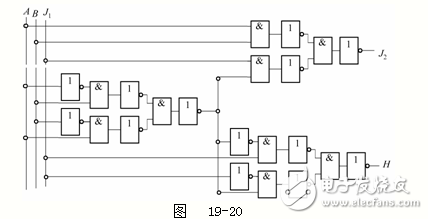

把图19-19a、b、c所示的电路连接在一起,就构成一个完整的一位全加器电路,如图19-20所示。

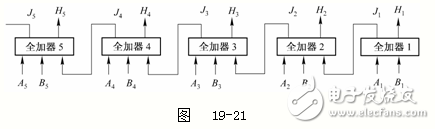

如果是两个多位数相加,就要把多个全加器连接起来,构成加法器,图19-21是五位加法器的框图。

-

组合逻辑电路分析和设计方法2023-08-16 11127

-

组合逻辑电路的分析和设计2023-03-06 5763

-

MGLS-12864的逻辑电路图2012-07-23 2685

-

组合逻辑电路的设计实验2009-10-24 4254

-

组合逻辑电路实验分析2009-07-15 2227

-

6N137逻辑电路图2009-07-01 2839

-

逻辑电路电源的过压保护电路图2009-04-07 1245

-

光触发逻辑电路图2009-04-02 996

-

组合逻辑电路实验2009-03-20 3290

-

光电逻辑电路图2008-12-22 1026

-

集成逻辑电路、组合逻辑电路2008-12-11 5869

-

逻辑门及组合逻辑电路实验2008-09-25 4733

全部0条评论

快来发表一下你的评论吧 !