FPGA中数据延迟方案介绍

描述

一.非阻塞赋值延时打拍

always@ (posedge clk) begind1 <= d;d2 <= d1; ....... dout <= dn;end

本质上就是对数据进行多级寄存器缓存,延迟时间以clk的一个周期为单位,消耗的就是寄存器。比较适合延迟固定周期以及延迟周期比较短的情况。

缺点:延迟时间不方便控制,不适合延迟时间比较长的情况。

二、移位寄存器延时

reg [data_width*delay_width-1:00] data_r=0;always @ (posedge clk)begin data_r <= {data_r[data_width*(delay_width-1)-1:0],data_in};endassign data_out=data_r[camera_trig_delay_time];

这种方法利用的是移位寄存器的方法,用的是SLICEM资源。SLICEM可以在不使用触发器的条件下配置为32位移位寄存器(注意:只能左移)。这样,每个LUT可以将串行数据延迟1到32个时钟周期。移位输入D(LUT DI1脚)和移位输出Q31(LUT MC31脚)可以进行级联,以形成更大的移位寄存器,达到更大的延迟效果。这种方法延迟的时间可配置性也比较高。

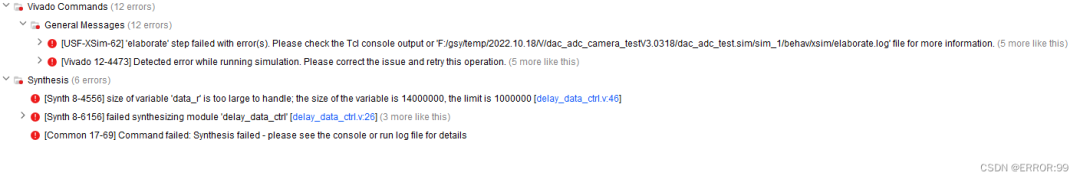

缺点:占用的资源比较多。尤其当延迟的数量级较大时,拼接的位移寄器是有个数限制的,如下图则是当延迟时间设置比较久的时候vivado报错的截图。

三、计数器实现任意周期延时

这种资源消耗率较低,延迟周期也比较灵活。

parameter delay_per = 8'h4;//延时周期数reg flag;reg [7:0] delay_count; always @(posedge clk ornegedge rst_n) beginif(!rst_n) begin flag <= 0; endelseif(in1)begin flag <= 1; endelseif(delay_count == delay_per)begin flag <= 0; endendalways @(posedge clk ornegedge rst_n) beginif(!rst_n)begin delay_count <= 0; out1 <= 0; endelseif(delay_count == delay_per && flag == 1'b1)begin delay_count <= 0; out1 <= 1; endelseif(flag == 1'b1)begin delay_count <= delay_count + 1'b1; out1 <= 0; endelsebegin delay_count <= 0; out1 <= 0; endend

这种实现方式比较多,这里摘录了网上的代码。这种方法下,延迟的时间必须小于信号的间隔。因为如果延迟时间大于了信号间隔,就会丢掉信号。

缺点:.延迟时间必须小于信号间隔。

四、大容量存储

对于比较大时间的延迟,可以用RAM或者fifo或者DDR这种存储介质进行缓存延迟

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Xilinx FPGA输入延迟原语介绍2026-03-11 2039

-

集成电源解决方案-Altera FPGA应用介绍2023-11-28 580

-

FPGA学习-IO延迟的约束方法2023-01-01 4996

-

PCIE高速传输解决方案FPGA技术XILINX官方XDMA驱动2021-05-19 6893

-

Xilinx Vivado I/O延迟约束介绍2020-11-29 6509

-

一种基于FPGA和DSP的高速数据采集设计方案介绍2019-07-05 2598

-

如何在FPGA中实现选定信号的准确延迟2019-05-28 4457

-

在FPGA高速AD采集设计中的PCB布线解决方案浅析2019-03-07 7514

-

FPGA使用ddio方式送数据给AD9957发现FPGA送数据的延迟较大2018-10-17 4188

-

使用通信中的无线模块的数据延迟2018-08-10 1294

-

无线模块通信中的数据延迟2018-08-09 5439

-

通过高性能FPGA搭建的客制硬体,更大幅缩短往返交易延迟2018-08-03 2663

-

低成本FPGA中实现动态相位调整方案2018-02-16 11649

-

FPGA的多路可控脉冲延迟系统设计2009-03-29 3062

全部0条评论

快来发表一下你的评论吧 !