STDRIVEG210半桥栅极驱动器技术解析与应用指南

描述

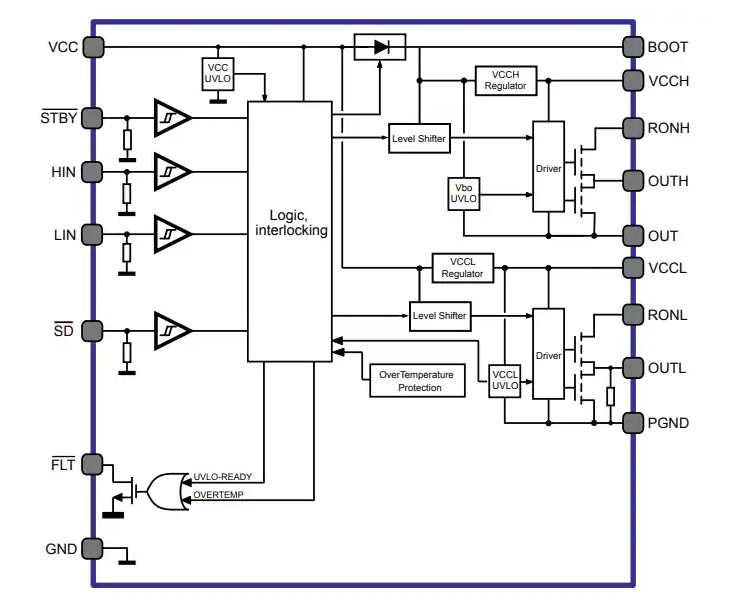

STMicroelectronics STDRIVEG210半桥栅极驱动器设计用于N 沟道增强模式GaN,高侧驱动器部分可承受高达220V电压轨。这些驱动器具有大电流能力、短传播延迟和出色的延迟匹配,并集成了低压差稳压器 (LDO)。这使得它们非常适合驱动高速GaN。STDRIVEG210半桥栅极驱动器具有针对快速启动和低功耗软开关应用量身定制的电源UVLO功能。高侧稳压器的特点是唤醒时间非常短,可以在间歇操作(突发模式)期间最大限度地提高应用效率。这些驱动器提供了扩展的输入引脚范围,便于与控制器连接。待机引脚可在非活动期或突发模式下降低功耗。应用包括DC/DC、AC/DC、谐振转换器、同步整流、UPS、适配器、LED灯和USB-C。

数据手册:*附件:STMicroelectronics STDRIVEG210半桥栅极驱动器数据手册.pdf

特性

- 高压轨高达220V

- ±200 V/ns dV/dt瞬态抗扰度

- 驱动器具有独立的灌电流和源路径,以实现最佳驱动:

- 2.4A和1.2Ω灌电流

- 1.0A和3.7Ω源电流

- 300ns超快高侧启动时间

- 传播延迟45ns,最小输出脉冲15ns

- 高 (>1MHz) 切换频率

- 内置自举二极管

- 完全支持GaN硬开关操作

- V

CC、VBO和VLS上的UVLO功能 - 分开的逻辑输入和关闭引脚

- 过温和UVLO报告故障引脚

- 低功耗模式待机功能

- 分开的PGND用于开尔文源驱动和电流分流兼容性

- 3.3 V至20 V兼容输入,具有迟滞和下拉功能

方框图

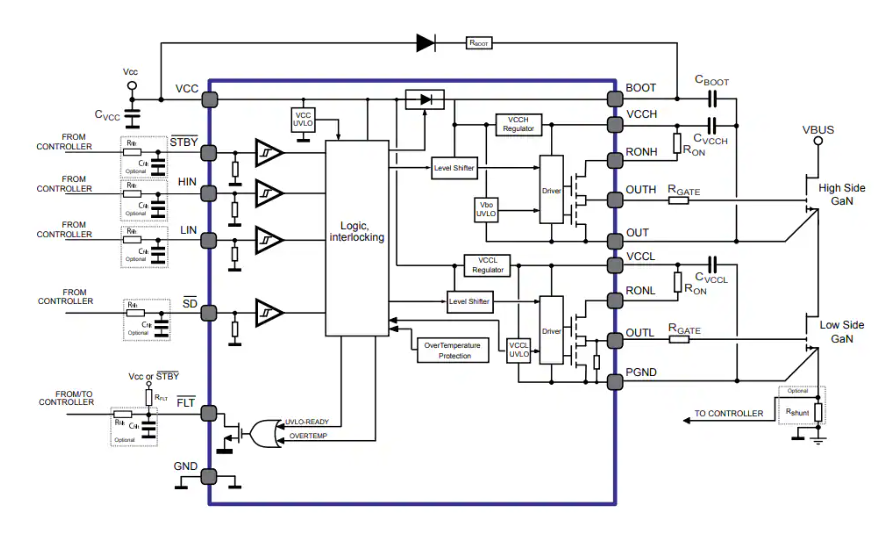

典型应用原理图

STDRIVEG210半桥栅极驱动器技术解析与应用指南

一、核心特性与典型应用场景

STDRIVEG210是STMicroelectronics推出的220V高速半桥栅极驱动器,专为增强型GaN功率开关设计,具有以下突出特性:

- 高压支持:最高220V工作电压,±200V/ns的dV/dt瞬态抗扰度。

- 驱动能力优化:分离的灌电流(2.4A)和拉电流(1.0A)路径,源阻抗分别为3.7Ω(拉电流)和1.2Ω(灌电流)。

- 超快响应:高侧启动时间仅300ns,传播延迟45ns,最小输出脉冲15ns,支持>1MHz开关频率。

- 集成保护功能:VCC、VBO、VLS欠压锁定(UVLO),过温保护和故障引脚(FLT)报告。

- 节能设计:待机模式功耗极低,兼容3.3V至20V逻辑输入。

典型应用:

- DC/DC、AC/DC谐振变换器

- 电池充电器与适配器

- 太阳能微逆变器与MPPT优化器

- LED驱动与USB-C电源

二、关键电路设计与功能解析

2.1 引脚配置与功能

- VCC(引脚1) :逻辑供电(9.2-18V),需外接100nF去耦电容。

- STBY(引脚2) :待机控制(低电平激活),内置下拉电阻。

- OUTH/OUTL(引脚15/13) :高低侧驱动输出,需通过RGATE电阻连接GaN栅极。

- BOOT(引脚18) :高侧浮动供电,集成自举二极管,需外接47nF-3.3μF电容。

2.2 自举电路设计

- 集成二极管:同步低侧导通,减少VCC至VBO压降,但需外接快速二极管(如STTH1R06)以实现最优启动性能。

- 布局建议:CBOOT电容负端应靠近OUT引脚,自举电阻RBOOT≥2.2Ω以抑制EMI。

2.3 栅极电阻配置

- 单输出架构:通过RONx(引脚16/11)调节导通阻抗,RGATE调节关断阻抗。例如:

- 关断阻抗:RGATE ≈ ROFF(传统设计)

- 导通阻抗:RON ≈ RON(传统设计) - RGATE

- 布局优化:0603封装的RGATE电阻需贴近GaN栅极,减少环路电感。

三、保护机制与电源管理

3.1 UVLO与故障处理

- VCC UVLO:开启阈值8.5V(典型值),关闭阈值8.0V,滞后0.5V。

- VLS UVLO:低侧驱动UVLO阈值4.8V(开启)/4.65V(关闭)。

- FLT引脚:开漏输出,指示UVLO、过温或待机状态,需外接上拉电阻。

3.2 热管理

- 过温保护:触发温度175°C(典型值),滞后20°C。

- 散热设计:QFN 4x5mm封装,建议通过GND引脚铜箔散热,RθJA为85°C/W(4层板)。

四、PCB布局与噪声抑制

- 关键回路最小化:

- 栅极环路:OUTx→RGATE→GaN栅极→Kelvin源极→PGND/OUT。

- 电源去耦:VCCL、VCCH电容(47nF X7R)需贴近引脚。

- 噪声抑制措施:

- 星型接地:PGND与信号GND单点连接。

- 高频电容:在高压总线与功率地间就近放置陶瓷电容(如1μF/50V)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

SM74104高压半桥栅极驱动器的技术解析与应用指南2026-01-11 719

-

LM2105:高性能半桥驱动器的技术解析与应用指南2026-01-07 647

-

UCC2773x:高性能半桥栅极驱动器的技术解析与应用指南2026-01-06 654

-

意法半导体半桥GaN栅极驱动器简化电源管理设计2025-10-29 924

-

STDRIVEG60015演示板技术解析:650V E模式GaN半桥驱动设计指南2025-10-24 889

-

STDRIVEG611栅极驱动器评估板技术解析与应用指南2025-10-17 806

-

STDRIVEG611半桥栅极驱动器技术解析与应用指南2025-10-16 1166

-

STDRIVEG211半桥栅极驱动器深度解析与设计指南2025-10-15 960

-

LM2105半桥栅极驱动器技术解析与应用指南2025-08-21 1239

-

LM2005 107V半桥栅极驱动器技术解析与应用指南2025-08-08 1537

-

ST 意法半导体 STDRIVEG611QTR 用于 GaN 功率开关的高压和高速半桥栅极驱动器2025-02-12 660

-

STDRIVEG600 GaN半桥驱动器2023-09-05 1019

全部0条评论

快来发表一下你的评论吧 !