如何为嵌入式视觉开发者减负?

描述

试想一下,在一个通常性能受限的嵌入式架构中去跑复杂的视觉处理算法,还要平衡功耗、尺寸、成本、开发周期等因素,确实不容易。如果你面对的是工业或汽车这种对实时性和可靠性要求较高的场合,视觉处理要又快又准,容不得半点闪失。而且现在都人工智能(AI)时代了来了,机器学习是不是也应该支持一下?所以,嵌入式视觉开发者头上总会有个大大的“鸭梨”。

不过,这个世界上总是会有人在琢磨“如何将复杂的事情变得简单”。在嵌入式视觉开发这件事上,如何为开发者“减负”,已经有了许多好方案摆在我们面前了。

我们先从硬件上来看。单一处理器架构当然更容易上手,但是开发者总免不了要在性能和灵活性、可扩展性上做折中。直到赛灵思推出了Zynq这种全新架构的FPGA SoC器件,大家才眼前一亮。Zynq是一种异构处理器,内部既包含嵌入式处理器(PS),也有可编程逻辑电路(PL)。

嵌入式视觉开发者可以根据需要将计算任务在两个系统间进行分配,十分灵活。通常可以将高性能的视觉处理功能放在PL上做加速,这自然比用通用CPU处理更高效。由于PL是硬件可编程的,所以开发者可以复用成熟的IP,也可以根据算法编写自己的定制化IP,实现与众不同视觉处理效果。

为了更好地支持高性能视觉处理的应用开发,赛灵思特别推出了Zynq Ultrascale+ MPSoC,与上一代Zynq相比,该器件提升了性能,同时为了应对实时性视觉处理做了专门的优化。我们看看Zynq Ultrascale+ MPSoC的核心资源配置,就明白了:

四个ARM Cortex-A53 CPU,算力不俗,可以支持功能复杂的OS,如Linux。

两个ARM Cortex R5F实时处理器(RPU),可工作在锁步和独立运行模式,锁步模式可用于安全性要求严苛的场合。

一个Mali-400图形处理器,用于2D/3D图形显示,可提供高质量的视频显示输出。

不夸张地说,Zynq Ultrascale+ MPSoC就是一颗“为嵌入式视觉”而生的器件,丰富的硬件资源能够让开发者达到事半功倍的目的。

图1,Zynq Ultrascale+ MPSoC将嵌入式视觉作为其主攻应用市场(图片来源:赛灵思)

硬件架构能够满足要求了,但这并不意味着就能玩转嵌入式视频开发。以往在开发者心中,想和FPGA打交道,要学会要用专门的硬件描述语言写HDL代码,这并不容易,更何况现在面对的Zynq Ultrascale+ MPSoC是一个更复杂的FPGA+CPU的“异构”系统。

这个顾虑,赛灵思早已经料到了,所以他们在推出Zynq之后,也开发出了一个“软件定义”的工具套件,让FPGA SoC的开发变得更容易,这就是SDSoC。

对于SDSoC比较通俗的理解就是,它将FPGA SoC所需的开发工具和资源库整合在一个统一的开发环境中,让以往需要由系统架构、硬件设计、软件开发等不同团队协调合作、反复迭代才能完成的复杂设计开发流程,以更为自动化的方式得以实现,简化了工作,提高了效率。

SDSoC的核心愿景就是:让更多只有很少或根本没有FPGA设计经验的研发人员,无需写一行RTL代码,就可以直接使用高级编程语言编程,体验到可编程硬件的的强大能力,并且可以与通用处理器系统一起协同工作。就嵌入式视觉开发而言,开发者使用SDSoC后,可以将更多的时间和精力从繁复的底层开发工作中解放出来,去考虑算法的优化这类可以给产品带来更多差异化和附加值的高层次、系统级的问题。

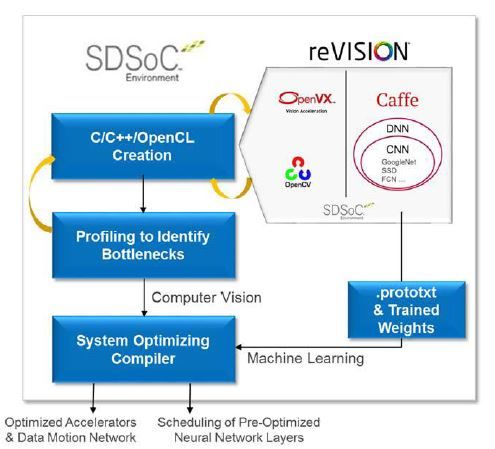

图2,SDSoC典型开发流程(图片来源:赛灵思)

可见,SDSoC的出现让基于Zynq Ultrascale+ MPSoC这类嵌入式视觉硬件平台的开发效率大为提升。但是,你别以为这就大功告成了。市场的发展会不断给你提出新的需求,比如说如果今天你还没有考虑为嵌入式视觉系统加入机器学习功能,明天你的产品可能就OUT了。

想要在设计上“追新”不掉队,传统的视觉处理设计思路就要改变——开发者要从费时费力的自己做HDL编程优化,转向充分利用现有的成熟、经过验证的IP资源,通过软件定义的方式获得所需的视觉加速性能。赛灵思的reVISION堆栈就是一个将实现新思路所需的所有要素整合在一起的系统环境。

reVISION堆栈包括丰富的平台、算法和应用开发资源,支持最流行的神经网络,如AlexNet、GoogLeNet、SqueezeNet、SSD和FCN等。此外,该堆栈还提供库元素,包括预定义和优化的CNN网络层实现,这是构建定制神经网络(DNN(深度神经网络)/CNN(卷积神经网络))所必需的。

机器学习元素还配合一系列丰富的支持加速功能的OpenCV功能,满足计算机视觉处理要求。针对应用层开发,赛灵思支持工业级框架,包括面向机器学习的Caffe和面向计算机视觉的OpenVX。reVISION堆栈还包括了赛灵思和第三方提供的开发平台以及各类传感器。

用reVISION的开发流程也很简单,在SDSoC开发环境中,软件工程师和系统工程师可以 reVISION硬件平台为目标,并调用大量的加速就绪型计算机视觉库进行开发,快速构建应用。

按照赛灵思的说法,采用传统的RTL流程进行视觉处理开发,赛灵思的FPGA可以帮助用户完成20%的工作,用户需要解决剩余的80%问题;而基于reVISION的开发则可以帮助用户完成80%的工作量,用户只需做剩下的20%即可,效率的提升十分显著。

图3,采用reVISION的软件定义设计流程(图片来源:赛灵思)

总之,一个为视频处理专门优化的硬件架构Zynq Ultrascale+ MPSoC、一个简单易用低门槛儿的SDSoC开发环境、一个资源丰富的reVISION堆栈,构成了嵌入式视觉开发“三件套”,它们可以帮助开发者大幅减少工作负荷、提升设计效率。一旦拥有,做个嵌入式视觉开发者,是不是件幸福的事儿?

图4,安富利推出的MicroZed嵌入式视觉开发套件,结合reVISION可以为开发者提供全面的嵌入式视觉设计开发支持

-

给初学嵌入式开发者的建议2015-10-15 0

-

如何为嵌入式处理设计选择合适的开发工具?2021-04-29 0

-

2012新能源、工业与嵌入式应用方案展暨开发者论坛圆满落幕2012-08-23 482

-

嵌入式视觉技术--潜力巨大,有待开发2014-08-20 2757

-

玩转Xilinx嵌入式视觉开发者专区 让视觉系统开发更加简单2017-11-10 1076

-

如何成为一名合格的嵌入式开发者?现在了解还不晚!2018-04-27 3799

-

Xilinx嵌入式视觉开发者专区的详细介绍2018-11-29 2304

-

嵌入式视觉的最新趋势讨论2018-11-22 3055

-

英伟达发布嵌入式电脑Jetson Nano,帮助机器人开发者引入AI计算能力2019-03-21 6031

-

嵌入式开发者必备的基础硬件知识2019-06-18 3094

-

赛灵思公司宣布推出嵌入式视觉开发者专区2019-08-01 1857

-

AI开发平台如何帮助嵌入式开发者加速应用产品化落地2020-07-30 965

-

开发者如何为其特定嵌入式AI项目选择最佳的AI芯片2022-12-23 1291

-

浅析MATLAB和Simulink嵌入式视觉应用2021-11-22 4127

-

AI来袭!嵌入式开发者该如何应对转型?2025-03-04 523

全部0条评论

快来发表一下你的评论吧 !