以FPGA为核心控制单元的多通道综合测试系统设计详解

可编程逻辑

描述

1 背景知识

采用基于FPGA的方式进行系统设计,具备运行传输速度快、并行处理内部程序、有大量开发好的IP核、引脚众多、设计灵活等优点。

针对被测样机的功能模式和受控电路模块众多,对控制器I/O引脚资源要求较高,所以本系统设计需采用FPGA作为核心控制单元,以实现对被测样机的管理控制,和实现数据采集、通道切换、信号控制、数据通信等功能。

本设计中选用了Spartan6系列的XC6SLX150-2FG484C这款FPGA芯片,其内部资源丰富,用户可用IO数达168个,满足该系统的设计需求。

2 系统设计

2.1 总体方案

被测样机需对8个被测设备进行循环测量与控制,并对测量数据进行记录判读、存储转发,使用FPGA作为核心控制单元进行总体方案设计,得到本系统的FPGA控制结构框图如下图1所示。需实现的主要功能有,通道切换控制、信号采集控制、控制信号生成、以太网数据通信等。

图 1 系统FPGA控制结构框图

2.2 总体设计

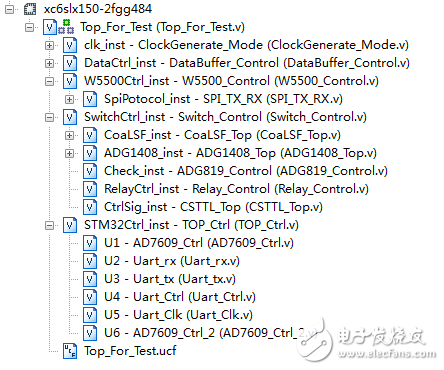

本系统采用Verilog语言进行程序设计,得到如下图2所示的程序设计结构层次图。

其中,顶层模块将各层综合、控制数据的交换等功能。顶层下面包含五大子模块:

1)时钟模块,用于时钟生成;

2)数据控制模块,用于控制和缓存数据;

3)W5500控制模块,实现TCP/IP协议与PC端进行数据传输;

4)开关控制模块,根据PC端命令实现对被测样机的控制;

5)STM32控制模块,实现FPGA与AD采集、串口通信等的交互和控制。

图 2 FPGA程序设计结构层次图

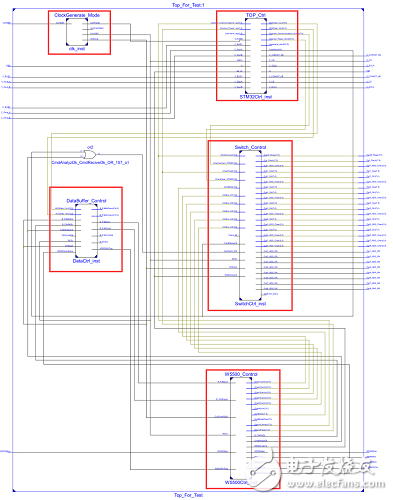

综合顶层模块得到如下如3所示的RTL原理图,图中5个红框对应上述五大模块。

图 3 系统顶层综合RTL原理图

2.3 子模块设计

2.3.1 数据控制模块

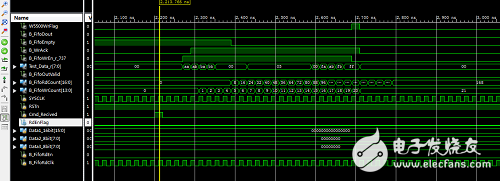

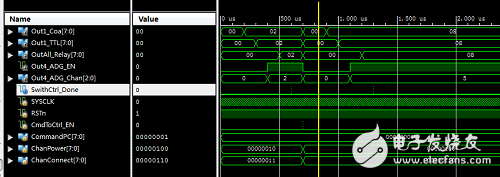

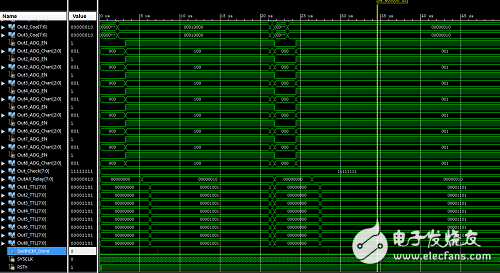

数据控制模块主要完成对各个模块数据、命令的缓存、交互功能,对其进行仿真测试,得到仿真结果图如下图4所示。

图 4 数据控制模块的仿真图

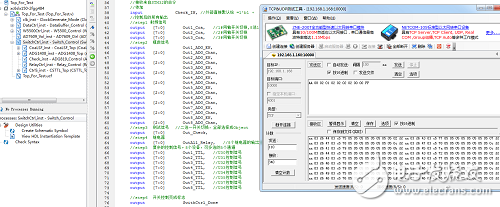

对应的实际环境测试结果如下图5所示,实现了灵活的数据处理功能。

图 5 数据控制模块实物测试图

2.3.2 开关控制模块

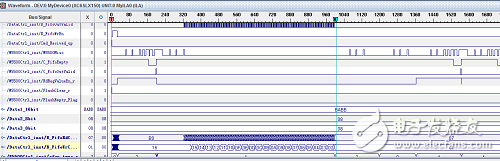

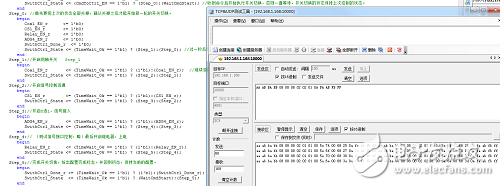

被测样机的切换开关数量众多,且有先后顺序,结合功能和时序要求,设计实现了如下图6的仿真结果。

图 6 开关控制模块仿真结果图

结合W5500控制模块,对开关切换模块进行实物测试,得到如下图7所示结果。在此测试中,回传的数据正确解析了发送数据的命令,并验证了对被测样机的开关切换、通道选择等功能。

图 7 开关控制模块实物测试结果图

2.3.3 STM32控制模块

此模块主要实现了AD采集控制,和FPGA与STM32功能的交互,在此对AD采集与其他模块的控制进行仿真和测试,得到如下图8所示的AD采集控制和交互仿真结果。

图 8 AD采集控制和交互仿真结果

对AD采集的控制,要和其他模块协调配合。如从仿真中可看出,在收到CmdAnalyzOk信号后,AD数据才会更新到B_FIFO中保存,并在收到W5500WrFlag信号后才进行数据传输。

实物测试结果图如下图9所示。实现了根据命令数据采集相应通道的AD值,并通过TCP/IP回传到PC端。

图 9 AD采集控制和交互实际测试图

2.4 系统测试

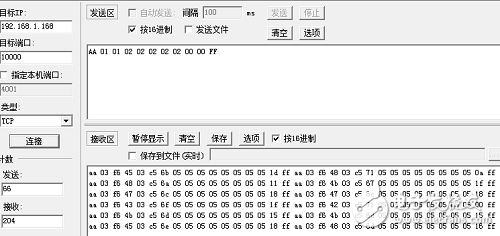

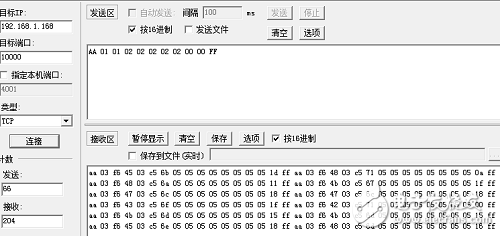

上节已对各个子模块进行了分层设计和实现,现在进行综合设计与测试。先实现全部的开关切换功能,整体仿真结果如下图10所示,实现了所有开关切换和通道选择的功能。

图 10 多通道系统开关切换模块仿真

综合全部模块,对顶层进行实际测试,得到如下图11所示的多通道综合测试系统实物测试结果图。实测结果验证了系统功能实现的正确性,PC端可循环发送命令,FPGA端接收并解析命令进行相应的控制(开关切换、信号采集等),然后将数据回馈到PC端,实现了多通道综合测试系统的设计。

图 11 多通道综合测试系统实物测试结果图

3 结语

本设计以FPGA为核心控制单元,实现了一种多通道综合测试系统,具备开关切换、通道选择、数据采集、TCP/IP协议数据传输等功能,充分利用和体现了FPGA的优势,提供了一种功能完善、性能优良的综合测试系统设计方案。

-

安全综合测试仪2012-07-15 3313

-

基于FPGA的多通道综合测试系统设计2018-08-07 3543

-

一种基于FPGA的多通道频率测量系统的实现方法介绍2019-06-27 1805

-

怎么实现以FPGA为核心器件的并行多通道信号产生模块?2021-04-29 1579

-

物联网设备的控制单元核心2021-11-10 1717

-

基于虚拟仪器技术的综合测试系统2009-09-12 693

-

导弹综合测试系统的程控电源设计2009-07-10 1264

-

基于微控制器的OLED光电性能综合测试系统2011-08-02 2434

-

ADC 综合测试例程2013-09-25 734

-

以FPGA为核心控制单元的空间相机通信系统的设计详解2018-07-19 1292

-

配网物理模拟系统控制单元设计2018-03-09 981

-

以FPGA为核心的多轴控制器设计2018-08-12 2226

-

压力传感器自动综合测试系统控制方法2021-03-19 1006

-

LED驱动电源综合测试系统是什么2022-06-24 1830

-

电磁兼容与电磁环境综合测试系统2025-02-14 905

全部0条评论

快来发表一下你的评论吧 !