基于FPGA和嵌入式以太网W5500的TCP/IP协议栈实现设计

可编程逻辑

描述

1 背景知识

随着网络技术的发展,网络带宽不断增大,系统处理网络协议开销越来越大。以太网具有易于集成、低成本以及传输距离远等特点,越来越多的通信设备需要接入到以太网扩展网络功能以实现远程控制和更加高效的数据传输,基于TCP/IP协议的应用越来越多。FPGA等可编程逻辑器件的快速发展使得以太网协议传输越来越快,随着新技术的不断发展,实现TCP/IP协议栈技术水平越来越高,基于FPGA控制嵌入式以太网协议处理应用越来越普遍。

W5500是一款多功能的全硬件以太网接口芯片,内部集成有10/100M以太网控制器,嵌入了TCP卸载引擎(TCP Offload Engine:TOE),且集成有32K发送缓存区和接收缓存区存储用于数据传输。无需考虑协议内部各层关系,不涉及操作系统,只需要正确配置就可以实现网络连接,接口电路简单、编程灵活方便。

本设计从成本控制和实现周期来考虑,采用了以W5500芯片作为TCP/IP协议栈进行传输系统的设计和实现。

2 系统设计

2.1 TOE技术

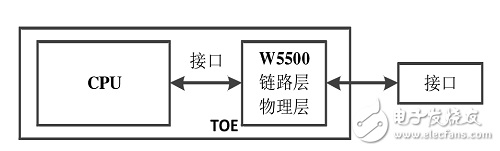

采用TOE技术,即以太网卸载引擎技术,其实现方式是将TCP协议数据包从主机CPU转移到包含TOE功能的网卡,让TOE网卡处理TCP协议数据量,从而提高服务器性能。TOE方式不需进行软件协议栈移植,开发周期缩短,CPU负担降低,稳定性能提高。其处理方式框图如下图1所示。

图 1 TOE方式进行TCP/IP协议栈处理

2.2 W5500以太网控制器

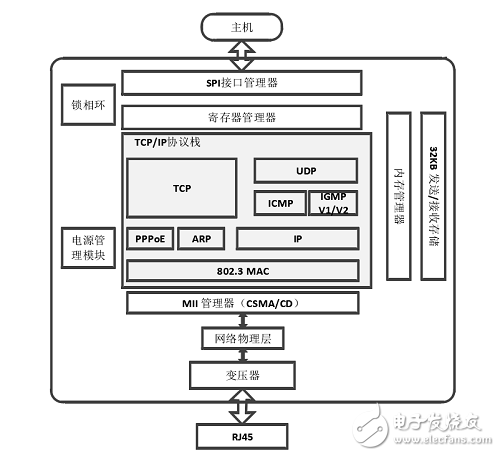

W5500芯片主要通过Socket编程进行协议通信,共有8个可供使用,采用SPI传输协议进行各个寄存器的参数配置,最高数据传输速率可达80MHz。W5500的内部功能框图,如下图2所示。

图 2 W5500的内部功能方框图

2.3 系统程序设计

本设计中FPGA选用Xilinx公司的Spartan6系列的XC6SLX150-2FG484C芯片。这款高性能核心板,具有高速,高带宽,高容量等特点。该核心板硬件实物图如下图3所示。

图 3 核心板硬件实物图

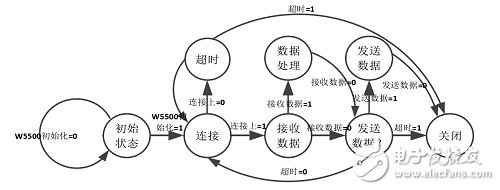

通过设计FPGA程序控制W5500作为服务器模式,等待上位机连接,经三次连接握手成功后,便可进行TCP/IP协议的数据传输。TCP协议通信状态机如图4所示。

图 4 TCP状态机的FPGA实现

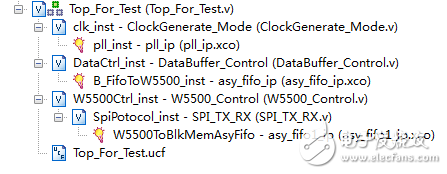

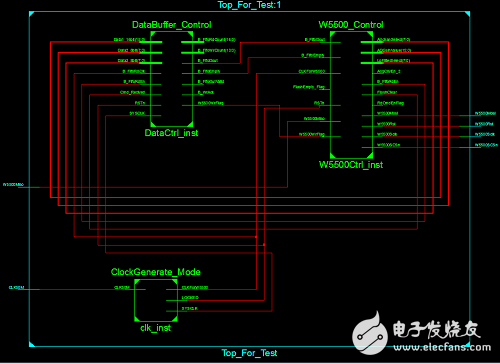

采用模块化、自顶向下的方式进行FPGA程序设计,即顶层Top模块作为总控部分,下一层分为时钟生成、数据控制和W5500控制三大模块,即如下图5所示的Verilog程序工程结构图。其中,数据控制模块主要处理、缓存与W5500模块的接收和发送的数据;W5500控制模块采用SPI方式实现FPGA对W5500芯片寄存器的控制。

图 5 W5500的程序设计结构图

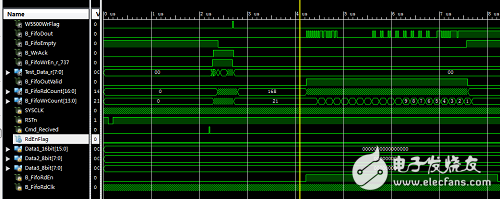

对设计的Verilog程序进行仿真测试,得到如下图6所示的结果。可见,通过W5500模块的数据接收和发送功能均实现。

图 6 W5500模块功能仿真验证图

得到的顶层综RTL原理图如下图7所示。

图 7 W5500模块顶层综合RTL图

2.4 系统测试

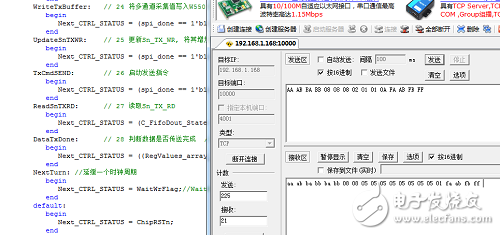

本系统的设计,将下位机(FPGA和W5500)作为服务器,上位机采用测试软件“TCP&UDP测试工具”作为客户端。

将程序配置到FPGA中,首先开启下位机的服务器模式,等待客户端的连接。然后打来测试软件,设置好要连接的IP地址(即服务器IP)和端口号,建立客户端并连接。连接成功后,便开始TCP/IP协议传输测试,通过发送对应的命令数据,服务器接收到命令后,进行数据解析处理和控制,并将结果数据发送回客服端(PC端)。

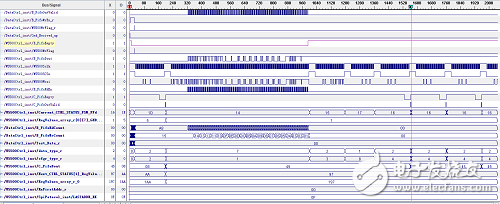

在程序设计过程中,使用开发软件ISE中的ChipScope功能,可以清晰地观测各个信号的变化情况,以测试程序设计的正确性,及便于找出问题。设计完成的ChipScope在线抓数据结果如下图8所示,可实时观测数据与命令的关系和变化情况。

图 8 W5500数据抓取综合测试结果

得到对应的实测结果如下图9所示,验证了以TCP/IP协议方式的数据发送和接收功能的实现。

图 9 W5500功能实测结果图

3 结语

本系统实现了基于FPGA的,采用嵌入式以太网W5500芯片以硬件形式实现的TCP/IP协议栈,提高了CPU的处理效率,并且使得通信速率在很大程度上得到了提高,为以太网数据传输系统的设计提供了一种有效的方式。

-

W5500以太网控制器的驱动设计与实现2022-12-08 7346

-

单片机轻松实现以太网应用 ,全硬件TCP/IP 协议W5500模块资料2014-09-12 9071

-

WIZnet W5500的特点和应用介绍2015-05-05 6684

-

基于FPGA和W5500的以太网传输系统实现2018-08-07 8179

-

以太网W5500模块资料分享!2019-11-01 4902

-

W5500全硬件TCP IP嵌入式以太网控制器中英文版本数据手册免费下载2018-09-21 1499

-

W5500全硬件TCP IP嵌入式以太网控制器的中文数据手册免费下载2019-04-02 1422

-

W5500 TCP IP嵌入式以太网控制器的数据手册免费下载2019-07-08 1466

-

W5500全硬件TCP IP嵌入式以太网控制器芯片的数据手册免费下载2019-08-06 1331

-

高性能以太网芯片W5500的数据手册免费下载2019-08-14 1544

-

W5500以太网控制器的数据手册和使用STM32F40实现W5500检测ping通2019-09-09 2359

-

W5500以太网控制器的数据手册免费下载2020-03-19 1198

-

W5500数据手册免费下载2021-05-18 1358

-

全硬件TCP/IP嵌入式以太网控制器w5500中文资料2022-04-21 2857

-

W5500模块设计原理图解析2023-01-06 1381

全部0条评论

快来发表一下你的评论吧 !