【精选直播】openDACS2025开源EDA与芯片赛宣讲 赛题一:网表评估和优化

描述

openDACS2025开源EDA与芯片赛项

赛题一:网表评估和优化介绍

线上宣讲直播

10月22日(周三) 19:30 精彩开播

| 宣讲信息

报告题目

赛题宣讲:网表评估和优化介绍

报告简介

开放原子大赛是由开放原子开源基金会组织举办的面向开源领域的技术类赛事,目前大赛已成功举办两届共发布100个赛项,吸引8多万人报名参赛,覆盖1000多所院校,发放奖金超过2700万元,形成了一批具有应用价值的技术成果。本届大赛预计发布50个赛项,持续规划1500万元总奖金。

openDACS2025开源EDA与芯片赛项,聚焦集成电路产业的数字设计、处理器设计自动化、生成式芯片设计等领域,对促进产业高质量发展具有重要意义。

宣讲嘉宾

李兴权(鹏城实验室副研究员)、陶思敏(鹏城实验室工程师)

特邀主持

何均宏(openDACS工委会)、穆嘉楠(中科院计算技术研究所)

宣讲时间

2025年10月22日(周三)1930

讲座环节及流程

◈讲座环节:

① 5 分钟主持人进行主题与嘉宾介绍

② 45分钟报告嘉宾讲座环节

③ 15分钟互动问答环节

点击 预约 精彩不容错过!

直播海报

直播海报

诚邀各界嘉宾

线上参会、扫码关注

1. 大赛背景

开放原子大赛是由开放原子开源基金会组织举办的面向开源领域的技术类赛事,目前大赛已成功举办两届共发布100个赛项,吸引8多万人报名参赛,覆盖1000多所院校,发放奖金超过2700万元,形成了一批具有应用价值的技术成果。本届大赛预计发布50个赛项,持续规划1500万元总奖金。openDACS2025开源EDA与芯片赛项,聚焦集成电路产业的数字设计、处理器设计自动化、生成式芯片设计等领域,对促进产业高质量发展具有重要意义。本赛项包含7道赛题,下面是赛题一 网表评估与优化的介绍。

2. 命题单位及赛题Chair

2.1 命题单位

鹏城实验室、中国科学院计算技术研究所

2.2 赛题Chair

李兴权 鹏城实验室副研究员

李兴权,鹏城实验室,副研究员,博士生导师。主要从事EDA、AIEDA相关研究,主导开源EDA项目--iEDA。主持和参与国家自然科学基金项目,福建省优青项目,国家实验室重大专项项目课题,工信部项目课题多项。在TCAD,TC,TVLSI,TODAES,DAC,ICCAD,DATE,ICCD, ASPDAC, ISPD, ISCAS,ISEDA, NIPS等学术期刊和会议发表70余篇论文,申请发明专利20项(PCT专利2项))。2017,2018,2022年3次获得(ICCAD@CAD Contest)全球第一名。2020年获得中国运筹学会运筹应用奖。2023年获得ISEDA最佳论文奖。

陶思敏

鹏城实验室工程师

陶思敏,鹏城实验室工程师,iEDA团队签核分析模块技术组长,主导设计静态时序分析工具(iSTA),功耗分析工具(iPA),电压降分析工具(iIR),所研究工具已集成在iEDA平台,也提供给“一生一芯”做时序功耗评估。发表EDA领域学术论文多篇,和申请中国发明专利多篇。

穆嘉楠

中国科学院计算技术研究所助理研究员

穆嘉楠,中国科学院计算技术研究所助理研究员。2024年在中国科学院计算技术研究所获得博士学位,他的研究聚焦于AI辅助的处理器芯片设计。以第一作者和通讯作者发表 DAC、TCAD、ICML、ICCAD、DATE等领域会议期刊论文十余篇。

3. 赛题背景

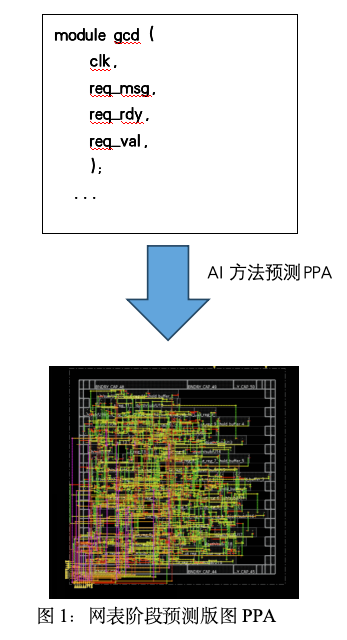

在芯片设计过程中,如果能在设计流程的早期,综合后网表Netlist阶段就对芯片的性能PPA(Performance、Power、Area)进行准确的评估,可以及时的反馈给芯片设计人员调整芯片的架构设计等,进而提升芯片设计效率,缩短芯片设计周期和设计周转时间(Turn Around Time)。在综合出网表后到输出最终的芯片版图,影响芯片签核PPA的主要是芯片物理化设计(布局、时钟树综合、布线)带来的变化。在先进工艺下,随着线宽越来越小,互连线的电阻越来越大,互连线延时、时钟树功耗的占比越来越大,因此物理设计对PPA的影响日益重要。另外在物理化设计阶段,时序功耗优化手段(如插入缓冲器Buffer,改变尺寸Resizer,网表结构优化等)也会影响芯片的面积占用、时序、功耗指标。对于PPA可优化性的考虑也是前期设计比较关注的。近年来人工智能技术爆发式发展,使用神经网络等机器学习方法预估芯片的性能PPA成为了近些年的研究热点,而如何在设计早期综合网表后就考虑芯片物理化设计和其中的时序优化等对PPA的影响是一个重要的挑战性问题。

4. 赛题内容

4.1 赛题描述

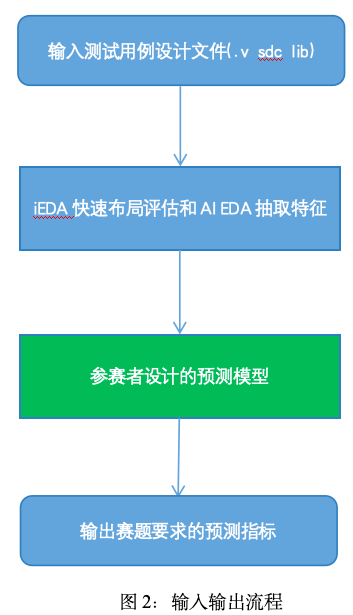

本赛题针对综合后网表,给定开源物理设计工具iEDA(https://github.com/OSCC-Project/iEDA.git),特征提取工具AiEDA(https://github.com/OSCC-Project/AiEDA.git),以及Golden EDA工具输出结果的PPA指标作为标签和预测指标,具体包括:面积(以线密度代替作为指标)、主频、TNS(Total Negative Slack)、总功耗(分为漏电功耗、内部功耗、开关功耗)、Top100的时序路径的Path Delay。在本次比赛中,参赛者使用开源iEDA工具运行到布局阶段不做PlaceOpt优化进行指标评估,AiEDA提供布局阶段各种类型的原始数据的提取方法,AiEDA集成了iEDA作为第三方工具,因此这两个过程可以在AiEDA框架上一步完成。基于iEDA和AiEDA这两个工具,参赛者选用适合的机器学习方法来预测评估数据和最终PPA之间的关系。预测结果关注指标分为精度指标和性能指标,精度关注平均绝对误差MAE,相关性系数R2,性能指标关注模型推理运行时间Run Time,如更高的相关系数、更小的误差和更少的运行时间则得分更高。

4.2 赛题Case

赛题方为参赛队伍提供赛题Case(具体用例数目以数据仓库为准,其中部分用例会作为评分隐藏用例)用于模型训练。下面是对所提供的文件的简单示例(具体以发布为准)。

- 设计文件

- 门级网表Netlist文件(.v文件),

- 时序约束文件(.sdc文件),

- 开源工艺库Skywater130(包含时序功耗信息的.lib文件, 物理单元信息.lef文件)。

如果模型训练有需要,参赛者可以基于iEDA工具内提供的Parser解析这些文件,如果需要的信息没有相应的接口api提供,可以在iEDA中补充接口。

2. iEDA快速布局评估结果和AiEDA提取特征数据

- liEDA输出布局评估结果包括:

- 布局后的输出def;

- 基于布局后的结果给出的时序评估报告(包含Top100的时序路径,可以根据需要设置更多路径输出);

- 功耗评估报告(包含所有Instance的漏电功耗、内部功耗、开关功耗);

- 线密度报告;

- 其他Summary报告和过程Log文件

- lAiEDA抽取的布局阶段特征数据初步包括:

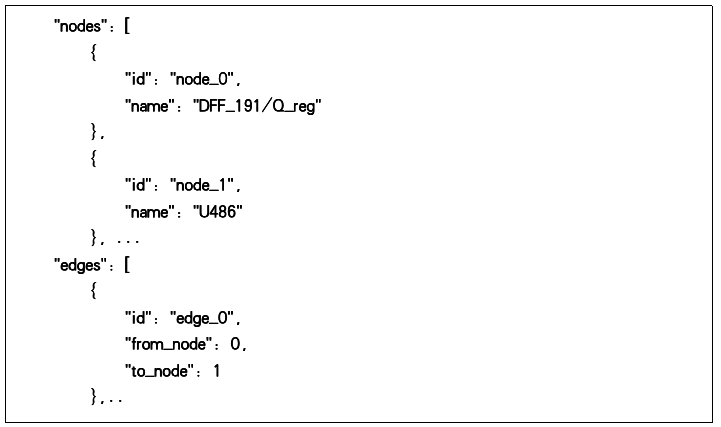

- Graph数据:包括Instance Graph、Wire Graph,从网表Netlist中抽取的Instance或者Pin之间的连接关系,以及点和边上面的特征(详细情况请看数据集)。

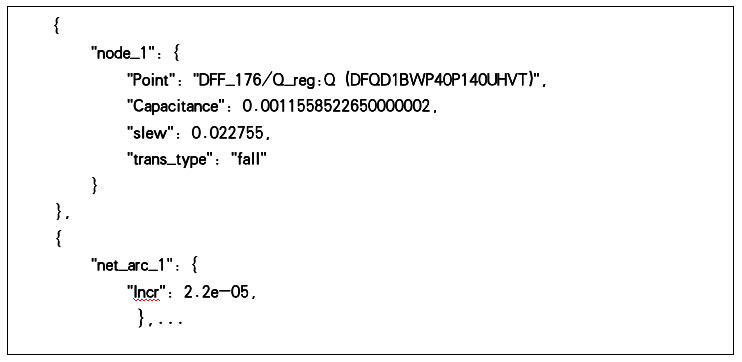

- Path数据:时序路径经过的Pin/Port和时序弧Timing Arc,以及其中特征包括电容C、电阻R、转换时间Slew、时序Arc延时Delay等。

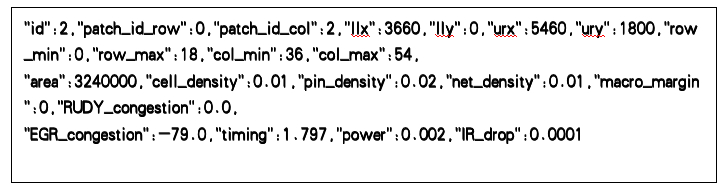

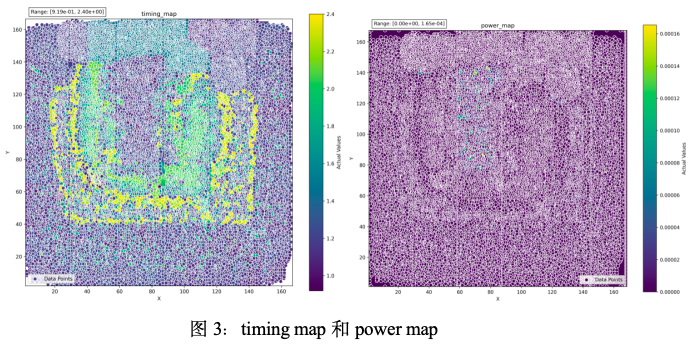

- Patch数据Patch是对版图平面做分割,每个patch是版图的一个区域,如下是id为2的区域,包含区域矩形大小、面积、Cell/Pin/Net密度、拥塞、Timing WNS、Power、IR_drop等特征。可以根据Patch数据构建Timing Map、Power Map、拥塞Map等图片数据。

- 布局单元Instance信息:布局Cell信息、是否能做Resizer和Resize Cell类型等。所有的特征数据会统一以Json文件格式提供,如果参赛者需要更多的特征,可以在AiEDA中补充接口。在模型推理阶段,参赛者也可以修改接口跳过解析Json文件直接从内存中获取特征数据以加速推理时间。

- Graph数据:包括Instance Graph、Wire Graph,从网表Netlist中抽取的Instance或者Pin之间的连接关系,以及点和边上面的特征(详细情况请看数据集)。

3. Golden工具给出的Ground Truth指标标签数据每个用例的标签指标包括线密度、主频、TNS(Total Negative Slack)、漏电功耗、内部功耗、开关功耗、Top100的时序路径的Path Delay 。

4.3 赛题环境

建议参赛队伍的开发环境和运行环境,iEDA运行C++使用兼容C++20的版本,并在Linux系统环境下进行开发。AiEDA推荐使用Python 3.12,Pytorch版本可以根据本地GPU确定。

4.4 赛题资源和提交要求

A. 提交要求:

(一)初赛:参赛队伍提交该赛题的设计文档,要求是PDF文档,在文档中应写清楚技术实现细节,包含以下几点:

- 功能描述

- 整体设计框架

- 功能模块细节设计

- 方案的优势和挑战

(二)决赛:参赛队伍提交训练好的模型和模型代码以及Readme。其中,Readme是对最终提交模型的基本说明,包括推理代码的运行命令等。如果程序运行需要依赖第三方库的,需要一并提供,防止由于版本不同而带来的结果差异。在比赛结束前接受随时提交,出题方会固定周期进行评测并对外发布排名。(三)作品提交通道:官方的AtomGit代码平台:https://atomgit.com/

4.5 赛题评分

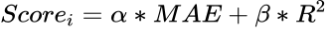

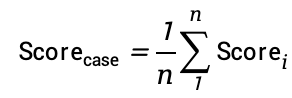

赛题的评分用例分为公开用例和隐藏用例,公开用例可以作为模型训练参赛者测试使用。预测指标7个指标包括线密度、主频、TNS、漏电功耗、内部功耗、开关功耗、Top100的时序路径的Path Delay。各个预测指标得分会累加平均得到一个最终分数结果。对某个Case而言,单一预测指标精度项得分为(权重分别为0.4,0.6): 单一指标第一名得10 分,第二名得9 分,第三名8 分,第四名得7 分,第五名得6 分,第六到八名得4 分,第九到十名得3 分,其余均得1 分。另外考虑单个Case运行时间RunTime得分,在不超时的情况下按照排名得分,如果超时则Run Time为0分。该Case的总体得分为7个预测指标和运行时间Run Time的得分Score_i累加平均,权重相同,每个Case最高满分10分:

单一指标第一名得10 分,第二名得9 分,第三名8 分,第四名得7 分,第五名得6 分,第六到八名得4 分,第九到十名得3 分,其余均得1 分。另外考虑单个Case运行时间RunTime得分,在不超时的情况下按照排名得分,如果超时则Run Time为0分。该Case的总体得分为7个预测指标和运行时间Run Time的得分Score_i累加平均,权重相同,每个Case最高满分10分: 而参赛选手的该赛题得分为所有测试用例的分数之和,10个测试用例满分为100分。

而参赛选手的该赛题得分为所有测试用例的分数之和,10个测试用例满分为100分。

4.6 赛事流程

时间 | 事项 |

2025年10月01日 | 报名启动 |

2025年11月15日 | 报名截止 |

2025年11月23日 | 初赛作品提交截止 |

2025年11月30日 | 公布晋级决赛名单 |

2025年12月07日 | 决赛作品提交截止 |

2025年12月下旬 | 线下决赛路演及颁奖仪式 |

4.7 赛题奖金

大赛分为初赛和决赛,均设奖项,总奖金40万元。

(1)初赛:参赛队伍按赛题报名,在规定的时间内提交参赛开源代码、可执行代码、测试数据和相关文档材料,由赛题评审组评分。每个赛题评选出:优胜奖1~2名,奖金1.3万元;优秀奖2~3名,奖金0.5万元。

(2)决赛:初赛的各赛题优胜奖10~14支队伍进行路演,评出3项“开源创新之星”奖,获奖者追加奖金2万元;3~5项“开源新秀”奖,获奖者追加奖金1万元。

5. 赛事报名和联系方式

报名网址:https://competition.atomgit.com/competitionInfo?id=f702525c4fb87ddb624211ef6fb23e20

#heading-0-0

联系方式:taosm@pcl.ac.cn

赛事微信群二维码:

-

openDACS 2025 开源EDA与芯片赛项 赛题七:基于大模型的生成式原理图设计2025-11-13 2029

-

【精选直播】openDACS 2025 开源EDA与芯片大赛 赛题五 赛题七 直播宣讲会2025-11-11 1060

-

【精选直播】openDACS 2025 开源EDA与芯片大赛 赛题六 赛题三 直播宣讲会2025-11-04 980

-

【精选直播】openDACS 2025 开源EDA与芯片大赛 赛题二 赛题四 直播宣讲会2025-10-28 1237

-

【赛题知多少】 紫光同创赛题答疑专场|2025年全国大学生嵌入式芯片与系统设计竞赛FPGA赛道2025-08-06 3943

-

EDA²侠客岛难题挑战·2025已正式开启2025-03-05 2014

-

思尔芯赛题正式发布,邀你共战EDA精英挑战赛!2024-08-03 1837

-

2023电赛A题国奖CW32 开源分享2023-11-02 5644

-

开放原子开源大赛OpenHarmony创新赛 | 宣讲会议程一图抢鲜看2023-05-30 837

-

OpenHarmony创新赛 | 赛事宣讲会日期重磅官宣!为你带来超详尽的赛事攻略2023-05-25 1141

-

广和通赛题宣讲之第六届(2023)全国大学生嵌入式芯片与系统设计竞赛2023-03-06 1626

-

openDACS第一批开源EDA核心贡献者名单、openDACS V2.0版本在CCF Chip2022正式发布2022-08-15 5628

全部0条评论

快来发表一下你的评论吧 !