CMOS集成电路中闩锁效应的产生与防护

描述

文章来源:Jeff的芯片世界

原文作者:Jeff的芯片世界

本文介绍了CMOS中的闩锁效应与解决措施。

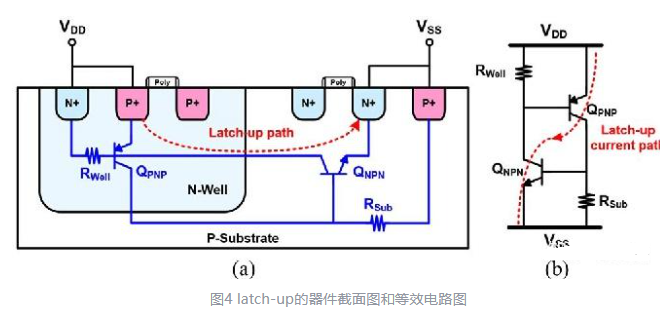

什么是闩锁效应

闩锁效应(Latch-up)是CMOS集成电路中一种危险的寄生效应,可能导致芯片瞬间失效甚至永久烧毁。它的本质是由芯片内部的寄生PNP和NPN双极型晶体管(BJT)相互作用,形成类似可控硅(SCR)的结构,在特定条件下触发低阻抗通路,使电源(VDD)和地(GND)之间短路,引发大电流失控。

这种现象在早期CMOS工艺中尤为突出,但随着制程优化(如阱隔离、保护环设计等),现代芯片的闩锁风险已大幅降低。然而,在高压、高速或恶劣环境(如高温、ESD冲击)下,闩锁仍可能被意外触发,成为半导体可靠性设计的重要挑战。

闩锁效应的产生与防护

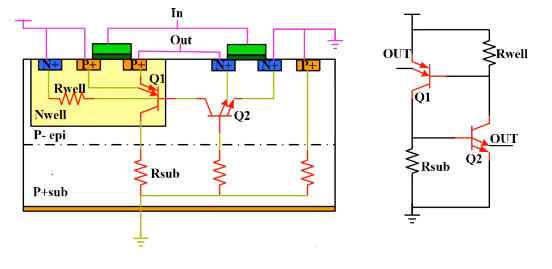

闩锁的核心机制源于CMOS结构中的寄生四层PNPN结构。NMOS的源/漏区(N+)与P型衬底形成NPN晶体管,PMOS的源/漏区(P+)与N阱形成PNP晶体管,而衬底电阻(Rsub)和阱电阻(Rwell)则提供了正反馈路径。当外部干扰(如电压瞬变、ESD静电)使其中一个寄生BJT导通,另一个BJT的基极电流会被放大,形成正反馈循环,最终导致SCR“锁定”在导通状态。此时,即使触发信号消失,大电流仍会持续,直至芯片过热损坏。

为应对这一问题,半导体行业采取了多种防护措施。在工艺层面,通过增加阱和衬底接触、使用保护环(Guard Ring)以及逆向掺杂阱来降低寄生电阻并阻断载流子扩散。在电路设计层面,电源去耦电容、ESD防护器件(如TVS二极管)以及优化的版图布局(如确保NMOS靠近GND、PMOS靠近VDD)都能有效抑制闩锁效应。

闩锁效应的实际影响与行业应对

闩锁效应可能导致芯片突然失效,表现为电流激增、功能紊乱甚至永久损坏。在高温或高压环境下,这种风险尤为显著。为评估芯片的抗闩锁能力,行业采用JEDEC78测试和ESD模拟等标准方法,通过施加脉冲电流或电压来测量触发阈值和维持电流,确保芯片在极端条件下的可靠性。

闩锁效应是CMOS工艺的固有挑战,但通过工艺改进、电路优化和严格测试,其风险已大幅降低。

-

闩锁效应的形成原理和测试流程2025-07-03 5094

-

CMOS的闩锁效应:Latch up的原理分析2020-12-23 62694

-

什么是闩锁效应?2012-08-01 9895

-

如何解决CMOS电路中的闩锁效应在现实生活中有什么具体的...2013-05-29 3244

-

CMOS集成电路使用时的技术要求2018-12-13 3225

-

什么是闩锁效应?闩锁效应的触发方式有哪几种?2021-06-17 6673

-

CMOS数字集成电路是什么?CMOS数字集成电路有什么特点?2021-06-22 5259

-

TTL集成电路与CMOS集成电路元件比较2021-07-26 4373

-

关于TTL集成电路与CMOS集成电路看完你就懂了2021-09-28 5340

-

高阻衬底集成电路抗闩锁效应研究2010-05-11 419

-

CMOS闩锁效应2010-09-26 1580

-

CMOS集成电路的性能及特点有哪些?2009-11-30 1572

-

巧焊场效应管和CMOS集成电路2010-01-16 1174

-

CMOS电平的介绍和CMOS的闩锁效应详细概述2021-01-06 2030

-

芯片失效机理之闩锁效应2024-12-27 6088

全部0条评论

快来发表一下你的评论吧 !