ADC34RF72 四通道、16位、1.5GSPS、超低噪声频谱密度(NSD)射频采样接收器技术手册

描述

该ADC34RF72是一款 16 位、1.5GSPS(非交错)、四通道模数转换器 (ADC)。该器件设计用于最高信噪比 (SNR),并提供 −163.7dBFS/Hz 的噪声频谱密度。使用内部平均模式,NSD 可以提高到低至 -168.7dBFS/Hz。缓冲模拟输入支持50、100、200Ω的可编程内部终端阻抗,全功率输入带宽为1.8GHz (−3dB)。

该器件包括多种数字处理功能,例如用于均衡的96抽头/通道可编程FIR滤波器、12位分数延迟滤波器以及多个数字下变频器(DDC)。有八个 DDC 支持 /2、/3 和 /5 的抽取因子,最高可达 /32768。48 位 NCO 支持相位相干跳频。

该ADC34RF72支持接口速率高达24.75Gbps的JESD204B/C串行数据接口。高能效ADC架构在1.5GSPS时功耗为1.1W/ch,并以较低的采样率提供功率缩放。

*附件:adc34rf72.pdf

特性

- 16位、四通道1.5GSPS ADC

- 噪声频谱密度:-163.7dBFS/Hz

- 热噪声:75.6dBFS

- 噪声系数:14.4dB

- 单核(非交错)ADC架构

- 光圈抖动:40fs

- 缓冲模拟输入

- 输入满量程:1.44Vpp (4.1dBm)

- 全功率输入带宽 (-3dB):1.8GHz

- 超低近距离残余相位噪声:

- −140dBc/Hz(10kHz失调时,1GHz时)

- 频谱性能(fIN = 1GHz,-1dBFS):

- 信噪比平坦:72.1dBFS

- HD2,3:68dBc

- 非 HD2,3:93dBFS

- 96 抽头/通道可编程 FIR 均衡器滤波器

- 12 位分数延迟滤波器

- 数字下变频器 (DDC)

- 高达 8 个 DDC

- 复数输出:/2、/3、/4、/5 到 /32768 抽取

- 48 位 NCO 相位相干跳频

- 快速跳频:< 1μs

- JESD204B/C 串行数据接口

- 最大通道速率:24.75Gbps

- 代码错误率 (CER):1E-15 错误/样本

- 功耗:1.1W/通道(1.5GSPS)

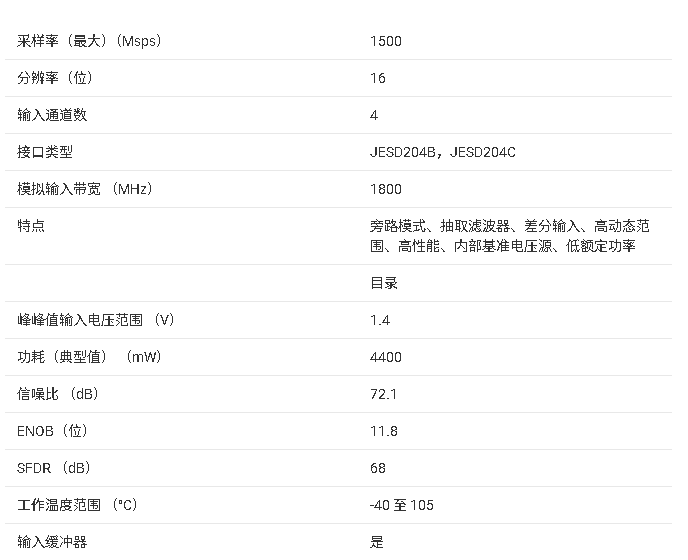

参数

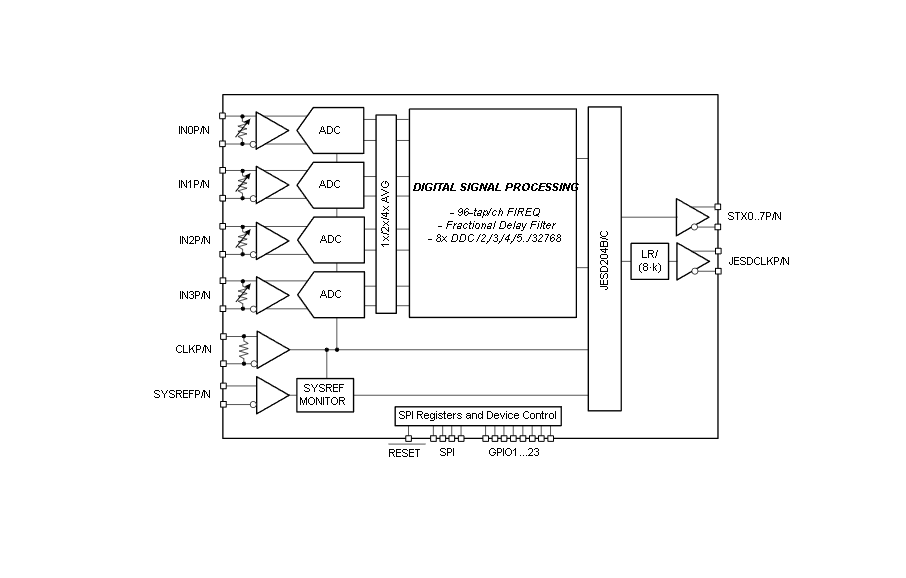

方框图

ADC34RF72 是一款 16 位四通道 1.5GSPS 射频采样模数转换器(ADC),具备高信噪比、低噪声密度及丰富数字处理功能,适用于多种高性能电子系统。

一、核心特性

- 基础性能参数

- 分辨率与采样率:16 位分辨率,单通道 1.5GSPS 采样率,采用非交错单核心架构,避免通道间串扰。

- 噪声与失真指标:噪声谱密度(NSD)低至 - 163.7dBFS/Hz,开启内部平均模式可优化至 - 168.7dBFS/Hz;1GHz 输入时,平坦信噪比(SNRflat)达 72.1dBFS,二次 / 三次谐波失真(HD2、HD3)为 68dBc。

- 输入与带宽:模拟输入全量程 1.44Vpp(4.1dBm),-3dB 全功率输入带宽 1.8GHz,支持 50Ω、100Ω、200Ω 可编程内部端接阻抗。

- 关键功能配置

- 数字信号处理:每通道配备 96 抽头可编程 FIR 均衡滤波器、12 位分数延迟滤波器;内置 8 个数字下变频器(DDC),支持 2/3/4/5 至 32768 的抽取比,48 位数控振荡器(NCO)实现相位相干跳频,跳频速度<1μs。

- 数据接口:支持 JESD204B/C 串行接口,最高通道速率 24.75Gbps,码误码率(CER)低至 1E-15 errors/sample。

- 功耗与封装:1.5GSPS 采样率下每通道功耗 1.1W,采用 13.8mm×13.8mm FCCSP 封装,共 289 引脚。

二、适用场景

ADC34RF72 凭借高性能与多功能,广泛应用于以下领域:

- 相控阵雷达:高采样率与低相位噪声满足雷达信号精准采集需求。

- 测试测量设备:如频谱分析仪、时域数字化仪,高信噪比确保信号分析精度。

- 通信与电子战:软件定义无线电(SDR)、通信基础设施、电子战系统,支持宽频信号处理与快速跳频。

- 工业检测:晶圆检测设备,高带宽与低噪声保障检测信号的准确性。

三、硬件设计要点

- 电源与时钟

- 电源需求:需 3 种电源轨,分别为模拟 1.8V(AVDD18)、模拟 1.2V(AVDD12)、数字 0.9V(DVDD09),推荐模拟电源使用低噪声 LDO,数字电源用开关 DC/DC 转换器。

- 时钟要求:差分时钟输入(CLKP/N)需 AC 耦合,输入频率范围 500-1500MHz,差分输入电压 0.6-2.8Vpp,建议时钟抖动<50fs 以保证信噪比性能。

- 引脚与布局

- 关键引脚:模拟输入(IN0P/N-IN3P/N)为差分信号,需匹配阻抗;JESD204B/C 接口引脚(STX0-7P/N)为高速串行信号,需 100Ω 差分布线;电源引脚(如 AVDD12、AVDD18)需就近放置旁路电容。

- 布局准则:模拟信号与时钟信号采用短路径、低串扰布线,差分线长度匹配;数字信号与模拟信号分区布局,避免干扰;使用电源和接地平面,降低阻抗与噪声。

- 初始化与控制

- 初始化流程:上电后需通过 RESET 引脚施加低脉冲复位,按 “DVDD09→AVDD12/CLKVDD12→AVDD18/GPIOVDD18” 顺序供电,复位后通过 SPI 配置内部寄存器。

- 控制方式:支持 SPI 接口(SCLK、SDIO、SEN 引脚)配置寄存器,24 个 GPIO 引脚可配置为 NCO 控制、校准冻结、全局断电等功能。

四、工作模式与性能优化

- 三种工作模式

- 正常模式:4 个独立通道,每通道对应 1 个 ADC 核心,单通道功耗最低。

- 2 倍平均模式:2 个 ADC 通道输入同一信号,内部平均处理,信噪比提升约 3dB,输出 2 个通道。

- 4 倍平均模式:4 个 ADC 通道输入同一信号,内部平均处理,信噪比提升约 6dB,输出 1 个通道。

- 性能优化手段

- 噪声优化:开启内部平均模式降低噪声谱密度;模拟输入端使用巴伦(如 Marki Microwave BAL-0003SMG)实现单端 - 差分转换,减少信号失真。

- 失真控制:时钟端采用低抖动时钟源(如 LMK04832),差分线严格匹配长度,减少相位不平衡导致的谐波失真。

- 功耗管理:支持快速断电、通道断电、全局断电三种低功耗模式,可根据需求通过 GPIO 或 SPI 选择,平衡性能与功耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC34RF52:高性能四通道14位1.5GSPS RF采样数据转换器深度解析2026-01-26 957

-

ADC34RF52 四通道 14 位 1.5GSPS 射频采样模数转换器(ADC)技术文档总结2025-10-29 816

-

ADC32RF54双通道 14 位高速 RF 采样 ADC 技术总结2025-10-28 985

-

ADC34RF55 技术文档总结2025-10-27 868

-

德州仪器ADC34RF52:14位1.5GSPS射频采样ADC的技术解析2025-08-27 1166

-

高性能射频采样ADC:ADC32RF5x系列技术解析2025-08-15 1406

-

德州仪器ADC34RF55:14位3GSPS RF采样ADC技术解析2025-08-14 1555

-

AD9084 Apollo MxFE四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册2025-04-28 2029

-

AD9084 MxFE 四通道、16位、28 GSPS RF DAC和四通道、12位、20 GSPS RF ADC技术手册2025-04-18 2387

-

AD9081四通道、16位、12 GSPS RF DAC和四通道、12位、4 GSPS RF ADC数据表2024-07-31 951

-

ADC34RF55四通道14位3GSPS射频采样数据转换器数据表2024-07-15 586

-

DAC34SH84四通道16位1.5GSPS数模转换器(DAC)数据表2024-06-20 769

-

一文教你如何利用噪声频谱密度评估软件定义系统中的ADC2020-12-31 2491

全部0条评论

快来发表一下你的评论吧 !