DAC39RF20核心信息总结

描述

该DAC39RF20是一款具有 16 位分辨率的单通道和双通道数模转换器 (DAC)。通过外部全速率时钟,这些器件在单边沿采样模式(NRZ 和 RF)下支持 22GSPS,在双边沿采样模式(DES2XL、DES2XH)下支持 44GSPS。当使用内部PLL/VCO时,器件在单边沿采样模式(NRZ和RF)下支持17GSPS,在双边沿采样模式(DES2XL、DES2XH)下支持34GSPS。这些器件可用作非插值或插值DAC,用于直接RF采样或复杂基带信号生成。两个通道的最大输入数据速率为 21GSPS(12 位分辨率)或 15.75GSPS(16 位分辨率)。一个通道的最大速率为 22GSPS(16 位分辨率)。该器件可以在超过 20GHz 的频率下生成大于 10GHz 带宽的信号,从而能够通过 Ku 频段直接采样。

*附件:dac39rf20.pdf

特性

- 16位多奈奎斯特DAC内核

- DAC采样率:

- NRZ,射频模式:22GSPS

- DES2xL、DES2xH 模式:44GSPS

- 最大输入数据速率:

- 12 位,双通道:21GSPS/通道

- 16 位,双通道:15.75GSPS/通道

- 16 位,单通道:22GSPS

- 输出频率范围:>18GHz

- fOUT = 10GHz、DES2xL 模式下的性能

- 本底噪声(小信号):–170dBFS/Hz

- SFDR (-0.1dBFS):–55dBc

- IMD3(每音-7dBFS):–60dBc

- 附加相位噪声,10kHz 偏移:-132dBc/Hz

- 可选的PLL/VCO,用于DAC时钟生成

- 四个集成数字上变频器 (DUC)

- 插值:1x、4x、6x、8x 至 256x

- 用于 I/Q 输出的复杂基带 DUC

- 用于直接射频采样的复数到实际上变频

- 64 位频率分辨率 NCO

- 具有跳频功能的相位连续、同步和复位选项

- DUC 输入或 DAC 输入端的可编程 FIR 均衡器

- 直接数字合成 (DDS) 功能

- 四个分段线性波形发生器

- 16 个预存储的波形

- 256 总向量

- 自动或同步外部触发器

- 频率、幅度、相位接口流

- 四个分段线性波形发生器

- JESD204C界面

- 16 通道,高达 32.5Gbps

- C-S 类,子类 1 兼容

- 自动时钟和 SYSREF 校准和跟踪

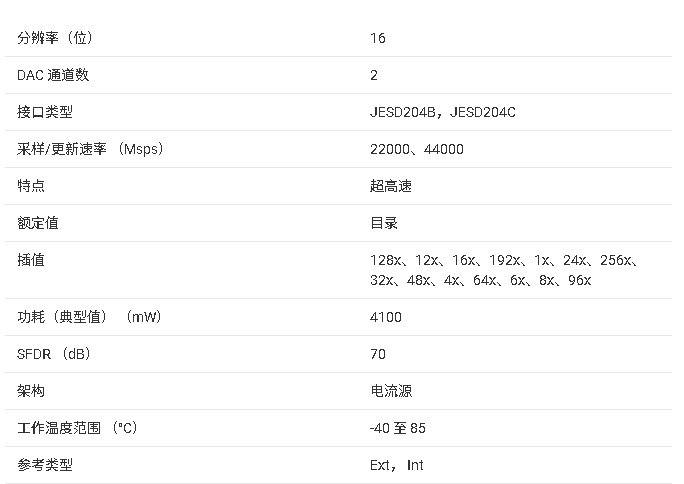

参数

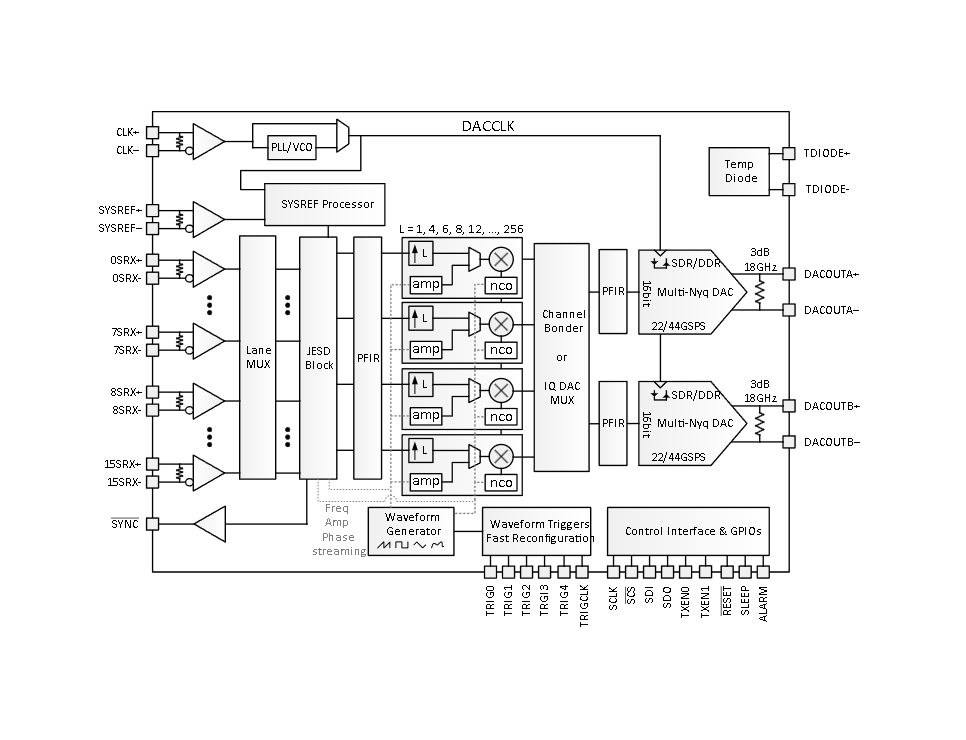

方框图

一、核心性能参数

1. 采样率与频率特性

- 采样率范围 :根据工作模式灵活调整,NRZ(非归零码)、RF 模式下最高 22GSPS;DES2xL(双沿采样低带宽)、DES2xH(双沿采样高带宽)模式下,因支持双沿采样,采样率翻倍至 44GSPS,适配不同信号带宽需求。

- 输出频率与信号质量 :输出频率范围超 18GHz,可覆盖 Ku 频段;10GHz 输出时(DES2xL 模式),噪声底低至 - 170dBFS/Hz,三阶交调失真(IMD3,-7dBFS 双音输入)达 - 60dBc,10kHz 偏移处附加相位噪声为 - 132dBc/Hz,保证宽频带内信号纯净度。

- 输入数据率 :双通道配置下,12 位分辨率时最高 21GSPS / 通道,16 位分辨率时最高 15.75GSPS / 通道;单通道 16 位分辨率时最高 22GSPS,适配高速数据传输场景。

2. 关键集成功能

- 数字上变频器(DUC) :集成 4 个 DUC,支持 1x、4x、6x 至 256x 插值,配备 64 位分辨率数控振荡器(NCO),可实现相位连续、同步的频率跳变,支持复数基带信号到实 RF 信号的直接上变频,减少外部电路复杂度。

- 直接数字合成(DDS) :含 4 个分段线性波形发生器,可预存 16 种波形、256 个向量,支持自动触发或同步外部触发;支持频率、幅度、相位参数的实时 streaming 传输,可生成非线性调频(NLFM)、相位编码雷达脉冲等复杂波形。

- 可编程 FIR 均衡器 :可灵活配置在 DUC 输入或 DAC 输入端,用于补偿信号链路损耗,优化信号幅频特性,适配不同传输链路的损耗特性。

- JESD204C 接口 :配备 16 条 SerDes 通道,单通道最高 32.5Gbps 速率,兼容 Class C-S subclass-1,支持多器件同步;支持 8b/10b 与 64b/66b 编码,64b/66b 模式下需启用扰码功能,保障时钟恢复稳定性。

二、适用场景

基于高采样率、宽频带输出及高集成度特性,DAC39RF20 主要应用于以下领域:

- 卫星通信(SATCOM) :超 18GHz 输出频率覆盖卫星通信常用频段,低噪声与低失真特性保障卫星信号收发链路的信号质量,适配天地一体化通信系统。

- 相控阵天线系统 :支持快速频率跳变与多通道同步,可通过 JESD204C 接口实现多 DAC 器件的精准时序对齐,满足相控阵波束赋形对高速、同步信号生成的需求。

- 合成孔径雷达(SAR)激励器 :22-44GSPS 高采样率可生成宽带宽雷达激励信号,DDS 功能支持自定义雷达脉冲波形,适配高分辨率 SAR 成像系统。

- 无线通信测试仪与任意波形发生器(AWG) :DDS 波形存储与 streaming 功能可生成 LTE、5G 等标准通信信号,也可自定义测试波形,用于通信设备研发与生产测试。

三、硬件设计关键要点

1. 电源与时钟配置

- 电源需求 :需多组独立电源轨,包括 1.8V 模拟电源(VDDA18A/B,为 DAC 通道 A/B 供电)、0.8V 数字电源(VDDDIG,数字逻辑供电)、1.8V 时钟电源(VDDCLK18,时钟输入缓冲供电)、-1.8V 负电源(VEEAM18/VEEBM18,DAC 电流源偏置供电);每个电源引脚需并联 100nF MLCC 电容与 1μF 钽电容,电容紧贴引脚布局,降低电源噪声。

- 时钟设计 :外部时钟模式下,CLK± 需 AC 耦合至时钟源,内部集成 100Ω 差分端接,时钟占空比需保持 45%-55%;内部 PLL/VCO 模式支持 8.125-17GHz 时钟生成,需配置 PLL 倍频系数(MPY)与参考时钟分频系数(REFDIV),确保 VCO 频率在 8.125-16.25GHz 范围内。

2. 布局与布线准则

- 差分信号处理 :DAC 模拟输出(DACOUTA±/DACOUTB±)、时钟(CLK±)及 JESD204C SerDes 通道(0SRX±-15SRX±)需采用差分布线,阻抗控制为 100Ω,长度匹配误差≤5mil,减少信号时延差(skew)。

- 地平面隔离 :模拟地(AGND)、数字地(DGND)与时钟地(VSSCLK)需单点连接,避免地环路;高频信号(时钟、SerDes)与低频控制信号(SPI)分开布局,间距≥2mm,减少串扰。

- 热设计 :采用 289 球 FCCSP 封装(13.8mm×13.8mm,0.8mm pitch),封装热焊盘需通过至少 4 个过孔连接至 PCB 接地平面,PCB 铜皮面积不小于封装面积的 2 倍,确保结温(Tj)不超过 150°C(最高额定值)。

3. 初始化与校准流程

- 寄存器配置 :通过 SPI 接口(SCLK、SDI、SDO、SCS)配置工作模式,包括 JESD204C 格式(JMODE)、DSP 工作模式(DUC/DDS/ 旁路)、插值系数(DSP_L)、PLL 参数(MPY、REFDIV);配置完成后需等待 PLL 锁定(PLL_LOCKED=1)。

- 同步校准 :SYSREF 用于多器件同步,需确保 SYSREF 周期为 DACCLK 周期的整数倍(如 32×DACCLK);启动时需发送 15 个 SYSREF 脉冲完成时钟与 LMFC(本地多帧时钟)对齐,再使能系统(SYS_EN=1),确保链路确定性时延。

四、工作模式与性能优化

1. 核心工作模式

- DUC 模式 :接收 JESD204C 接口的 I/Q 基带数据,经 DUC 插值(1x-256x)与 NCO 混频后,上变频至目标 RF 频率,直接驱动 DAC 输出;支持相位连续的频率跳变,适用于软件定义无线电(SDR)的基带 - 射频直接转换场景。

- DDS 模式 :

- SPI 模式 :通过 FREQ、PHASE、AMP 寄存器配置单频信号参数,生成固定频率的正弦波,适用于本地振荡器(LO)场景。

- 向量模式 :预存 256 个向量(含频率、幅度、相位参数),通过触发信号切换向量,生成复杂波形(如 NLFM),适用于雷达脉冲生成。

- 流模式 :通过 JESD204C 接口实时 streaming 传输频率 / 相位 / 幅度参数,支持动态波形调整,适用于跳频通信场景。

- 旁路模式 :JESD204C 输入数据直接传输至 DAC 输出,跳过 DUC/DDS 处理,适用于简单信号直通(如低带宽测试信号)场景。

2. 性能优化手段

- 噪声抑制 :模拟输入端并联 10nF-1μF 电容滤除电源噪声;SerDes 通道串联 50Ω 电阻与 100pF 电容抑制高频干扰;启用 Dither(抖动)与 DEM(动态元素匹配)功能,降低 DAC 非线性失真(如谐波失真)。

- 失真控制 :配置可编程 FIR 均衡器补偿链路损耗,优化信号幅频特性;根据输出频率选择 DAC 输出模式(NRZ 用于 0-FDACCLK/2 频段,RF 用于 FDACCLK/2-FDACCLK 频段),避免奈奎斯特区信号衰减。

- 功耗管理 :支持 APP Sleep(DSP / 编码器断电)、Link Sleep(JESD 链路层断电)、PHY Sleep(SerDes 物理层断电)等低功耗模式,正常工作时 VDD 电流典型 5mA、VIO 电流典型 10μA,可根据系统功耗需求灵活切换。

五、可靠性与异常处理

1. 异常监测与保护

- 过压 / 过流保护 :输入电压超出绝对最大额定值(如 VDDA18A/B 最高 2.45V)时,需外部限流电路限制输入电流在 ±10mA 以内,避免 ESD 保护二极管损坏。

- 温度监测 :内置温度二极管(TDIODE±),可通过外部电路监测结温,当结温接近 150°C 时,需通过降额(如降低采样率)或增强散热(如增加 PCB 散热铜皮)控制温度。

- 链路故障处理 :JESD204C 接口支持链路状态监测(LANE_STATUS 寄存器),出现弹性缓冲区溢出(EB_ERR)或链路断开(LINK_UP=0)时,可通过 JESD_RST 寄存器复位链路,重启 CGS(码组同步)与 ILAS(初始 lane 对齐)流程。

2. 可靠性设计

- ESD 防护 :符合 HBM(人体放电模型)±500V、CDM(带电器件模型)±250V 标准,PCB 布局时需预留足够的 ESD 防护器件空间(如 0402 封装 TVS 管)。

- 数据完整性 :支持 SECDED(单粒子误差校正)与 CRC 校验,减少高速数据传输中的误码;JESD204C 接口支持 FEC(前向纠错),64b/66b 模式下可启用 FEC 提升链路抗干扰能力。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC3174 产品核心信息总结2025-11-14 812

-

DAC8162-Q1 产品核心信息总结2025-11-12 880

-

DAC39RFx10 系列产品技术文档总结2025-10-27 1011

-

DDS39RF10产品技术文档总结2025-10-24 1323

-

请问DAC39RF10B的新版说明书里面INL的单位Codes是怎么定义的?2024-11-14 386

-

DAC39RF12、DAC39RFS12双通道和单通道数模转换器(DAC)数据表2024-07-15 729

-

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位双通道和单通道多奈奎斯特数模转换器(DAC)数据表2024-07-12 717

全部0条评论

快来发表一下你的评论吧 !