ADS9217文件内容总结

描述

ADS921x 是一系列 18 位、高速、双通道、同步采样、模数转换器 (ADC),带有用于 ADC 输入的集成驱动器。集成的ADC驱动器简化了信号链,降低了精密应用的功耗,并支持超过1MHz的高频信号。由于不需要外部去耦电容,集成ADC基准电压缓冲器针对宽带宽应用进行了优化。

ADS921x 使用串行 LVDS (SLVDS) 数据接口,可实现高速数字通信,同时最大限度地降低数字开关噪声。使用每个ADC通道的单独SLVDS输出或两个ADC通道的一个SLVDS输出读取双通道ADC数据。

*附件:ads9217.pdf

特性

- 高速低功耗:

- ADS9219:20MSPS/通道,230mW/通道

- ADS9218:10MSPS/通道,146mW/通道

- ADS9217:5MSPS/通道,95mW/通道

- 2 通道,同时采样

- 功能集成:

- 集成ADC驱动器

- 集成精密参考

- 共模电压输出缓冲器

- 高性能:

- 18 位无缺失码

- INL:±1LSB,DNL:±0.75LSB

- 信噪比:95.5dB和104.5dB信噪比,OSR = 16

- 宽输入带宽 (–3dB):

- ADS9219和ADS9218:90MHz

- ADS9217:45MHz

- 串行LVDS接口:

- SDR 和 DDR 输出模式

- 同步时钟和数据输出

- 扩展工作范围:–40°C 至 +125°C

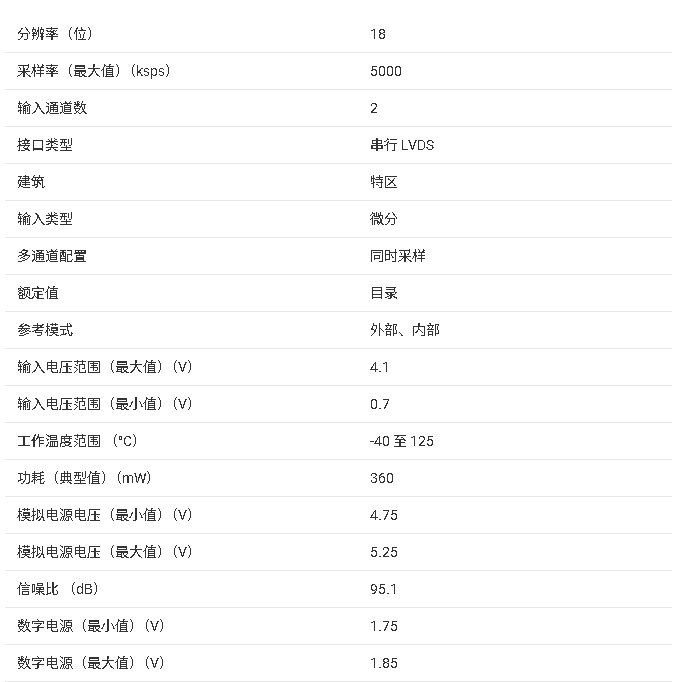

参数

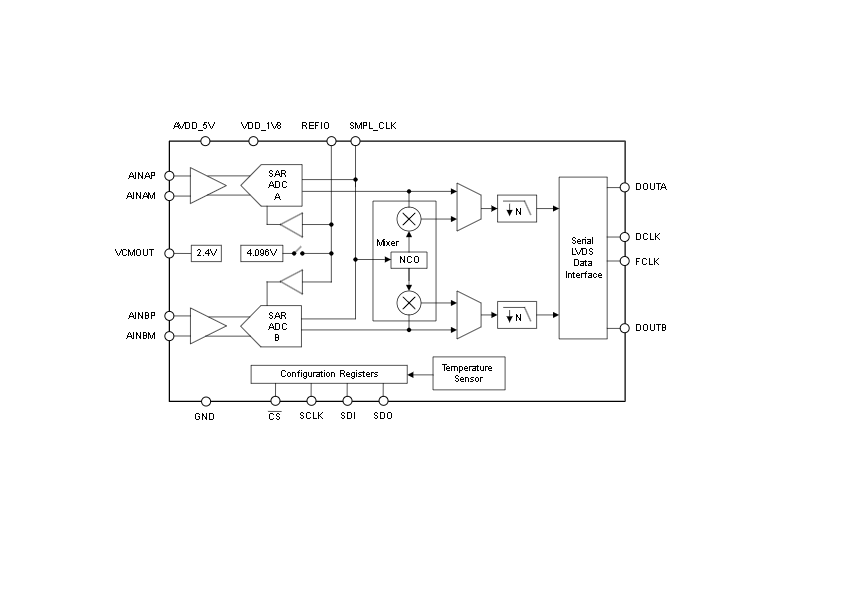

方框图

一、产品基础信息与核心差异对比

ADS9217、ADS9218、ADS9219 同属 ADS921x 系列,核心架构均为双通道同步采样 SAR ADC,共享集成 ADC 驱动、精密基准等特性,主要差异体现在采样速率与功耗,具体参数对比如下:

| 参数分类 | 参数名称 | ADS9217 | ADS9218 | ADS9219 | 系列共同特性 |

|---|---|---|---|---|---|

| 基础性能 | 最大采样速率 | 5MSPS / 通道 | 10MSPS / 通道 | 20MSPS / 通道 | 1. 双通道同步采样,18 位分辨率无失码2. 集成 ADC 输入驱动、4.096V 精密基准与共模电压输出缓冲器3. 支持 ±3.2V 差分输入满量程(FSR)4. 串行 LVDS 接口,支持 SDR/DDR 模式与同步时钟输出5. 内置数据平均(2-16 样本)、数字下变频器(DDC)与 10 位温度传感器6. 工作温度范围:-40°C 至 + 125°C,封装为 6mm×6mm 40 引脚 VQFN(RHA) |

| 基础性能 | 典型功耗(满速) | 95mW / 通道 | 146mW / 通道 | 230mW / 通道 | |

| 信号处理 | 模拟输入带宽(-3dB) | 45MHz | 90MHz | 90MHz | |

| 信号处理 | 典型 SNR(2kHz 输入) | 95.5dBFS | 95.5dBFS | 95.5dBFS | |

| 精度指标 | 积分非线性(INL) | ±0.8LSB(-40°C 至 125°C) | ±0.8LSB(-40°C 至 125°C) | ±0.8LSB(-40°C 至 125°C) | |

| 精度指标 | 微分非线性(DNL) | ±0.4LSB | ±0.4LSB | ±0.4LSB | |

| 精度指标 | 输入失调误差 | ±40LSB | ±40LSB | ±40LSB | |

| 精度指标 | 增益误差 | ±0.01% FSR(典型值) | ±0.01% FSR(典型值) | ±0.01% FSR(典型值) |

二、关键功能特性详解

1. 模拟输入与基准电路配置

1.1 模拟输入特性

- 输入类型 :支持 AC 耦合与 DC 耦合差分输入,需确保输入共模电压与 VCMOUT 引脚电压匹配,VCMOUT 典型值为 2.385V(ADS9217)、2.410V(ADS9218)、2.460V(ADS9219),共模输入范围围绕 VCMOUT 波动 ±70mV。

- 输入参数 :输入偏置电流典型值 0.1nA,温度漂移 0.1nA/°C;输入采样电容 22pF,等效输入网络含 2Ω 与 0.6Ω 匹配电阻(如图 7-1 等效输入网络所示)。

- 通道隔离 :通道间隔离度达 120dB(2kHz 输入),有效抑制通道串扰。

1.2 基准电压配置

- 内部基准 :默认启用 4.096V 内部基准,温度漂移 6-20ppm/°C,需在 REFIO 引脚外接 10μF 陶瓷去耦电容以滤除噪声,REFM 引脚需连接至地。

- 外部基准 :可通过两种方式启用外部基准:一是配置 SPI(SPI_EN=1),写入 PD_REF=1b(寄存器 0xC1,Bank1);二是设置 SPI_EN=0,将 SDI/EXTREF 引脚拉低,外部基准电压范围需为 4.076V-4.116V。

2. 数据处理与接口功能设计

2.1 数据平均(Decimation)功能

- 平均模式 :支持 2、4、8、16 样本平均,平均使能后输出速率按对应倍数降低(如 ADS9219 用 16 样本平均时,输出速率降至 1.25MSPS / 通道),且 SNR 随平均倍数提升,OSR=16 时 SNR 可达 104.8dBFS。

- 配置方式 :需通过多寄存器协同配置,包括 OSR_EN(0x0D [6],使能平均)、OSR(0x0D [5:2],选择平均倍数)、OSR_CLK(0xC0 [9:7],时钟配置),同时 SMPL_SYNC 引脚可同步多器件的平均滤波复位。

- 数据输出特性 :平均后初始输出 N 个无效数据,后续输出平均结果(如图 7-4 数据输出时序所示)。

2.2 数字下变频器(DDC)

- 核心构成 :集成 24 位数控振荡器(NCO)与数字混频器,每个通道可输出 48 位 I/Q 数据(24 位 I+24 位 Q),NCO 为双通道共享。

- NCO 配置 :NCO 频率通过 NCO_FREQUENCY 寄存器(0xFD、0xFE)配置,公式为fNCO =224fSMP L _CLK ×(NCOFREQUENC Y [ 23 : 0 ] &0xFFFF 0 );初始相位通过 NCO_PHASE 寄存器(0xFC、0xFD)配置,支持 0、π、2π 三种初始相位,可通过 SMPL_SYNC 引脚复位相位。

- 抽取配置 :支持 2、4、8、16 倍抽取,需配合数据平均功能,抽取倍数通过 OSR 寄存器(0x0D [5:2])设置,同时需配置 OSR_INIT1(0xC0 [11:10])、OSR_INIT2(0xC4 [5:4])等初始化寄存器。

2.3 LVDS 数据接口

- 接口模式 :支持 1 lane(单通道输出双路数据)与 2 lane(双通道分别输出)两种 lanes 配置,数据帧宽可选 20 位或 24 位(默认 24 位),数据速率支持 SDR(单数据率)与 DDR(双数据率)。

- 时钟计算 :数据时钟(DCLK)频率由采样时钟(SMPL_CLK)、lanes 数量、帧宽与速率决定,公式为,例如 2 lane、24 位 DDR 模式下,DCLK=12×SMPL_CLK(ADS9219 满速时 DCLK=240MHz)。

- 信号匹配 :LVDS 差分对(如 DCLKP/DCLKM、DOUTAP/DOUTAM)需在接收端靠近器件处接 100Ω 匹配电阻,确保信号完整性。

3. 特殊功能模块说明

3.1 温度传感器

- 性能指标 :10 位精度,温度测量范围覆盖器件工作温度区间,需通过固定寄存器序列读取:

- 向 Bank1 的 0x90 寄存器写入 0x4000,加载温度数据至 0x91 寄存器;

- 读取 Bank1 的 0x91 寄存器,获取 10 位温度数据;

- 向 Bank1 的 0x90 寄存器写入 0x0000,完成读取。

- 温度计算 :通过公式转换为实际温度值。

3.2 数据随机化功能

- 功能作用 :启用后 ADC 输出与伪随机序列(PRBS)或 ADC 转换结果 LSB 进行异或操作,减少数据传输过程中地弹噪声对模拟性能的干扰,尤其适用于 PCB 布局难以优化的场景。

- 配置方式 :通过 XOR_EN(0x12 [3],使能异或)、XOR_MODE(0xFB [2],选择异或对象)配置,默认使用 PRBS 异或,可切换为 LSB 异或。

3.3 测试模式

- 模式类型 :支持三种测试图案,用于接口调试与链路验证:

- 固定模式:输出 TP0_A/TP0_B 寄存器(0x14/0x19)定义的固定值;

- 数字斜坡:输出随 RAMP_INC_A/RAMP_INC_B(0x13 [7:4]/0x18 [7:4])配置递增的斜坡信号,递增步长为 N+1(N 为寄存器配置值);

- 交替模式:交替输出 TP0_A/TP1_A、TP0_B/TP1_B 寄存器(0x14/0x15、0x19/0x1A)定义的值。

- 启用方式 :通过 TP_EN_A/TP_EN_B(0x13 [1]/0x18 [1],使能测试模式)、TP_MODE_A/TP_MODE_B(0x13 [3:2]/0x18 [3:2],选择模式类型)配置。

三、电气规格详情(典型值,TA=25°C,AVDD_5V=5V,VDD_1V8=1.8V)

3.1 供电与电流特性

| 器件型号 | AVDD_5V 电流(满速) | AVDD_5V 电流(掉电) | VDD_1V8 电流(满速) | VDD_1V8 电流(掉电) |

|---|---|---|---|---|

| ADS9217 | 20-24mA | 2mA | 50-66mA | 2mA |

| ADS9218 | 33-40mA | 2mA | 70.5-89mA | 2mA |

| ADS9219 | 55-59mA | 2mA | 103-110mA | 2mA |

3.2 AC 性能指标

| AC 性能参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 信号噪声失真比(SINAD) | fIN=2kHz | 93 | 95.4 | - | dB |

| 信号噪声失真比(SINAD) | fIN=1MHz | - | 94.3 | - | dB |

| 信噪比(SNR) | fIN=2kHz | 93.3 | 95.5 | - | dBFS |

| 信噪比(SNR) | fIN=1MHz | - | 94.9 | - | dBFS |

| 总谐波失真(THD) | fIN=2kHz(ADS9217/9218) | - | -120 | - | dB |

| 总谐波失真(THD) | fIN=2kHz(ADS9219) | - | -118 | - | dB |

| 总谐波失真(THD) | fIN=1MHz(全系列) | - | -104 | - | dB |

| 无杂散动态范围(SFDR) | fIN=2kHz | - | 118 | - | dB |

| 无杂散动态范围(SFDR) | fIN=1MHz | - | 104 | - | dB |

| 孔径抖动 | 单端 CMOS 时钟 | - | 0.3 | - | psRMS |

| 孔径抖动 | 差分 LVDS 时钟 | - | 0.8 | - | psRMS |

3.3 数字接口电气特性

| 接口类型 | 参数名称 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|---|

| LVDS 输入(SMPL_CLK) | 高电平输入电压(P-M) | AC 耦合 | 100 | - | - | mV |

| LVDS 输入(SMPL_CLK) | 高电平输入电压(P-M) | DC 耦合 | 300 | - | - | mV |

| LVDS 输入(SMPL_CLK) | 低电平输入电压(P-M) | AC 耦合 | - | - | -100 | mV |

| LVDS 输入(SMPL_CLK) | 低电平输入电压(P-M) | DC 耦合 | - | - | -300 | mV |

| LVDS 输出 | 差分输出电压 | RL=100Ω | 200 | 350 | 500 | mV |

| LVDS 输出 | 输出共模电压 | RL=100Ω | 0.88 | 1.1 | 1.32 | V |

| CMOS 输入(CS/SCLK/SDI) | 低电平输入电压(VIL) | - | -0.1 | - | 0.5 | V |

| CMOS 输入(CS/SCLK/SDI) | 高电平输入电压(VIH) | - | 1.3 | - | VDD_1V8 | V |

| CMOS 输出(SDO) | 低电平输出电压(VOL) | IOL=200μA | 0 | - | 0.4 | V |

| CMOS 输出(SDO) | 高电平输出电压(VOH) | IOH=200μA | 1.4 | - | VDD_1V8 | V |

四、寄存器配置体系

器件包含 3 个寄存器组(Bank 0/1/2),共定义数十个配置寄存器,关键寄存器功能分类如下:

4.1 Bank 0:基础配置寄存器

| 寄存器地址 | 寄存器名称 | 核心功能 | 关键字段说明 |

|---|---|---|---|

| 0x00 | 复位与 SPI 模式寄存器 | 器件复位、SPI 模式选择 | - RESET(bit0):1b 时复位所有寄存器- SPI_MODE(bit2):0b 为菊花链模式,1b 为传统模式- SPI_RD_EN(bit1):1b 时使能寄存器读(仅传统模式) |

| 0x01 | 菊花链长度寄存器 | 配置 SPI 菊花链设备数量 | - DAISY_CHAIN_LEN(bit6-2):0=1 个 ADC,31=32 个 ADC |

| 0x03 | 寄存器组选择寄存器 | 选择待操作的寄存器组 | - REG_BANK_SEL(bit7-0):0=Bank0,2=Bank1,16=Bank2 |

| 0x04 | 初始化配置寄存器 | 器件初始化控制 | - INIT_1(bit3-0):初始化时写 1011b,正常运行写 0000b |

4.2 Bank 1:功能配置寄存器

| 寄存器地址 | 寄存器名称 | 核心功能 | 关键字段说明 |

|---|---|---|---|

| 0x0D | 数据格式与平均控制寄存器 | 数据格式选择、数据平均使能 | - DATA_FORMAT(bit13):0 = 二进制,1 = 二进制补码- OSR_EN(bit6):1b 使能数据平均- OSR(bit5-2):0=2 倍平均,3=16 倍平均 |

| 0x12 | 数据接口配置寄存器 | 数据 lanes、异或使能 | - DATA_LANES(bit2-0):0=2 lane 20 位,2=2 lane 24 位,5=1 lane 20 位,7=1 lane 24 位- XOR_EN(bit3):1b 使能数据异或 |

| 0x13/0x18 | ADC A/B 测试模式寄存器 | 测试图案控制 | - TP_EN_A/B(bit1):1b 使能测试模式- TP_MODE_A/B(bit3-2):0 = 固定模式,2 = 斜坡模式,3 = 交替模式- RAMP_INC_A/B(bit7-4):斜坡递增步长(N+1) |

| 0x90/0x91 | 温度传感器控制 / 数据寄存器 | 温度数据读取 | - TS_LD(0x90 bit14):1b 触发温度数据加载- TEMPERATURE_SENSOR(0x91 bit9-0):10 位温度数据 |

| 0xC0 | 时钟与电源控制寄存器 | 时钟配置、通道掉电 | - OSR_INIT1(bit11-10):数据平均初始化- OSR_CLK(bit9-7):平均模式时钟配置- PD_CH(bit1-0):0 = 正常,1=ADC A 掉电,2=ADC B 掉电,3 = 双路掉电 |

| 0xC1 | 基准与数据速率寄存器 | 基准选择、数据速率 | - PD_REF(bit11):1b 禁用内部基准- DATA_RATE(bit8):0=DDR 模式,1=SDR 模式 |

| 0xFB | DDC 与异或模式寄存器 | DDC 使能、异或模式 | - MIXER_EN(bit0):1b 使能 DDC- XOR_MODE(bit2):0=PRBS 异或,1=LSB 异或- NCO_SYSREF(bit3):1b 支持 SMPL_SYNC 周期脉冲同步 |

| 0xFC/0xFD/0xFE | NCO 配置寄存器 | NCO 相位与频率 | - NCO_PHASE_COUNT(0xFC/0xFD):24 位 NCO 相位配置- NCO_FREQUENCY(0xFD/0xFE):24 位 NCO 频率配置 |

4.3 Bank 2:时钟配置寄存器

| 寄存器地址 | 寄存器名称 | 核心功能 | 关键字段说明 |

|---|---|---|---|

| 0x1Ch | 时钟配置寄存器 | ADS9217 专用时钟配置 | - CLK6(bit7-6):0=24 位 2 lane 模式,3 = 其他模式(仅 ADS9217 适用) |

五、应用设计与布局建议

5.1 典型应用场景

该系列 ADC 主要面向高精度、高 - speed 数据采集场景,包括:

- 功率分析仪:双通道同步采样电压、电流信号,计算功率参数

- 源测量单元(SMU):高精度测量电压、电流输出与反馈信号

- 船用设备:抗恶劣环境的高精度数据采集

- 伺服驱动器位置反馈:同步采集位置与速度信号

- 直流电源、交流源、电子负载:监测输入 / 输出电压、电流信号

5.2 应用电路设计

5.2.1 ≤20kHz 带宽 DAQ 电路

- 核心器件 :采用双通道全差分放大器 THS4552 驱动 ADC,THS4552 增益可通过 RFB 电阻配置(RFB=1kΩ 时增益 = 1,RFB=4.02kΩ 时增益 = 4)。

- 关键参数 :SNR≥92dB,THD≤-110dB,需在放大器输出端串联 270pF 电容与 ADC 输入匹配。

- 电路结构 :单端 / 差分信号经 THS4552 放大后,分别输入 ADC 的 AINAP/AINAM(通道 A)与 AINBP/AINBM(通道 B),VCMOUT 引脚提供共模电压参考。

5.2.2 ≤100kHz 带宽 DAQ 电路

- 核心器件 :同样采用 THS4552 驱动,新增 47pF 补偿电容优化高频性能。

- 关键参数 :SNR≥91dB,THD≤-110dB,ADC 输入端需保留 270pF 匹配电容,确保信号完整性。

5.2.3 ≤1MHz 带宽 DAQ 电路

- 核心器件 :选用高带宽全差分放大器 THS4541(850MHz 带宽),适配 ADC 90MHz 输入带宽需求。

- 关键参数 :SNR≥80dB,THD≤-100dB,电路中需添加 22pF 匹配电容与 50Ω 终端电阻,抑制高频反射。

5.3 电源与布局设计要点

5.3.1 电源去耦设计

- 供电体系 :包含 AVDD_5V(模拟电源,引脚 1、10)与 VDD_1V8(数字与模拟辅助电源,引脚 13、14、35-37),需独立供电。

- 去耦配置 :AVDD_5V 引脚需并联 1μF+0.1μF 陶瓷电容,VDD_1V8 引脚同样并联 1μF+0.1μF 陶瓷电容,所有电容需靠近引脚布局,避免过孔,减少寄生电感。

5.3.2 PCB 布局准则

- 分区布局 :将模拟部分(AINx、REFIO、VCMOUT)与数字部分(LVDS 接口、SPI 接口)严格分区,避免数字线穿越模拟区域。

- 接地处理 :暴露热焊盘(Thermal Pad)必须接地,REFM 引脚与 GND 需短路径连接,采用独立接地平面,减少地弹噪声。

- 差分对布线 :LVDS 差分对(如 DCLKP/DCLKM、DOUTAP/DOUTAM)需等长布线,长度差控制在 5mil 以内,且远离电源噪声源。

- 基准防护 :REFIO 引脚的 10μF 去耦电容需靠近器件,避免与数字信号平行布线,减少干扰。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS9326文件内容总结2025-10-22 672

-

服务器数据恢复—ocfs2文件系统被格式化为Ext4文件系统的数据恢复案例2025-06-10 871

-

服务器数据恢复—ocfs2文件系统被误格式化为Ext4文件系统的数据恢复案例2023-12-04 1106

-

HY MOTOR Basic 5.00文件分享2022-10-08 695

-

AD9213/9217 Wiki:使用基于ADS8-V1EBZ FPGA采集板的ADC评估板2021-03-23 2209

-

PADS Professional VX2.10文件免费下载2019-05-06 3328

-

Hash_1.0.4文件校验工具应用程序免费下载2018-07-09 1666

-

AltiumDesignerSummer9文件下载2015-07-30 1332

-

AltiumDesignerWinter09文件下载2013-08-10 810

-

fat32_fat32文件系统2012-05-21 7378

-

protel99文件转换成PADS2007文件的视频教程2009-09-12 12592

-

MP3文件原理2009-08-04 2240

-

UG8.5文件下载2009-02-06 1689

全部0条评论

快来发表一下你的评论吧 !