ADC3664-SEP文件内容总结

描述

ADC3664-xEP器件是一款低噪声、超低功耗、14位、125MSPS、高速双通道ADC。该器件专为最低噪声性能而设计,可提供 -156.9dBFS/Hz 的噪声频谱密度以及线性度和动态范围。ADC3664-xEP 提供 IF 采样支持,使该器件专为广泛的应用而设计。高速控制环路受益于低至一个时钟周期的短延迟。ADC在125MSPS时仅消耗100mW/ch,功耗在较低采样率下也能很好地扩展。

ADC3664-xEP 使用串行 LVDS (SLVDS) 接口输出数据,从而最大限度地减少数字互连的数量。该设备支持双通道、单通道和半通道选项。该器件支持–55°C至+105°C的扩展温度范围。

*附件:adc3664-sep.pdf

特性

- 耐辐射(仅限 -SEP):

- 单事件闩锁 (SEL) 免疫高达 LET = 43 MeV-cm2/mg

- 单事件功能中断 (SEFI) 表征高达 LET = 43 MeV-cm2/mg

- 总电离剂量(TID):30krad(Si)

- 增强型产品(-EP 和 -SEP):

- 符合 ASTM E595 释气规范

- 供应商物料图纸 (VID)

- 温度范围:–55°C 至 105°C

- 一个制造、组装和测试站点

- 金键合丝,NiPdAu 引线表面处理

- 晶圆批次可追溯性

- 延长产品生命周期

- 双通道,125MSPS ADC

- 14 位分辨率(无遗漏代码)

- 本底噪声:–156.9dBFS/Hz

- 低功耗:100mW/ch(125MSPS 时)

- 延迟:2 个时钟周期

- 电压基准选项:

- 外部:1 至 125MSPS

- 内部:100 至 125MSPS

- 输入带宽:200MHz (3dB)

- INL:±2.6 LSB;DNL:±0.9 LSB(典型值)

- 片上 DSP(可选/可旁路)

- 抽取 2、4、8、16、32

- 32 位 NCO

- 串行LVDS数字接口(2线、1线和1/2线)

- 小尺寸:40 QFN (5 × 5mm) 封装

- 频谱性能 (fIN = 5MHz):

- 信噪比:77.5dBFS

- SFDR:84dBc HD2、HD3

- SFDR:92dBFS 最差支线

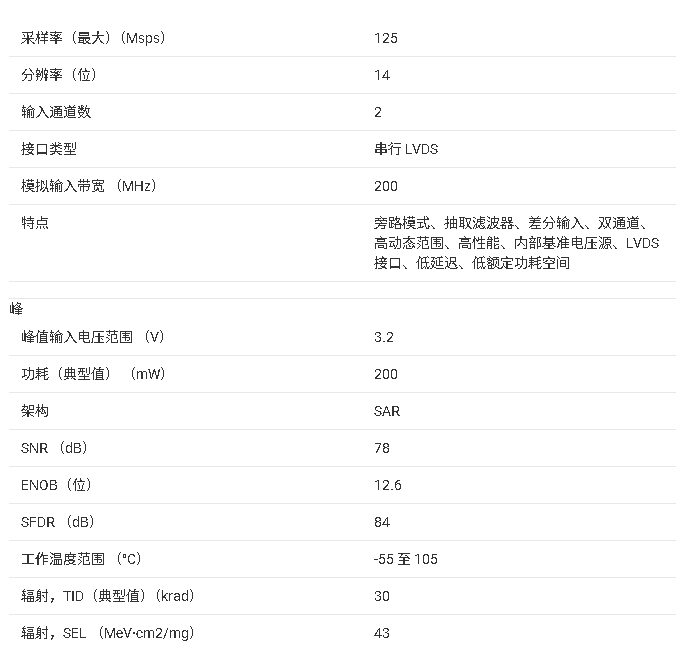

参数

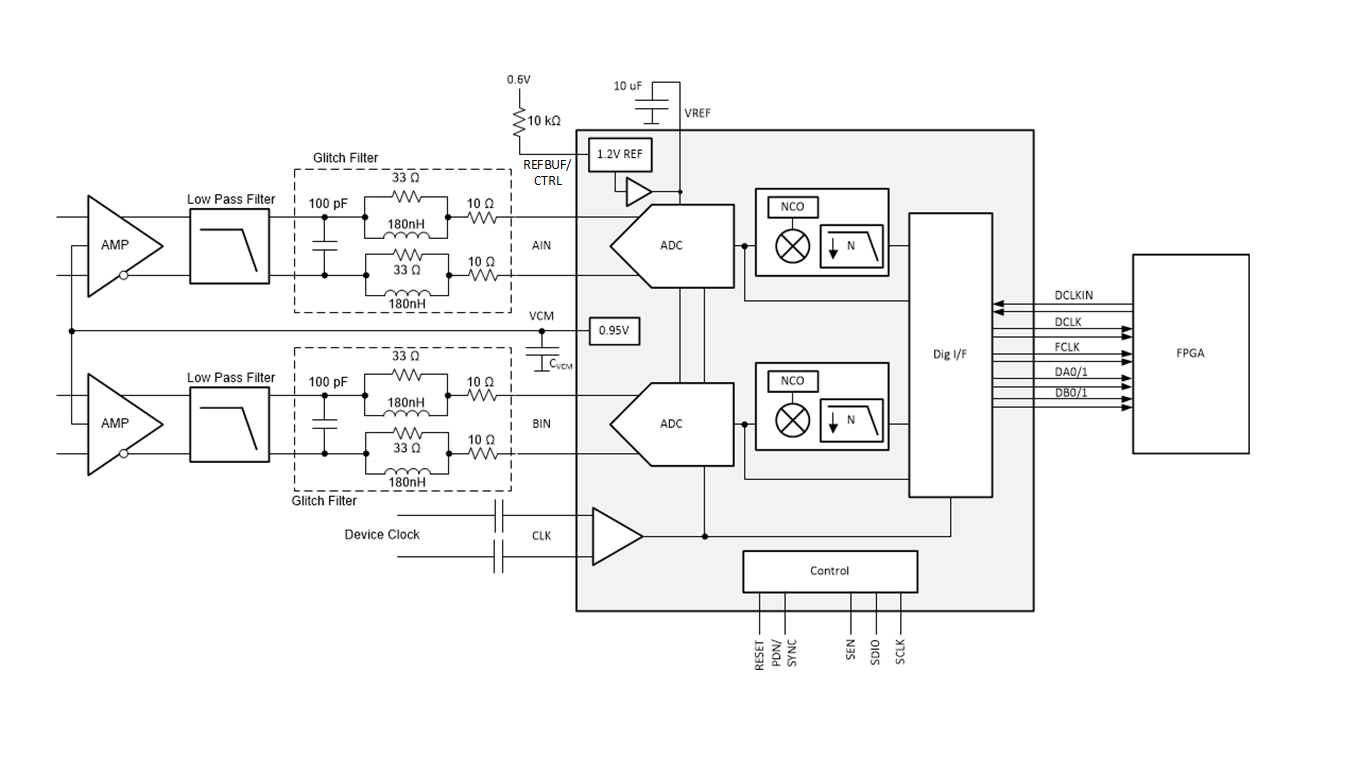

方框图

一、产品基础信息与核心差异

ADC3664-SEP 与 ADC3664-EP 同属 ADC3664-xEP 系列,核心架构均为 14 位双通道同步采样 ADC,共享低功耗、高动态范围特性,主要差异集中在抗辐射能力与应用场景,具体参数对比如下:

| 参数分类 | 参数名称 | ADC3664-EP(增强型) | ADC3664-SEP(抗辐射型) | 系列共同特性 |

|---|---|---|---|---|

| 基础性能 | 抗辐射能力 | 无抗辐射设计 | 1. 单粒子锁定(SEL)免疫:LET≤43 MeV-cm²/mg2. 单粒子功能中断(SEFI):LET≤43 MeV-cm²/mg3. 总电离剂量(TID):30krad (Si) | 1. 14 位分辨率无失码,采样速率 1-125MSPS(外部基准)、100-125MSPS(内部基准)2. 低噪声:噪声谱密度 - 156.9dBFS/Hz,5MHz 输入时 SNR 典型 77.5dBFS、SFDR 典型 92dBFS3. 低功耗:125MSPS 时 100mW / 通道,功耗随采样速率线性降低4. 输入带宽 200MHz(-3dB),支持 IF 采样,适配高频信号采集5. 集成片上数字下变频器(DDC),支持 2/4/8/16/32 倍抽取,32 位 NCO6. 串行 LVDS 接口:支持 2 路、1 路、1/2 路输出模式,输出分辨率 14-20 位可调7. 工作温度范围 - 55°C 至 105°C,封装为 5mm×5mm 40 引脚 WQFN(RSB) |

| 基础性能 | 封装与工艺 | 40 引脚 WQFN(RSB),NiPdAu 引脚镀层,金键合线 | 同 ADC3664-EP,额外满足航天级工艺要求 | |

| 应用场景 | 目标场景 | 工业高速数据采集、通信设备 | 卫星光学通信载荷、卫星成像 / 雷达 / LIDAR 载荷 | |

| 可靠性认证 | 合规标准 | 符合 ASTM E595 释气标准,单一制造 / 组装 / 测试站点 | 除 ADC3664-EP 标准外,满足航天抗辐射标准 |

二、关键功能特性详解

1. 模拟输入与信号调理

1.1 模拟输入特性

- 输入范围与阻抗 :差分输入满量程 3.2Vpp,共模输入电压 0.9-1.0V(典型 0.95V);直流差分输入电阻 8kΩ,输入电容 5.4pF,等效输入网络含采样开关与匹配电阻(如图 7-1 等效输入网络所示),适配高频信号。

- 线性度指标 :全温度范围(-55°C 至 105°C)内,INL 最大 ±7.5LSB(典型 ±2.6LSB)、DNL 最大 ±1.8LSB(典型 ±0.9LSB);增益误差最大 ±3% FSR(内部基准)、±2% FSR(外部基准),温度漂移最大 106ppm/°C(内部基准)、57ppm/°C(外部基准),保障宽温域测量精度。

- 噪声性能 :150Hz 带宽内输入噪声低,5MHz 输入时 THD 典型 - 80dBc,二次 / 三次谐波失真(HD2/HD3)典型 - 84dBc,无杂散动态范围(SFDR)典型 92dBFS,适合弱信号采集。

1.2 基准电压配置

- 内部基准 :默认启用 1.6V 内部基准,需在 VREF 引脚外接 10μF+0.1μF 陶瓷去耦电容,基准温度漂移 6-20ppm/°C,输出阻抗 8Ω,额外消耗 4mA 模拟电流。

- 外部基准 :支持两种外部基准模式:一是直接接入 1.6V 外部基准(VREF 引脚),负载电流 1mA;二是接入 1.2V 外部基准(REFBUF/CTRL 引脚),通过内部增益缓冲放大至 1.6V,负载电流<100μA,需在 REFBUF/CTRL 引脚额外外接 10μF+0.1μF 去耦电容。

2. 数字处理与接口功能设计

2.1 数字下变频器(DDC)

- 抽取与滤波 :支持实抽取(无混频,仅低通滤波)与复抽取(含 NCO 混频),抽取倍数 2/4/8/16/32,复抽取时通带带宽约为采样率的 80%,阻带抑制≥85dB;实抽取通带带宽为复抽取的 1/2,适合不同带宽需求场景。

- NCO 配置 :32 位数控振荡器(NCO),频率范围 - FS/2 至 + FS/2,通过公式 NCO =fNCO ×232**/FS(正频率)或NCO**=**(**f**NCO****+**F**S****)**×**2**32**/**F**S**(负频率)计算配置值,支持相位反转,可通过 SYNC 引脚或寄存器重置相位。

- 数据增益补偿 :复抽取时信号经混频后幅度衰减 6dB,实抽取衰减 3dB,可通过寄存器配置 3dB 或 6dB 数字增益补偿,避免 SNR 损失。

2.2 LVDS 数据接口

- 接口模式 :支持三种输出模式,适配不同数据速率需求:

- 2 路模式:双通道分别从 DA0/DA1(通道 A)、DB0/DB1(通道 B)输出,14 位时序列化倍数 7x,DCLK 频率 = 3.5×FS。

- 1 路模式:双通道数据合并从 DA0/DB0 输出,14 位时序列化倍数 14x,DCLK 频率 = 7×FS。

- 1/2 路模式:双通道数据进一步合并从 DA0 输出,14 位时序列化倍数 28x,DCLK 频率 = 14×FS。

- 输出格式 :支持 14/16/18/20 位输出分辨率,16 位及以上时低位补 0;数据格式可通过寄存器(0x8F/0x92)配置为二进制补码(默认)或偏移二进制,适配不同后端处理需求。

- 时序特性 :延迟低至 1-2 个时钟周期(1/2 路 / 1 路模式 1 周期,2 路模式 2 周期),孔径抖动典型 250fs,确保高速信号采集的实时性。

3. 电源与可靠性设计

3.1 电源配置

- 供电体系 :需双电源供电,模拟电源(AVDD)1.75-1.85V(典型 1.8V),为 ADC 与模拟电路供电;I/O 电源(IOVDD)1.75-1.85V(典型 1.8V),为 LVDS 接口与数字电路供电,无电源上电顺序要求。

- 功耗特性 :125MSPS 时,AVDD 电流典型 64mA(外部基准)、68mA(内部基准),IOVDD 电流典型 47mA(2 路模式);全局掉电模式下功耗仅 12mW,支持单独关闭 ADC 通道、时钟缓冲、基准放大器等模块,灵活平衡功耗与功能。

3.2 可靠性与防护

- ESD 防护 :人体放电模型(HBM)2500V,带电器件模型(CDM)1000V,需遵循 ESD 防护流程操作,避免器件损坏。

- 热性能 :40 引脚 WQFN 封装热阻参数:结到环境(RθJA)30.7°C/W,结到板(RθJB)10.5°C/W,暴露热焊盘需焊接至 PCB 接地平面,确保散热效率。

三、电气规格详情(典型值,TA=25°C,AVDD=IOVDD=1.8V,1.6V 外部基准)

3.1 直流电气参数

| 参数名称 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 差分输入满量程(FS) | - | - | 3.2 | - | Vpp |

| 输入共模电压(VCM) | - | 0.9 | 0.95 | 1.0 | V |

| 输入电阻(RIN) | 直流差分 | - | 8 | - | kΩ |

| 输入电容(CIN) | 直流差分 | - | 5.4 | - | pF |

| 失调误差(VOS_ERR) | - | -55 | ±30 | 55 | LSB |

| 失调漂移(VOS_DRIFT) | - | - | ±0.06 | - | LSB/°C |

| 增益误差(GAIN_ERR) | 外部基准 | - | ±2 | - | %FSR |

| 增益误差(GAIN_ERR) | 内部基准 | - | ±3 | - | %FSR |

| 增益漂移(GAIN_DRIFT) | 外部基准 | - | ±57 | - | ppm/°C |

| 增益漂移(GAIN_DRIFT) | 内部基准 | - | 106 | - | ppm/°C |

3.2 交流电气参数(fIN=5MHz,-1dBFS 输入)

| 参数名称 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 噪声谱密度(NSD) | -20dBFS 输入 | - | -156.9 | - | dBFS/Hz |

| 信噪比(SNR) | 125MSPS | 72 | 77.5 | - | dBFS |

| 信号噪声失真比(SINAD) | 125MSPS | - | 75.7 | - | dBFS |

| 有效位(ENOB) | 125MSPS | - | 12.6 | - | bit |

| 总谐波失真(THD) | 125MSPS | 71.5 | 80 | - | dBc |

| 二次谐波失真(HD2) | 125MSPS | 77 | 84 | - | dBc |

| 三次谐波失真(HD3) | 125MSPS | 73.5 | 84 | - | dBc |

| 无杂散动态范围(SFDR) | 排除 HD2/HD3 | 84 | 92 | - | dBFS |

| 三阶互调失真(IMD3) | f1=10MHz,f2=12MHz | - | 88 | - | dBc |

3.3 时序参数(125MSPS)

| 参数名称 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 孔径延迟(tAD) | - | - | 0.85 | - | ns |

| 孔径抖动(tA) | 方波时钟 | - | 250 | - | fs |

| 恢复时间 | +6dB 过载后 SNR 误差≤1dB | - | 1 | - | 时钟周期 |

| 上电唤醒时间 | 内部基准,带隙使能 | - | 13 | - | μs |

| 数据延迟 | 1/2 路 LVDS | - | 1 | - | 时钟周期 |

| 数据延迟 | 2 路 LVDS | - | 2 | - | 时钟周期 |

四、寄存器配置体系

器件包含 112 个可配置寄存器(地址 0x00-0xFF),核心寄存器按功能分类如下,关键配置需通过 SPI 接口完成(SEN/SCLK/SDIO 引脚):

4.1 基础配置寄存器

| 寄存器地址 | 寄存器名称 | 核心功能 | 关键字段说明 |

|---|---|---|---|

| 0x00 | 复位寄存器 | 器件复位 | - RESET(bit0):1b 时复位所有寄存器,自动清零 |

| 0x07 | 输出接口映射寄存器 | 配置 LVDS 接口模式 | - OP_IF_MAPPER(bit7-5):选择接口映射(如 011=1 路,100=1/2 路)- OP_IF_EN(bit3):使能接口模式切换- OP_IF_SEL(bit2-0):选择输出路数(011=2 路,100=1 路,101=1/2 路) |

| 0x08 | 电源控制寄存器 | 模块掉电控制 | - PDN_CLKBUF(bit5):1b 关闭时钟缓冲- PDN_A/PDN_B(bit2-1):1b 关闭对应 ADC 通道- PDN_GLOBAL(bit0):1b 全局掉电 |

| 0x0E | 基准与时钟配置寄存器 | 基准选择与时钟类型 | - REF_CTRL(bit3):1b 时通过 SPI 选择基准,0b 时通过 REFBUF/CTRL 引脚选择- REF_SEL(bit2-1):00 = 内部基准,01 = 外部 1.2V 基准,10 = 外部 1.6V 基准- SE_CLK_EN(bit0):1b 使能单端时钟,0b 为差分时钟 |

4.2 数字下变频器(DDC)配置寄存器

| 寄存器地址 | 寄存器名称 | 核心功能 | 关键字段说明 |

|---|---|---|---|

| 0x24 | DDC 使能寄存器 | 启用 DDC 与通道复用 | - DDC_EN(bit1):1b 使能 DDC- DIG_BYP(bit2):1b 使能数字功能(含 DDC)- DDC_MUX(bit4-3):配置 ADC 与 DDC 连接(如 11 = 通道 A/B 平均后接入 DDC) |

| 0x25 | 抽取配置寄存器 | 选择抽取倍数与模式 | - DECIMATION(bit6-4):001=2 倍,010=4 倍,…,101=32 倍- REAL_OUT(bit3):1b 实抽取,0b 复抽取- MIX_PHASE(bit0):1b 反转 NCO 相位 |

| 0x26 | 混频增益寄存器 | 补偿混频损失 | - MIX_GAIN_A/B(bit7-6/bit3-2):01=3dB 增益,10=6dB 增益- MIX_RES_A/B(bit5/bit1):1b 重置 NCO 相位并加载新频率- FS/4_MIX_A/B(bit4/bit0):1b 使能 FS/4 混频 |

| 0x2A-0x2D | NCO_A 配置寄存器 | 通道 A NCO 频率 | - NCO_A [31:0]:32 位 NCO 值,按公式计算配置 |

| 0x31-0x34 | NCO_B 配置寄存器 | 通道 B NCO 频率 | - NCO_B [31:0]:32 位 NCO 值,实抽取时自动置 0 |

五、应用设计与布局建议

5.1 典型应用场景

该系列 ADC 主要面向高频、高动态范围数据采集场景,包括:

- 卫星载荷 :卫星光学通信、成像、雷达 / LIDAR 信号采集(ADC3664-SEP 为主)

- 工业设备 :高速数据采集卡、软件无线电(SDR)、超声探伤(ADC3664-EP 为主)

5.1.1 频谱分析仪应用方案

- 电路结构 :单端输入信号经 THS4541 全差分放大器转换为差分信号,通过采样毛刺滤波器(DC-30MHz 时用 33Ω 电阻 + 82nH 电感 + 33pF 电容)与 ADC 输入匹配;时钟采用低抖动差分时钟源,基准选用外部 1.6V 高精度基准(如 REF7040),ADC 输出通过 LVDS 接口连接 FPGA 进行数据处理。

- 关键参数 :输入信号带宽 DC-30MHz,SNR≥75dBFS,THD≤-74dBc,满足高频信号频谱分析需求。

5.2 电源与布局设计要点

5.2.1 电源去耦设计

- 去耦配置 :AVDD 与 IOVDD 引脚均需并联 10μF+0.1μF 陶瓷电容,且靠近引脚布局,避免过孔;推荐电源架构为 “开关电源 + LDO”,开关电源(如 TPS7H4010-SEP)实现高效降压,LDO(如 TPS73801-SEP)进一步滤除噪声,确保模拟电源噪声≤1mVpp。

- 隔离要求 :AVDD 与 IOVDD 需独立布线,避免数字噪声耦合至模拟电路;GND 与 IOGND 需单点连接,形成独立接地平面。

5.2.2 PCB 布局准则

- 差分信号布线 :模拟输入(AINP/AINM、BINP/BINM)与时钟输入(CLKP/CLKM)需采用 100Ω 差分布线,长度差≤5mil,避免过孔;LVDS 输出(DA0/DA0M 等)采用紧密耦合 100Ω 差分布线,长度匹配。

- 基准防护 :VREF 与 REFBUF/CTRL 引脚的去耦电容需紧贴器件,布线长度≤5mm,避免与数字线平行;REFM 引脚直接连接至模拟地,路径阻抗≤1Ω。

- 热设计 :暴露热焊盘(Thermal Pad)需焊接至 PCB 接地平面,通过过孔与内层地连接,确保散热路径通畅,避免结温超过 105°C。

六、封装与订购信息

6.1 封装规格

- 封装类型 :40 引脚 WQFN(型号 RSB),尺寸 5mm×5mm,引脚间距 0.5mm,最大高度 0.8mm,暴露热焊盘(面积约 3.15mm×3.15mm)用于散热,焊盘推荐直径 0.4mm,钢网厚度 0.1mm。

- 焊接要求 :MSL 等级 3(260°C 峰值回流,168 小时湿敏存储),需遵循 JEDEC J-STD-020 标准,热焊盘焊接覆盖率≥75%,确保热性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADC3664 双通道、14位、125MSPS、高信噪比、低功耗ADC技术手册2025-11-01 1236

-

ADC128S102-SEP 技术文档总结2025-10-30 874

-

AFE11612-SEP 技术文档总结2025-10-29 699

-

ADC12DJ5200-SEP 产品技术总结2025-10-28 1362

-

ADC12QJ1600-SEP 技术文档总结2025-10-27 1556

-

ADC3664-SP 辐射加固型双通道模数转换器(ADC)产品文档总结2025-10-23 1395

-

Texas Instruments ADC3664EVMCVAL评估模块数据手册2025-07-09 923

-

ADC3664EVM用户指南2024-11-28 420

-

如果使用FPGA产生采样时钟给ADC3664的话,下图中的原理图需要进行怎样的修改呢?2024-11-20 483

-

ADC3664 14位、125MSPS、低噪声、低功率双通道ADC数据表2024-07-12 547

-

ADC128S102-SEP模数转换器(ADC)数据手册2023-06-19 2108

-

72V3664 数据表2023-03-23 328

-

通信原理公式内容总结2021-05-25 817

全部0条评论

快来发表一下你的评论吧 !