74LS138和与非门设计三人表决器 74LS138设计详解

IC应用电路图

描述

74LS138应当如何和与非门电路设计三人表决器呢?本文将为你详细介绍基于74LS138下的三人表决器设计过程。

74LS138

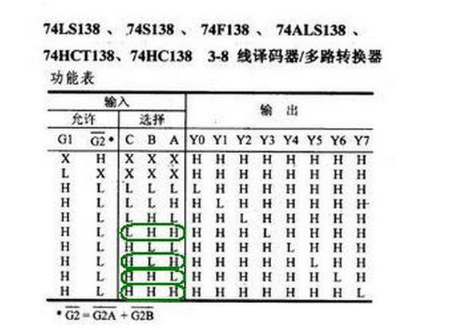

74LS138 为3 线-8线译码器,共有 54LS138和 74LS138 两种线路结构型式。54LS138为军用,74LS138为民用。

74LS138工作原理

①当一个选通端(E1)为高电平,另两个选通端((/E2))和(/E3))为低电平时,可将地址端(A0、A1、A2)的二进制编码在Y0至Y7对应的输出端以低电平译出。(即输出为Y0至Y7的非)比如:A2A1A0=110时,则Y6输出端输出低电平信号。

②利用 E1、E2和E3可级联扩展成 24 线译码器;若外接一个反相器还可级联扩展成 32 线译码器。

③若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

④可用在8086的译码电路中,扩展内存。

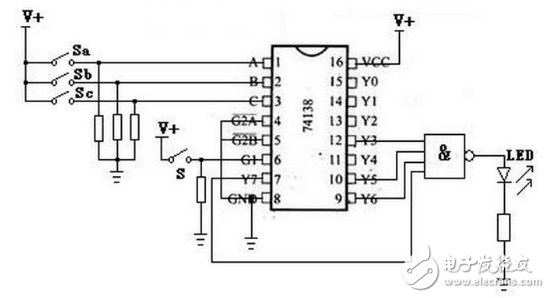

74LS138和与非门设计三人表决器

设Sa,Sb,Sc为三裁判按键,按下=1通过,S为开始键,

真值表中绿色圈为通过组合,通过後LED亮。

74LS138和与非门设计三人表决器工作原理

首先得弄清楚全加器的原理,你这里说的应该是设计1位的全加器。

全加器有3个输入端:a,b,ci;有2个输出端:s,co.

与3-8译码器比较,3-8译码器有3个数据输入端:A,B,C;3个使能端;8个输出端,OUT(0-7)。

这里可以把3-8译码器的3个数据输入端当做全加器的3个输入端,即3-8译码器的输入A、B、C分别对应全加器的输入a,b,ci;将3-8译码器的3个使能端都置为有效电平,保持正常工作;这里关键的就是处理3-8译码的8个输出端与全加器的2个输出的关系。

现在写出全加器和3-8译码器的综合真值表:

(A/a,B/b,C/ci为全加器和译码器的输入,OUT为译码器的输出(0-7),s为加法器的和,co为加法器的进位输出)PS:假定译码器的输出为高电平有效。

A/a B/b C/ci OUT s co

0 0 0 0 0 0

0 0 1 1 1 0

0 1 0 2 1 0

0 1 1 3 0 1

1 0 0 4 1 0

1 0 1 5 0 1

1 1 0 6 0 1

1 1 1 7 1 1

根据上面的真值表,可以设计出电路图:

将3-8译码器的输出OUT(1、2、4、7)作为一个4输入的或门的输入,或门的输出作为加法器的和;将3-8译码器的输出OUT(3、5、6、7)作为一个4输入的或门的输入,或门的输出作为加法器的进位输出。即完成了加法器的设计。

回过头来分析:

当加法器的输入分别为:a=1,b=0,ci=1时,对应3-8译码器的输入为A=1,B=0,C=1,这是译码器对应的输出为OUT(5)=1,其余的为0,根据上面设计的连接关系,s=0,co=1,满足全加器的功能,举其他的例子也一样,所以,设计全加器的设计正确。

结语

在三人表决器的设计中,如果数字系统简单,可以采用门电路;如果数字系统复杂,则可以采用译码器、数据选择器和加法器比较好。关于74LS138和与非门设计三人表决器的介绍就到这里了,希望本文能够帮到你。

-

基于8051的Proteus仿真-74LS138译码器应用2022-05-11 3513

-

74LS138译码器的扩展方法是什么2022-01-19 6617

-

如何对74LS138译码进行实验2021-07-14 6954

-

74ls138应用电路图大全(五款74ls138全加器电路/抢答器电路/三人表决器电路)2018-05-04 122455

-

74LS153实现三人表决电路(4种方式实现3人表决电路)2018-01-26 399644

-

74ls138中文资料详解2017-11-03 70887

-

74hc138和74ls138的区别2017-10-31 50650

-

74LS138英文手册2016-11-22 1354

-

74LS138 英版数据手册2016-08-29 1564

-

74LS1382016-04-29 4211

-

74ls138真值表_74ls138功能表2011-03-20 10668

-

74ls138译码器内部电路逻辑图功能表简单应用2009-07-13 68026

-

74ls138引脚图-74ls138管脚图及功能真值表2007-12-17 194494

全部0条评论

快来发表一下你的评论吧 !