ADS127L14/ADS127L18 ADC 产品文档总结

描述

ADS127L14(四通道)和ADS127L18(八进制)是基于单通道ADS127L11的24位、增量Σ(ΔΣ)模数转换器(ADC)。这些器件提供4个或8个通道的同步采样,数据速率高达512kSPS(宽带滤波器模式)和1365kSPS(低延迟滤波器模式)。

*附件:ads127l14.pdf

特性

- 同时测量四个或八个通道

- 宽带滤波器模式:高达 512kSPS

- 低延迟滤波模式:高达 1365kSPS

- 功率可扩展速度模式:

- 最大速度:512kSPS

- 83mW (ADS127L14)

- 165mW (ADS127L18)

- 高速:400kSPS

- 64mW (ADS127L14)

- 128mW (ADS127L18)

- 中速:200kSPS

- 37mW (ADS127L14)

- 74mW (ADS127L18)

- 低速:50kSPS

- 12mW (ADS127L14)

- 24mW (ADS127L18)

- 最大速度:512kSPS

- 具有直流精度的交流性能:(高速模式)

- 200kSPS时的动态范围:112dB(典型值)

- 总谐失真:–118dB(典型值)

- INL:1ppm FSR(典型值)

- 失调漂移:10nV/°C(典型值)

- 增益漂移:0.5ppm/°C(典型值)

- 预充电缓冲信号输入

- 可通过引脚设置或 SPI 进行编程

- 用于输出数据的帧同步端口

- 内部或外部时钟作

- 模拟电源电压:2.85V 至 5.5V

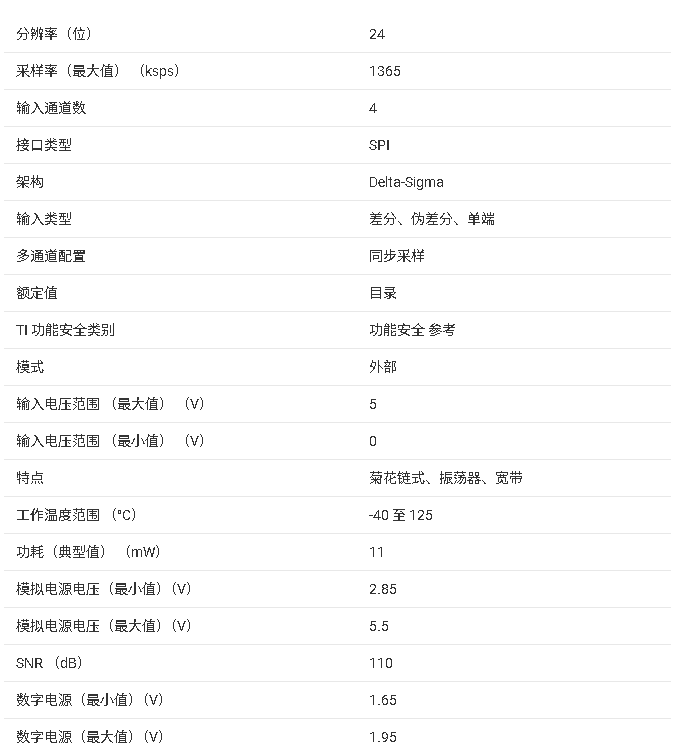

参数

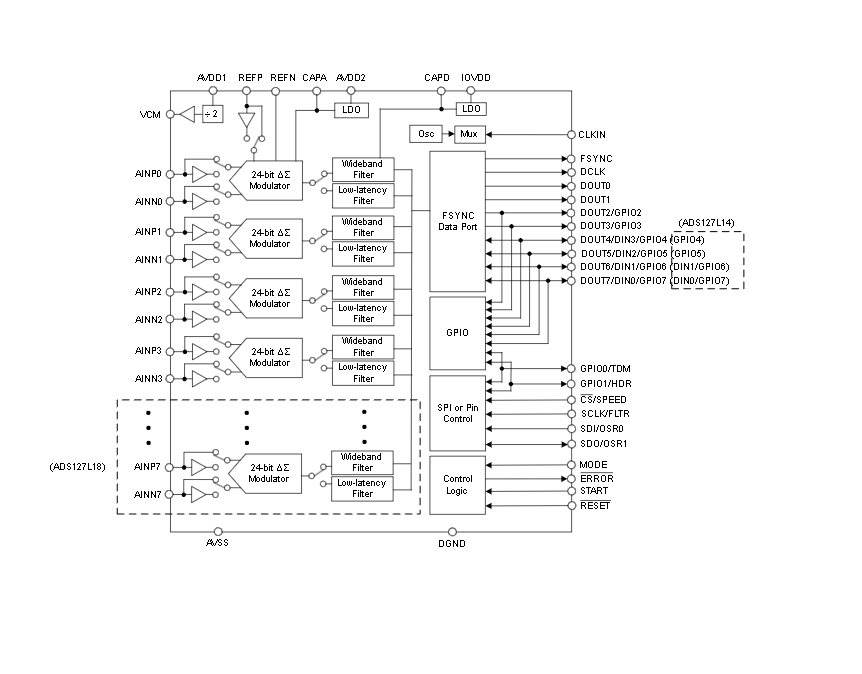

方框图

一、产品概述

ADS127L14(四通道)与 ADS127L18(八通道)是德州仪器推出的 24 位 delta-sigma(ΔΣ)架构模数转换器(ADC),核心优势为 多通道同步采样 、 高分辨率与宽信号带宽平衡 、 功率可缩放 ,适用于高精度数据采集场景。两款产品封装与核心架构一致,仅通道数量差异,均支持 - 40°C 至 + 125°C 工业级工作温度,满足测试测量、工厂自动化、航空航天、医疗等领域需求。

二、核心参数对比

两款产品核心差异为通道数量,关键性能参数一致,具体如下:

| 参数 | ADS127L14(四通道) | ADS127L18(八通道) | 备注 |

|---|---|---|---|

| 分辨率 | 24 位(无失码) | 24 位(无失码) | 支持 16 位 / 24 位输出分辨率切换 |

| 采样速率 | 宽带滤波模式:最高 512kSPS;低延迟滤波模式:最高 1365kSPS | 同左 | 采样速率随速度模式与过采样率(OSR)可调 |

| 功耗(典型值) | 最高速模式:83mW;低速模式:12mW | 最高速模式:165mW;低速模式:24mW | 功率随速度模式线性缩放 |

| 动态范围(DR) | 高速模式 200kSPS 下:112dB | 同左 | 宽带滤波模式,OSR=64 |

| 总谐波失真(THD) | 高速模式 1kHz 输入:-118dB | 同左 | 1x 输入范围,V_REF=4.096V |

| 积分非线性(INL) | ±1ppm of FSR | 同左 | 全温度范围典型值 |

| 输入带宽 | 宽带滤波模式 - 3dB 带宽:0.4374×f_DATA | 同左 | f_DATA 为输出数据率 |

| 电源电压 | 模拟:2.85V-5.5V(AVDD1);数字:1.8V(IOVDD) | 同左 | 支持单极性(如 5V/0V)或双极性(如 ±2.5V)供电 |

三、硬件设计关键信息

1. 封装与引脚

- 封装类型 :均采用 56 引脚 VQFN(RSH 封装),尺寸 7mm×7mm,暴露热焊盘需接地以保证散热(热阻 RθJA=23.5°C/W)。

- 关键引脚功能 :

- 模拟输入:AINPn/AINNn(n=0-3/7,通道正负端),支持差分输入,需匹配 VCMOUT 共模电压(典型为 (AVDD1+AVSS)/2)。

- 电源:AVDD1(模拟主电源)、AVDD2(模拟辅助电源)、IOVDD(数字 I/O 电源)、AVSS(模拟地),需按要求搭配 2.2μF/10μF X7R 陶瓷去耦电容。

- 基准与共模:REFP/REFN(基准电压正负端,支持 0.5V-5V 差分输入)、VCM(共模电压输出,需接 1μF 去耦电容)。

- 时钟与数据:CLKIN(外部时钟输入)、FSYNC(帧同步信号)、DCLK(数据时钟)、DOUTx/DINx(差分数据 I/O,支持菊花链)。

- 配置引脚:MODE(选择硬件 / SPI 配置)、SCLK/SDI/SDO(SPI 配置接口)、START/RESET(同步 / 复位控制)。

2. 电源与基准设计

- 电源要求 :

- 单极性供电:AVDD1=5V、AVSS=0V;双极性供电:AVDD1=2.5V、AVSS=-2.5V,AVDD2 可接 AVDD1 或独立降压(1.8V-5V)以降低功耗。

- 去耦电容:AVDD1/AVDD2/IOVDD 需就近接 2.2μF 去耦电容,CAPA(模拟稳压器输出)接 10μF 电容,REFP/REFN 接 2.2μF(缓冲开启)或 10μF(缓冲关闭)电容。

- 基准选择 :

- 内置无基准,需外接差分基准(推荐 REF6041 4.096V),支持低基准范围(0.5V-2.75V)与高基准范围(1V-AVDD1-AVSS)。

- 基准缓冲:REFP 引脚可开启预充电缓冲(REG_CFG1 寄存器控制),降低基准输入电流(典型 ±3μA),减少基准驱动带宽需求。

四、核心功能与配置

1. 采样与滤波

- 同步采样 :所有通道严格同步采样,支持多芯片菊花链同步(通过 START 引脚或 SPI 命令),同步后滤波需 68 个数据周期稳定(宽带滤波)。

- 双滤波模式 :

- 宽带滤波 :线性相位 FIR 架构,通带纹波 ±0.0004dB,阻带衰减 106dB,适合 AC 信号测量,支持 OSR=32-4096,数据率 512kSPS(最高速)-0.39kSPS(低速)。

- 低延迟滤波 :CIC(sinc)架构,支持 sinc4、sinc4+sinc1、sinc3、sinc3+sinc1 四种配置,延迟低至 3.9μs(最高速模式),适合 DC 信号快速采集,数据率最高 1365kSPS。

- 过采样(OSR) :可编程 OSR=12-4096,OSR 提升可降低噪声(如 OSR=4096 时动态范围达 139dB),输出数据率 = f_MOD/OSR(f_MOD= f_CLK/2)。

2. 数据接口与传输

- 帧同步(Frame-Sync)接口 :

- 支持 1/2/4/8 车道(TDM 时分复用),DOUTx 引脚可切换为 GPIO 或菊花链 DINx 输入,数据帧含可选 STATUS 头字节(通道状态)与 CRC 字节(错误检测)。

- 数据格式:24 位二进制补码(默认)或 16 位左对齐,MSB 优先,支持数据重复或菊花链级联(多芯片扩展通道)。

- SPI 配置接口 :

- 支持 SPI 模式 1(CPOL=0, CPHA=1),可通过 SPI 或硬件引脚配置(MODE 引脚选择),寄存器分全局配置(时钟、电源)与通道配置(滤波、增益)。

- 错误检测:支持 SPI CRC(8 位)、寄存器映射 CRC(16 位)、时钟计数错误、地址越界检测,ERROR 引脚(开漏)指示错误状态。

3. 校准与诊断

- 校准功能 :

- 偏移校准:每通道 24 位偏移寄存器(CHn_OFS),支持 ±16LSB 微调,校准值以二进制补码存储,在增益校准前生效。

- 增益校准:每通道 24 位增益寄存器(CHn_GAN),默认 400000h(增益 = 1),校准值以无符号二进制存储,公式:

校准后数据=(原始数据-偏移)×增益/400000h。

- 诊断功能 :

- 温度监测:无内置温度传感器,可通过输入短接测噪声漂移间接判断温度影响。

- 自测试:输入多路器支持短路(测偏移 / 噪声)、全量程(测增益)、共模(测 CMRR)测试模式,通过 CHn_CFG1 寄存器配置。

- 电源监测:ALV_FLAG(模拟欠压)、POR_FLAG(上电复位)监测电源状态,ERROR 引脚同步指示。

4. 功率与速度模式

四档速度模式 :通过 GEN_CFG2 寄存器选择,速度与功耗线性匹配:

速度模式 f_CLK 最高采样率(宽带滤波) 功耗(ADS127L14) 最高速 32.768MHz 512kSPS 83mW 高速 25.6MHz 400kSPS 64mW 中速 12.8MHz 200kSPS 37mW 低速 3.2MHz 50kSPS 12mW 省电模式 :通道可独立断电(CHn_CFG2 寄存器),断电后输出最后一次有效数据;待机模式(STBY_MODE)停止采样,功耗降低 50% 以上。

五、应用设计与布局

1. 典型应用

- 信号链设计 :输入需搭配抗混叠滤波器(推荐 THS4551 全差分放大器),四阶滤波器可实现 12.8MHz(f_MOD)处 90dB 衰减,避免信号混叠。

- 多通道扩展 :通过菊花链级联(DOUTx 接下一片 DINx),支持最多 32 片级联,需同步 CLKIN 与 START 信号,DCLK 频率需满足

f_DCLK ≥ f_DATA×TDM比×数据包长度。

2. PCB 布局准则

- 分层设计 :至少 4 层板,内层为地与电源平面,模拟地(AVSS)与数字地(DGND)单点连接(ADC 处),避免数字噪声串扰。

- 布线要求 :

- 模拟输入(AINPn/AINNn)采用等长差分对布线,远离数字线(如 SCLK、DCLK)。

- 时钟线(CLKIN)需短且阻抗匹配(串 10Ω 电阻),避免与其他时钟线平行。

- 电源平面:AVDD1/AVDD2/IOVDD 独立平面,热焊盘需大面积接地,降低热阻。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS127L11磁场升高的时候ADC损坏,为什么?2024-11-18 406

-

ADS127L11和ADS127L01相比主要突出的特点有哪些?2024-11-25 614

-

ADS127L01采样数据不准确是哪里的问题?2024-12-13 600

-

ADS127L11资料介绍2022-11-04 730

-

理解和运用ADS127L11EVM GUI中的Histogram Analysis2022-10-28 774

-

ADS127L11 400kSPS、宽带宽、24位、Δ-Σ ADC数据表2024-07-15 634

-

THP210和ADS127L11性能2024-08-27 624

-

ADS127L21EVM-PDK评估模块2024-11-06 708

-

Texas Instruments ADS127L18 24 位模数转换器数据手册2025-07-10 1522

-

Texas Instruments ADS127L18EVM-PDK 评估模块(EVM)数据手册2025-07-24 943

-

ADS127L21EVM-PDK评估套件技术解析与应用指南2025-08-20 1491

-

ADS117L14/ADS117L18 核心信息总结2025-10-22 906

-

ADS127L18四通道 / 八通道同步采样 24 位 ADC 产品文档总结2025-10-23 1149

-

ADS127L21B 产品技术文档总结2025-10-24 1010

-

ADS127L01 24 位高速宽带 ADC 核心信息总结2025-11-10 1054

全部0条评论

快来发表一下你的评论吧 !