ADC3569 单通道高速模数转换器(ADC)产品文档总结

描述

ADC3568和ADC3569 (ADC356x) 是 16 位、250MSPS 和 500MSPS、单通道模数转换器 (ADC)。这些器件专为高信噪比 (SNR) 而设计,可提供 -160dBFS/Hz (500MSPS) 的噪声频谱密度。

高能效ADC架构在500MSPS时功耗为435mW,并以较低的采样率(250MSPS时为369mW)提供功率缩放。

*附件:adc3569.pdf

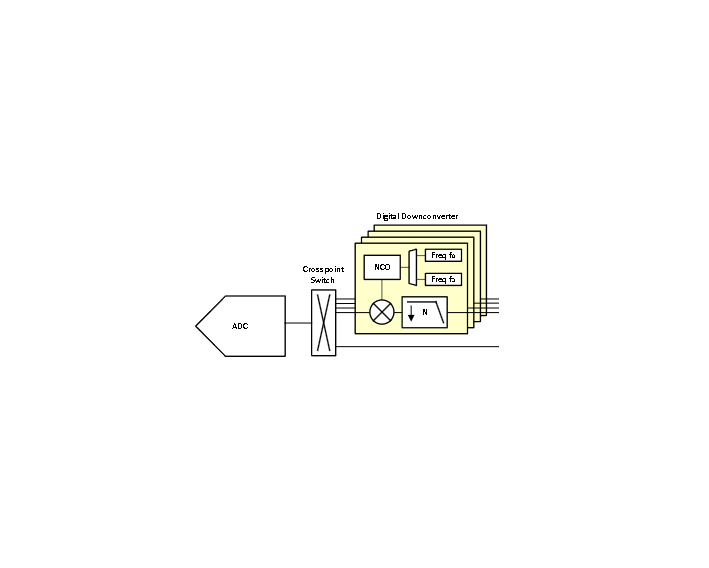

ADC356x包括一个可选的四频数字下变频器(DDC),支持2倍的宽带抽取到32768的窄带抽取。DDC 使用 48 位 NCO,支持相位相干和相位连续跳频。

ADC356x 配备了灵活的 LVDS 接口。在抽取旁路模式下,器件使用并行 SDR 或 DDR LVDS 接口。使用抽取时,输出数据使用串行LVDS接口传输,随着抽取的增加,所需的通道数量减少。对于高抽取比,输出分辨率可以提高到32位。

特性

- 16 位、单通道 250 和 500MSPS ADC

- 噪声频谱密度:−160.4dBFS/Hz

- 热噪声:76.4dBFS

- 单核(非交错)ADC架构

- 功耗:

- 435mW (500MSPS)

- 369mW (250MSPS)

- 光圈抖动:75fs

- 缓冲模拟输入

- 可编程 100Ω 和 200Ω 端接

- 输入满量程:2VPP

- 全功率输入带宽(−3dB):1.4GHz

- 频谱性能(fIN = 70MHz,−1dBFS):

- 信噪比:75.6dBFS

- SFDR HD2,3:80dBc

- SFDR 最差杂散:94dBFS

- INL:±2 LSB(典型值)

- DNL:±0.5 LSB(典型值)

- 数字下变频器 (DDC)

- 多达四个独立的 DDC

- 复杂而真实的抽取

- 抽取:/2、/4 到 /32768 抽取

- 48 位 NCO 相位相干跳频

- 并行/串行 LVDS 接口

- 用于 DDC 旁路的 16 位并行 SDR、DDR LVDS

- 用于抽取的串行LVDS

- 32 位输出选项,用于高抽取

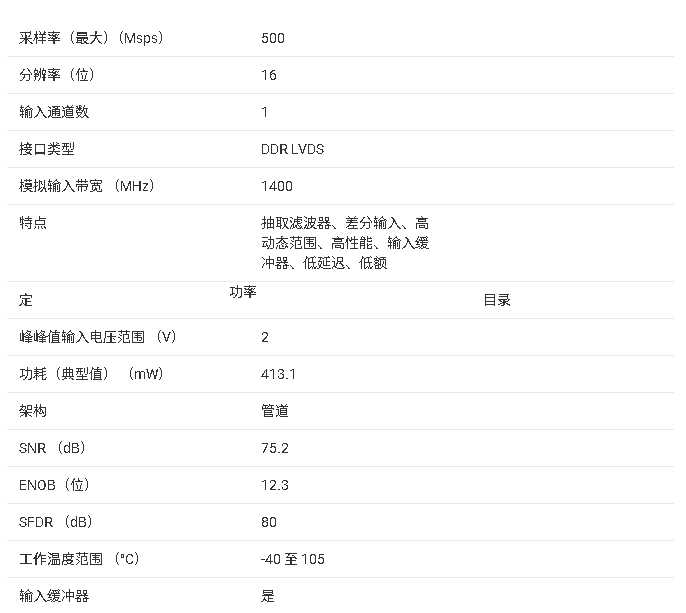

参数

方框图

一、产品概述

ADC3568 与 ADC3569(统称 ADC356x)是德州仪器推出的 单通道 16 位高速模数转换器 ,核心优势为高分辨率、低噪声、宽输入带宽与灵活数字下变频(DDC)功能,专为软件定义无线电(SDR)、频谱分析仪、雷达、光谱学、功率放大器线性化及通信基础设施等高精度信号处理场景设计。两款器件仅采样率差异:ADC3568 最高 250MSPS,ADC3569 最高 500MSPS,均采用 9mm×9mm 64 引脚 VQFN(RTD 封装),支持 - 40°C 至 + 105°C 宽温工作,兼具高性能与功率效率(250MSPS 功耗 369mW,500MSPS 功耗 435mW)。

二、核心参数与性能

| 参数 | ADC3568(250MSPS) | ADC3569(500MSPS) | 备注 |

|---|---|---|---|

| 核心性能 | 16 位分辨率,无失码;积分非线性(INL)±2LSB,微分非线性(DNL)±0.5LSB | 16 位分辨率,无失码;INL±2LSB,DNL±0.5LSB | 高线性度保障信号幅度与相位精度,适配雷达、频谱分析等高精度场景 |

| 噪声与动态性能 | 噪声谱密度(NSD)-157.4dBFS/Hz;信噪比(SNR)75.2dBFS(f_IN=70MHz);无杂散动态范围(SFDR)85dBc(HD2/HD3)、96dBc(非 HD2/HD3) | NSD-160.4dBFS/Hz;SNR75.6dBFS(f_IN=70MHz);SFDR82dBc(HD2/HD3)、94dBc(非 HD2/HD3) | 低噪声特性适配微弱信号采集(如通信接收信号) |

| 输入特性 | 输入带宽 1.4GHz(-3dB)、输入满量程 2VPP、共模电压 1.4V;内置 100Ω/200Ω 可编程端接 | 同 ADC3568 | 宽输入带宽支持高频信号直接采样,无需前端降频 |

| 时钟性能 | 采样时钟频率 100-250MHz,差分输入(0.5-2.4VPP)、共模电压 0.75V;孔径抖动 75fs | 采样时钟频率 100-500MHz,其余同 ADC3568 | 低抖动时钟保障高频采样动态性能 |

| 数字下变频(DDC) | 支持 1-4 个独立 DDC,实 / 复抽取(2x-32768x),48 位 NCO(相位连续 / 相干跳频) | 同 ADC3568 | 灵活抽取降低后端数据率,NCO 支持精准频率混频 |

| 接口与功耗 | 并行 SDR/DDR LVDS(16 位)、串行 LVDS(SLVDS,16/32 位);功耗 369mW | 同接口类型;功耗 435mW | 多接口模式适配不同数据传输需求,低功耗适配便携设备 |

三、硬件设计关键信息

1. 封装与引脚

- 封装类型 :64 引脚 VQFN(RTD),尺寸 9mm×9mm,暴露热焊盘(背面 GND PAD)需接地以保障散热(热阻 RθJA=22.3°C/W,RθJC=1.1°C/W),焊接时热焊盘需与地平面可靠连接,焊接面积≥7mm×7mm。

- 关键引脚功能 :

- 模拟输入:AINP/AINM(单通道差分输入,支持 100Ω/200Ω 内置端接)、VCM(共模电压输出,1.4V,供模拟输入偏置)。

- 电源:AVDD12(1.2V 模拟电源)、AVDD18(1.8V 模拟电源)、DVDD12(1.2V 数字电源)、DVDD18(1.8V 数字接口电源)、AGND/CLKGND/DGND(对应地,需单点共地)。

- 时钟与同步:CLKP/CLKM(差分采样时钟输入,AC 耦合推荐)、DCLKINP/DCLKINM(接口时钟输入,内置 100Ω 端接)、DCLKP/DCLKM(数据输出时钟)、FCLKP/FCLKM(帧时钟输出)、GPIO0/GPIO1(同步 / 控制复用引脚)、RESET(硬件复位,高有效)。

- 数据与控制:DOUT0P/DOUT0M 至 DOUT15P/DOUT15M(16 组 LVDS 数据输出)、SPI 接口(SEN/SCLK/SDIO,配置寄存器)。

2. 电源与信号设计要求

- 电源设计 :

- 供电序列:需按 “DVDD12→AVDD12→AVDD18/DVDD18” 顺序供电,避免电压冲击导致模拟电路损坏;掉电时按逆序操作。

- 去耦设计:AVDD12/AVDD18/DVDD12/DVDD18 引脚需就近布置 0.1μF 陶瓷电容 + 10μF 钽电容,VCM 引脚需外接 0.1μF 电容滤波;推荐搭配低噪声 LDO(如 TPS7A8400)进一步抑制电源噪声,模拟电源与数字电源需独立供电,避免串扰。

- 信号设计 :

- 模拟输入:需差分布线,阻抗匹配(50Ω),长度匹配误差 <5mil;AC 耦合时通过 VCM 引脚提供 1.4V 共模偏置,DC 耦合时需由前端放大器(如 LMH5485)提供共模电压;高频输入(>500MHz)需添加 RCR 滤波网络(10Ω+1pF)抑制采样毛刺。

- 时钟输入:差分时钟需 AC 耦合,单端时钟需将 CLKM 接地;时钟占空比 35%-65%,抖动 < 75fs,避免采样相位误差影响动态性能。

- LVDS 输出:需差分布线,阻抗 100Ω,远离模拟输入线(间距≥2mm),长度匹配误差 < 10mil,减少数字噪声串扰。

四、核心功能与配置

1. 高带宽模拟前端

- 宽输入带宽 :1.4GHz(-3dB)全功率带宽,支持高频信号直接采样(如 500MHz 以下射频信号),无需前端混频器,简化系统设计;输入阻抗 100Ω/200Ω 可编程,适配不同源阻抗场景(如 50Ω 射频前端)。

- 低噪声采样 :采用非交错单核心架构,避免通道失配导致的杂散;孔径抖动 75fs,保障高频采样时的 SNR 性能(如 500MSPS 采样 70MHz 信号时 SNR 仍达 75.6dBFS)。

2. 灵活数字下变频(DDC)

- 多通道 DDC :支持 1-4 个独立 DDC,实信号 / 复信号抽取(抽取因子 2x-32768x),复抽取时通带带宽约 0.8×Fs/N,实抽取时约 0.4×Fs/N(N 为抽取因子),可大幅降低后端 FPGA / 处理器数据处理压力(如 500MSPS 抽取 32 倍后数据率降至 15.625MSPS)。

- 48 位 NCO :每路 DDC 配备 48 位数控振荡器(NCO),支持相位连续与无限相位相干跳频,频率分辨率达 Fs/2⁴⁸(500MSPS 时约 0.001Hz),可实现精准频率混频(如将 700MHz 信号混频至基带),SFDR≥100dBc,无杂散干扰。

3. 多模式数字接口

- 并行 LVDS :DDC 旁路时支持 SDR(单沿采样)/DDR(双沿采样)模式,16 位数据通过 16 组 LVDS lane 输出,SDR 模式时钟速率等于采样率,DDR 模式时钟速率为采样率 1/2,适配高速无抽取场景(如实时雷达信号采集)。

- 串行 LVDS(SLVDS) :启用 DDC 时自动切换为 SLVDS,数据序列化后通过 fewer lane 输出(如抽取 8 倍时仅需 1 组 lane),支持 16 位 / 32 位输出分辨率(高抽取时推荐 32 位以避免量化噪声损失),帧时钟(FCLK)标记数据帧起始 / 结束。

- 输出控制 :支持输出数据格式(二进制补码 / 偏移二进制)、数据极性反转、 lane 映射(冗余 / 修复)、测试图案(斜坡 / 固定图案),便于系统调试与校准。

4. 低延迟与功耗优化

- 低延迟模式 :旁路数字纠错与 DDC 等模块, latency 降至 9 时钟周期(仅 DDR LVDS 支持),适配高速控制环场景(如功率放大器线性化),但 AC 性能略有下降(SNR 降低约 2dB)。

- 功耗 scaling :功耗随采样率线性降低(如 ADC3569 从 500MSPS 降至 250MSPS 时功耗从 435mW 降至 369mW),全局掉电模式功耗仅 30mW,适配电池供电设备。

五、应用设计与布局

1. 典型应用场景

- 宽带频谱分析仪 :采用 ADC3569(500MSPS),输入经巴伦变压器(如 Marki BAL-0009SMG)转换为差分信号,通过 RCR 滤波网络接入 AINP/AINM,启用 4 路 DDC 实现多频段并行采集(如同时监测 100MHz/200MHz/300MHz/400MHz 频段),SLVDS 输出至 FPGA 进行频谱分析,SNR75.6dBFS 保障微弱信号检测。

- 软件定义无线电(SDR) :选用 ADC3568(250MSPS),配合射频前端实现 200MHz 以下信号直接采样,DDC 抽取 8 倍后数据率降至 31.25MSPS,通过 SPI 配置 NCO 实现频率跳变(如从 100MHz 跳至 150MHz),适配多频段通信接收。

2. PCB 布局准则

- 分区设计 :模拟区(AINP/AINM、CLKP/CLKM、VCM)、数字区(LVDS 输出、SPI)、电源区严格分离,模拟地 / 数字地 / 时钟地仅在热焊盘处单点连接;数字信号线与模拟输入线间距≥2mm,避免串扰。

- 布线要求 :

- 模拟输入:差分对布线,长度 <10cm,避免过孔;高频输入(>500MHz)需缩短至 5cm 内,添加 RCR 滤波网络。

- 时钟输入:差分时钟线长度匹配误差 < 2mil,单端时钟线靠近地平面;时钟线与模拟输入线间距≥3mm,减少相位噪声耦合。

- LVDS 输出:差分对布线,长度匹配误差 < 10mil,每对 lane 远离模拟区域,末端接 100Ω 匹配电阻。

- 热设计 :暴露热焊盘通过至少 8 个 0.3mm 孔径过孔连接至地平面,热焊盘周围预留 1mm 散热铜皮,避免高温导致性能退化(结温≤115°C)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

解析ADC3568与ADC3569:高精度单通道ADC的卓越之选2026-01-26 609

-

ADC121S101 模数转换器技术规格与应用总结2025-11-17 714

-

ADC3568/ADC3569 ADC 产品文档总结2025-10-23 961

-

ADC14X250单片单通道高性能模数转换器数据表2024-07-18 540

-

ADC083000单通道、低功耗、高性能CMOS模数转换器数据表2024-07-17 555

-

ADC09xJ1300四通道/双通道/单通道1.3GSPS 9位模数转换器(ADC)数据表2024-07-15 510

-

模数转换器ADC简介2022-02-17 1790

-

EVAL-AD7853CB评估板采用AD7853SPS单通道,采样delta模数转换器2020-05-22 2874

-

电流积分模数转换器(ADC),什么是电流积分模数转换器(AD2010-03-24 3651

全部0条评论

快来发表一下你的评论吧 !