ADS127L21B 产品技术文档总结

描述

该ADS127L21B是一款高精度、24位、Δ-Σ(Δσ)、模数转换器(ADC),具有可编程数字滤波器。该数字滤波器使用宽带滤波器的数据速率高达 512kSPS,使用低延迟滤波器的数据速率高达 1365kSPS。该器件提供了交流性能和直流精度的完美组合,功耗低。

低漂移调制器实现了出色的直流精度,最大 0.8ppm INL(0°C 至 70°C),以及出色的交流性能和低宽带噪声。功耗可扩展架构具有四种速度模式,可优化数据速率、分辨率和功耗。信号和基准输入缓冲器可减少驱动器负载,从而提高精度。

*附件:ads127l21b.pdf

可编程无限和有限脉冲响应(IIR 和 FIR)数字滤波器允许自定义滤波器配置文件,例如 A 加权补偿和频率陷波滤波器。宽带或低延迟滤波器选项可在一台器件中优化交流信号性能或直流信号的数据吞吐量。

串行接口具有菊花链功能,可减少隔离栅上的信号线数量。SPI输入数据和寄存器存储器内容通过循环冗余校验(CRC)进行验证,以提高运行可靠性。

小型 3mm × 3mm WQFN 封装专为空间有限的应用而设计。该器件完全额定工作在–40°C至+125°C温度范围内,并且与ADS127L21引脚兼容。

特性

- 具有直流精度的交流性能:

- 动态范围 (200kSPS):111.5dB(典型值)

- INL:0.2ppm 的 FSR(典型值)

- 总谐波差:–125dB(典型值)

- 失调漂移:50nV/°C(典型值)

- 增益漂移:0.5ppm/°C(典型值)

- 功率可扩展速度模式:

- 最大速度:512kSPS(典型值 33mW)

- 高速:400kSPS(典型值为 26mW)

- 中速:200kSPS(典型值 14mW)

- 低速:50kSPS(典型值 4.3mW)

- 宽带或低延迟滤波器模式

- 可编程数据速率:

- 宽带滤波器模式:512kSPS

- 低延迟滤波模式:1.365MSPS

- 可编程 IIR 和 FIR 数字滤波器

- 缓冲输入

- 1.5μA典型输入电流,中速模式

- 输入范围:±VREF 或 ±2VREF

- 内部或外部时钟作

- 转换延迟(低延迟过滤器):3μs

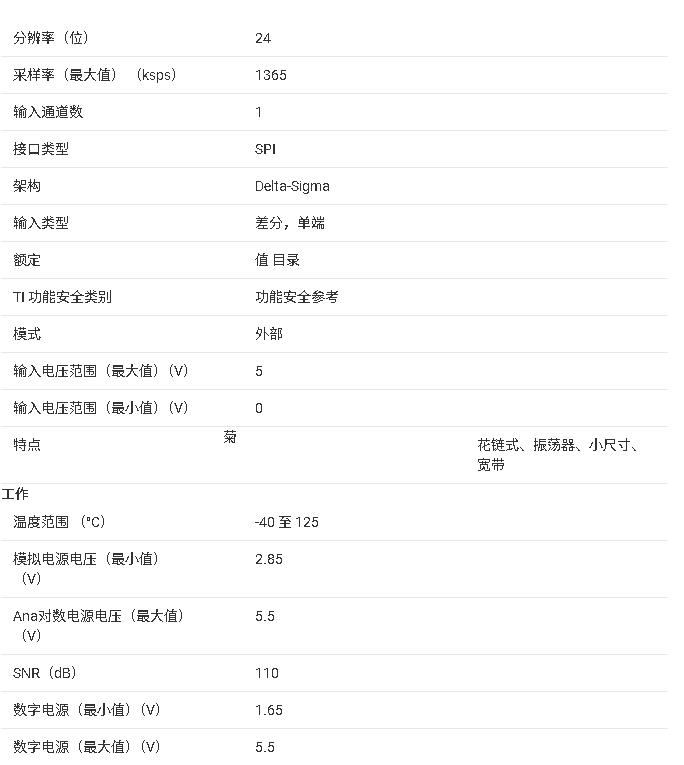

参数

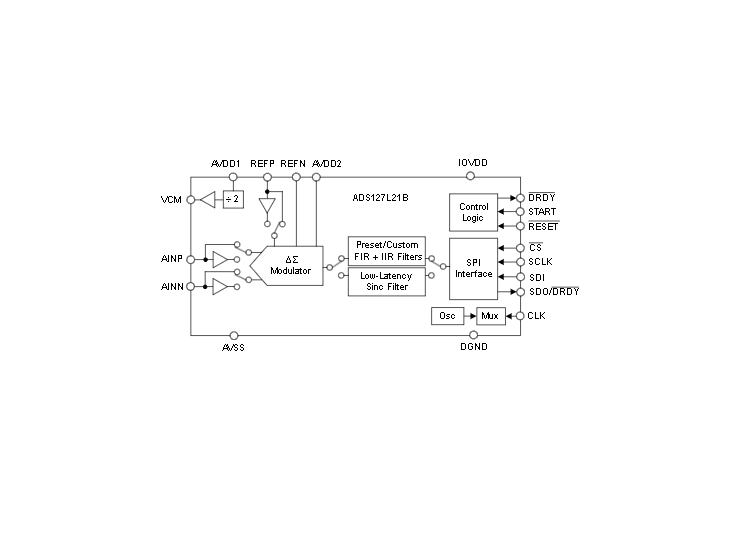

方框图

一、核心特性

1. 性能指标

AC 与 DC 精度 :动态范围(200kSPS 时)典型值 111.5dB,积分非线性(INL)典型值 0.2ppm FSR,总谐波失真(THD)典型值 - 125dB;温漂特性优异,失调漂移典型值 50nV/°C,增益漂移典型值 0.5ppm/°C。

速度与功耗平衡 :支持 4 种功耗可扩展速度模式,兼顾数据率与功耗需求,具体参数如下:

速度模式 最大数据率 典型功耗 最高速(Max) 512kSPS 33mW 高速(High) 400kSPS 26mW 中速(Mid) 200kSPS 14mW 低速(Low) 50kSPS 4.3mW 滤波灵活性 :提供宽带(Wideband)和低延迟(Low-latency)两种滤波模式,支持可编程 IIR/FIR 数字滤波器(如 A 加权补偿、陷波滤波);低延迟模式下数据率最高 1.365MSPS,转换延迟仅 3μs。

输入特性 :带缓冲的差分输入,中速模式下输入电流典型值 1.5μA;输入范围可配置为 ±V_REF 或 ±2V_REF,支持内 / 外部时钟操作。

2. 功能安全与可靠性

- 具备功能安全能力,提供相关文档支持安全系统设计。

- SPI 接口支持菊花链模式,减少隔离屏障下的信号线数量;SPI 输入数据与寄存器内容通过循环冗余校验(CRC)验证,提升运行可靠性。

二、封装与引脚

1. 封装规格

- 采用 3mm×3mm 20 引脚 WQFN(RUK 封装),适用于空间受限场景,工作温度范围 - 40°C 至 + 125°C,与 ADS127L21 引脚兼容。

2. 关键引脚功能

| 引脚名称 | 类型 | 核心功能 |

|---|---|---|

| AINP/AINN | 模拟输入 | 差分模拟信号输入,支持单端 / 双极性配置 |

| REFP/REFN | 模拟输入 | 差分参考电压输入,支持高低参考范围(低:0.5-2.75V;高:1V 至 AVDD1-AVSS) |

| AVDD1/AVDD2/AVSS | 模拟电源 | AVDD1 供电输入缓冲与采样开关,AVDD2 供电调制器,AVSS 为模拟地 |

| IOVDD/DGND | 数字电源 | IOVDD 为数字 I/O 供电,DGND 为数字地 |

| SDO/DRDY | 数字输出 | 串行数据输出 / 数据就绪(可二合一减少 SPI 引脚) |

| CLK | 数字输入 | 外部时钟输入(支持内 / 外部时钟切换) |

| START/RESET | 数字输入 | 转换启动(同步滤波)、复位(低电平有效) |

三、电气规格

1. 电源与电压

- 模拟电源(AVDD1):最高速 / 高速模式 4.5-5.5V,中速模式 3-5.5V,低速模式 2.85-5.5V;AVDD2 为 1.74-5.5V。

- 数字电源(IOVDD):1.65-5.5V,内部稳压至 1.35V 供数字核心。

- 参考电压:低参考范围 0.5-2.75V,高参考范围 1V 至 AVDD1-AVSS(高参考范围强制输入范围为 1x)。

2. 输入与噪声

- 输入电流:缓冲开启时,中速模式 ±1.5μA,低速模式 ±0.4μA;缓冲关闭时随速度模式变化(如最高速模式 125μA/V)。

- 噪声性能:宽带滤波器下,最高速模式(OSR=32)噪声 11.1μV RMS,动态范围 108.3dB;Sinc4 滤波器(OSR=64)噪声 5.71μV RMS,动态范围 114.1dB。

四、工作模式与控制

1. 速度模式

通过SPEED_MODE[1:0]寄存器配置 4 种模式,对应不同时钟频率(最高速 32.768MHz,低速 3.2MHz),需匹配外部时钟或内部振荡器(仅支持 DC 信号,固定 25.6MHz)。

2. 滤波模式

- 宽带滤波器 :含预设 / 可编程 FIR(128 抽头)+4 阶 IIR,支持自定义滤波(高通、带通等),-0.1dB 带宽 0.4125×f_DATA,-3dB 带宽 0.4374×f_DATA,适合 AC 信号。

- 低延迟滤波器 :Sinc3/Sinc4 + 可选 Sinc1 级联, latency 最短 3μs,适合 DC 信号或控制环路;支持 OSR 编程(12-4096),数据率最高 1.365MSPS。

3. 同步与校准

- 同步模式 :支持同步控制(连续转换,START 同步)、启动 / 停止控制(门控转换)、单触发控制(单次转换)。

- 校准功能 :24 位偏移(OFFSET)与增益(GAIN)校准寄存器,偏移校准用补码,增益校准用无符号二进制(归一化 400000h 为 1 倍增益)。

五、接口与通信

1. SPI 接口

- 兼容 SPI 模式 1(CPOL=0,CPHA=1),支持全双工、菊花链(多 ADC 级联减少 SPI 引脚)。

- 帧格式:数据分辨率 16/24 位,可选 STATUS 头(状态信息)、CRC 字节(8 位 CRC-8-ATM,FIR 系数用 16 位 CRC-16-IBM),帧长 16-40 位(依配置)。

- 命令集:读寄存器(40h + 地址)、写寄存器(80h + 地址)、无操作(00h 00h)、复位(01011000b 写入 CONTROL 寄存器)。

2. 数据就绪与复位

- DRDY 引脚(或 SDO/DRDY 二合一)低电平指示数据就绪,读取时在 SCLK 驱动下输出数据。

- 复位方式:RESET 引脚(低电平 4 个 CLK 周期)、SPI 命令(写复位 pattern)、上电复位(POR)。

六、寄存器配置

核心寄存器功能如下,地址 00h-17h,关键寄存器包括:

| 地址 | 寄存器 | 功能 |

|---|---|---|

| 02h | STATUS1 | 状态标志(SPI 错误、CRC 错误、调制器饱和、数据就绪等) |

| 04h | CONTROL | 转换控制(启动 / 停止、复位) |

| 06h | CONFIG1 | 数据分辨率(16/24 位)、输入范围(1x/2x)、缓冲使能 |

| 08h | CONFIG3 | 时钟选择(内 / 外部)、CRC 使能(SPI / 寄存器)、STATUS 输出使能 |

| 09h | FILTER1 | 滤波器选择(宽带 / Sinc)、OSR 配置 |

| 0Ch-0Eh | OFFSET2-0 | 24 位偏移校准(补码) |

| 0Fh-11h | GAIN2-0 | 24 位增益校准(无符号二进制) |

七、应用场景与设计建议

1. 典型应用

- 测试测量 :数据采集(DAQ)、数字万用表(高精度 DC/AC 测量)。

- 工业自动化 :振动监测(高动态范围 + 低噪声)、状态控制。

- 医疗 :多普勒超声(低延迟 + 宽带滤波)。

- 电网 :电能质量分析仪(高线性度 + 50/60Hz 抑制)。

2. 设计建议

- 电源滤波 :AVDD1/AVDD2/IOVDD 需并联 1μF+0.1μF 电容(靠近引脚),CAPA(模拟稳压输出)、CAPD(数字稳压输出)各并联 1μF 电容。

- 输入驱动 :启用输入缓冲(AINP_BUF/AINN_BUF)降低外部驱动要求,长距离信号需缓冲;建议差分输入匹配布线(减少噪声耦合)。

- 抗混叠滤波 :根据 OSR 选择滤波器阶数(如 OSR=32 需 4 阶滤波器,12.8MHz 时衰减 90dB),推荐使用 THS4551(全差分放大器)设计有源滤波。

- PCB 布局 :4 层板(内部分别为地、电源平面),模拟 / 数字地单点连接(ADC 处),参考电压靠近 ADC 并独立滤波。

-

ADS127L01 24 位高速宽带 ADC 核心信息总结2025-11-10 1021

-

ADS127L21 技术文档总结2025-10-29 715

-

ADS127L14/ADS127L18 ADC 产品文档总结2025-10-23 1314

-

ADS127L21EVM-PDK评估套件技术解析与应用指南2025-08-20 1455

-

Texas Instruments ADS127L18EVM-PDK 评估模块(EVM)数据手册2025-07-24 916

-

Texas Instruments ADS127L21B宽频Δ-ΣADC数据手册2025-07-17 1059

-

Texas Instruments ADS127L18 24 位模数转换器数据手册2025-07-10 1479

-

ADS127L01采样数据不准确是哪里的问题?2024-12-13 590

-

使用STM32与ADS127L01进行通信,ADS127L01会出现不工作的情况,怎么处理?2024-11-29 707

-

ADS127L11和ADS127L01相比主要突出的特点有哪些?2024-11-25 597

-

ADS127L21EVM-PDK评估模块2024-11-06 698

-

THP210和ADS127L11性能2024-08-27 620

-

ADS127L21具有可编程滤波器的512kSPS、24位宽带Δ-ΣADC数据表2024-07-15 741

-

理解和运用ADS127L11EVM GUI中的Histogram Analysis2022-10-28 768

全部0条评论

快来发表一下你的评论吧 !