DDS39RF12 与 DDS39RFS12 产品技术文档总结

描述

DDS39RF12 和 'RFS12 是一系列双通道和单通道直接数字合成器,具有 16 位分辨率的数模转换器 (DAC)。高采样率、输出频率范围、64 位 NCO 频率分辨率和任何具有相位相干性的跳频使该器件能够进行任意波形生成 (AWG) 和直接数字合成 (DDS)。

*附件:dds39rf12.pdf

这些器件还可用作插值DAC,用于窄带直接RF采样或复杂基带信号生成。单通道的最大输入数据速率为775MSPS,双通道的最大输入数据速率为388MSPS。这些器件可以在超过 10GHz 的载波频率下生成高达 620MHz 信号带宽(16 位输入分辨率)的信号,从而能够通过 C 波段和 X 波段直接采样。

JESD204B和JESD204C兼容的串行接口有 2 个接收器对,每个接收器对的速率高达 12.8Gbps。该接口JESD204B,JESD204C符合子类 1 标准,可通过使用 SYSREF 实现确定性延迟和多设备同步。

特性

- 16位、12至24GSPS、多奈奎斯特DAC内核

- 最大输入数据速率:

- 16 位、单通道复数 I/Q:775MSPS

- 16 位、双通道复数 I/Q:388MSPS

- 输出带宽 (-3dB):12GHz

- fOUT = 2.997GHz、DES2XL模式、DEM和抖动关闭时的性能

- 本底噪声(小信号):-154dBFS/Hz

- SFDR (-0.1dBFS):68dBc

- IMD3(每音-7dBFS):-74dBc

- 加相位噪声,10kHz 偏移:-138dBc/Hz

- 四个集成数字上变频器 (DUC)

- 插值:4x、6x、8x、12x ...256 倍

- 用于 I/Q 输出的复杂基带 DUC

- 复杂到实数上转换,用于双通道直接射频采样

- 64 位频率分辨率 NCO

- 快速重新配置接口,实现快速跳频

- 4位数据,200MHz时钟

- 60ns 重新配置(32 位频率)

- 任何具有相位相干性的跳频

- JESD204C界面

- 多达 2 个通道,每个通道高达 12.8Gbps

- C-S 类,子类 1 兼容

- 内部交流耦合电容器

- 用于自动 SYSREF 时序校准的 SYSREF 窗口

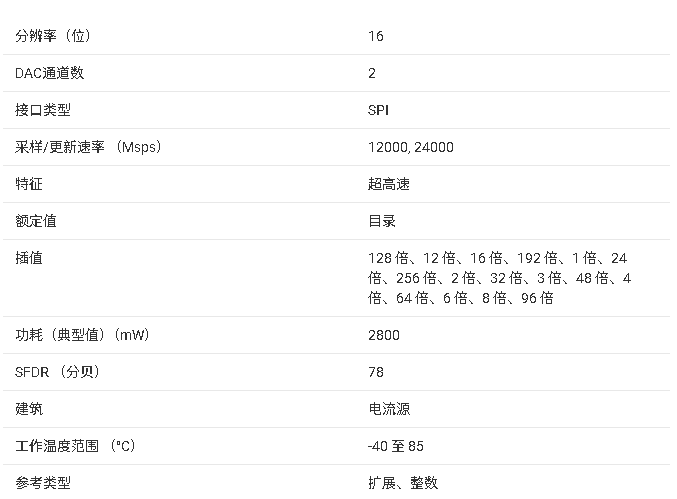

参数

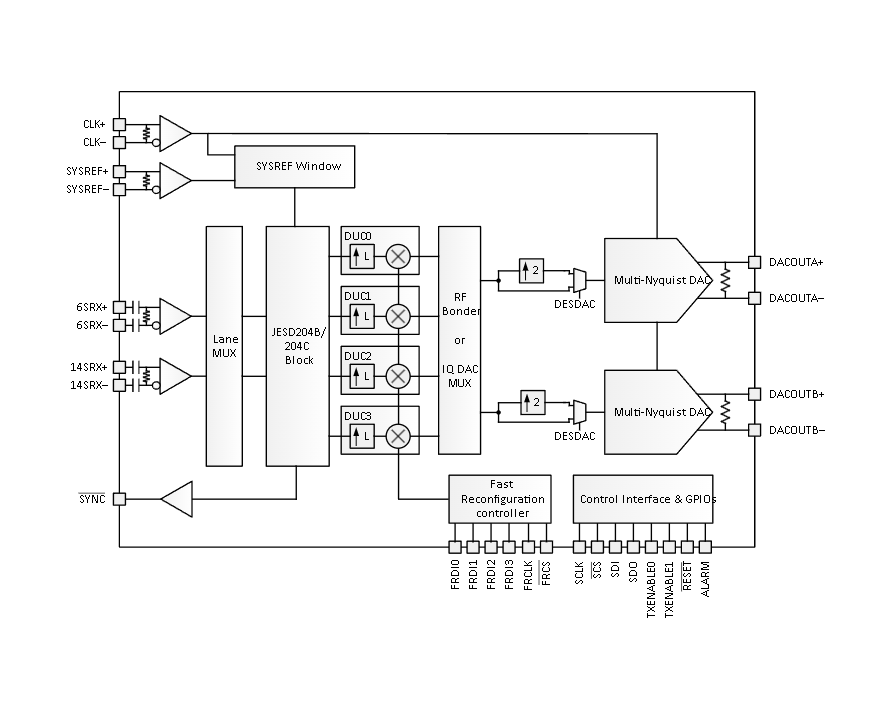

方框图

DDS39RF12 与 DDS39RFS12 是德州仪器(TI)推出的高采样率直接数字合成器(DDS)系列产品,搭载 16 位多奈奎斯特 DAC 内核,具备灵活的数字上变频器(DUC)、高速 JESD204C 接口及精准数控振荡器(NCO),可生成超宽频带信号,适用于卫星通信(SATCOM)、相控阵天线、合成孔径雷达(SAR)激励器、无线通信测试仪等对频率精度与信号带宽要求严苛的场景。两款器件核心架构一致,仅通道数量存在差异,可根据应用对信号输出通道的需求灵活选型。

一、核心特性与器件差异

1. 共性核心特性

- 高采样与带宽能力 :16 位多奈奎斯特 DAC 内核,采样率覆盖 12~24GSPS(双沿采样模式下);模拟输出带宽(-3dB)达 12GHz,支持 C 波段至 X 波段直接信号生成,可处理最高 600MHz 带宽的 16 位分辨率输入信号。

- 卓越信号性能 :在输出频率 2.997GHz、DES2XL 模式(禁用 DEM/Dither)下,小信号噪声底低至 - 154dBFS/Hz,无杂散动态范围(SFDR,-0.1dBFS)达 68dBc,三阶互调失真(IMD3,-7dBFS 双音)为 - 74dBc;10kHz 偏移处附加相位噪声低至 - 138dBc/Hz,确保信号纯净度。

- 灵活数字上变频(DUC) :集成 4 个独立 DUC,插值倍数可配置为 4x、6x、8x…256x,支持复数基带至实信号上变频,适配双通道直接射频采样;支持复数 / 实数输出格式切换,复数输出时最多启用 2 个 DUC,实数输出时最多启用 4 个 DUC,可通过通道绑定器(Channel Bonder)将多 DUC 输出求和后送入 DAC。

- 高精度 NCO 功能 :64 位 NCO 支持频率范围 - FCLK/2~+FCLK/2,相位分辨率 16 位,支持三种跳频模式:

- 相位连续模式 :频率渐变无相位突变,避免信号失真;

- 相位相干模式 :基于 SYSREF 同步,多次跳频后相位可恢复初始状态;

- 相位同步模式 :更新频率时复位累加器,适用于多器件 NCO 同步。

- 高速 JESD204C 接口 :支持 2 条 SerDes 通道,单通道速率最高 12.8Gbps,兼容 8b/10b(可选加扰)与 64b/66b(强制加扰)编码;符合 Class C-S subclass-1 标准,支持确定性延迟与多器件同步,内置 SYSREF 窗口功能,可自动校准 SYSREF 时序,补偿温度与电压导致的时序偏移。

- 快速重配置与低功耗优化 :提供快速重配置接口(FR),支持 200MHz 时钟下 4 位数据传输,32 位频率配置仅需 60ns,且跳频保持相位相干;支持睡眠模式,总功耗低至 171mW,适配低功耗场景。

2. 器件差异(DDS39RF12 vs DDS39RFS12)

| 参数 | DDS39RF12 | DDS39RFS12 |

|---|---|---|

| 通道数量 | 2 个(双通道) | 1 个(单通道) |

| 最大输入数据率(16 位复数 I/Q) | 388MSPS(双路并行) | 775MSPS(单路) |

| 典型功耗(12GSPS,DDS 模式) | 2831mW(双 DAC 工作) | 1837mW(单 DAC 工作) |

| 适用场景 | 需双路独立信号输出场景,如相控阵天线双极化控制 | 单路高带宽信号生成场景,如单通道雷达激励 |

二、封装与引脚功能

1. 封装规格

两款器件均采用 17mm×17mm 256 引脚 FCBGA 封装(1mm 引脚间距),内置裸露热焊盘(需接地优化散热),热阻参数为:结到环境(RθJA)15.8°C/W、结到板(RθJB)4.2°C/W、结到壳顶(RθJC (top))0.9°C/W;工作温度范围 - 40°C~105°C(环境温度),结温最高 115°C,MSL 等级 3(260°C 峰值回流焊,168 小时湿度敏感等级)。

2. 关键引脚分类与功能

| 引脚类别 | 关键引脚示例 | 类型 | 核心功能 |

|---|---|---|---|

| 模拟输出 | DACOUTA±、DACOUTB± | 模拟输出 | DAC 通道 A/B 差分模拟输出,需符合输出合规电压以保证性能;B 通道引脚仅 DDS39RF10 具备 |

| 时钟与同步输入 | CLK±、SYSREF± | 数字输入 | CLK± 为差分采样时钟(内置 100Ω 差分端接,自偏置,需 AC 耦合);SYSREF± 为 JESD204C 同步信号(内置 100Ω 端接) |

| SerDes 接口 | 6SRX±、14SRX± | 数字输入 | JESD204C 串行数据接收通道,内置 AC 耦合电容与 100Ω 差分端接 |

| 控制与配置接口 | SCLK、SCS、SDI/SDO | 数字 I/O | SPI 配置接口(SCS 低有效,SCLK 时钟,SDI 数据输入,SDO 数据输出);FRDI0~3、FRCLK/FRCS 为快速重配置接口 |

| 电源与地 | VDDA18A/B、VEEAM18/B18 | 电源输入 | VDDA18A/B 为 1.8V 模拟电源(通道 A/B),VEEAM18/B18 为 - 1.8V DAC 电流源偏置电源;AGND(模拟地)、DGND(数字地)、VSSCLK(时钟地)需独立布线 |

三、电气规格与工作条件

1. 电源要求

| 电源类型 | 电压范围 | 典型值 | 备注 |

|---|---|---|---|

| VDDA18A/VDDA18B | 1.71V~1.89V | 1.8V | 模拟电源(通道 A/B),可合并供电但可能增加通道串扰(XTALK) |

| VEEAM18/VEEBM18 | -1.89V~-1.71V | -1.8V | 通道 A/B DAC 电流源偏置电源,独立供电可优化串扰性能 |

| VDDCLK10 | 0.95V~1.05V | 1.0V | 时钟分配路径电源,需与数字电源隔离,避免噪声影响相位噪声性能 |

| VDDDIG | 0.95V~1.05V | 1.0V | 数字模块电源,需独立去耦,与模拟电源分开布线 |

| VDDIO/VDDR18 | 1.71V~1.89V | 1.8V | VDDIO 为 CMOS I/O 电源,VDDR18 为 SerDes 接收器电源 |

2. 关键电气参数(典型值,TA=25°C,FCLK=12GHz,IFS_SWITCH=20.5mA)

- DAC 核心性能 :16 位分辨率(无失码),差分非线性(DNL)±2.2LSB,积分非线性(INL)±9LSB;满量程输出电流(IFS_SWITCH)可通过 RBIAS 电阻与寄存器配置,典型值 20.5mA(3.6kΩ 电阻),温度漂移 - 8.6μA/°C。

- 输入输出特性 :模拟输入电容 0.5pF(时钟 / SYSREF 引脚),过压防护峰值功率 10dBm(100Ω 端接);DAC 输出差分端接电阻 102Ω,温度系数 - 9.6mΩ/°C;参考电压(VREF)典型值 0.9V,温漂 45ppm/°C。

- 功耗 :DDS39RF12 在 12GSPS、双 DAC 工作(Power Mode 1)时,总功耗典型值 2831mW;DDS39RFS12 单 DAC 工作(Power Mode 5)时,总功耗典型值 1837mW;睡眠模式功耗低至 171mW。

四、核心功能与工作模式

1. DAC 输出模式

器件支持多种 DAC 输出模式,适配不同频率范围与信号特性需求,模式差异如下表:

| DAC 输出模式 | 是否支持 DC | 最优频率范围 | 峰值输出功率 | 核心特点 |

|---|---|---|---|---|

| NRZ(非归零) | 是 | 0~FCLK/2 | 0dBFS | 标准零阶保持模式,适用于第一奈奎斯特区,频率响应在高奈奎斯特区衰减明显 |

| RTZ(归零) | 是 | 0~FCLK | -6dBFS | 采样周期后半段归零,频率响应展宽,支持第一、二奈奎斯特区,峰值功率降低 6dB |

| RF 模式 | 否 | FCLK/2~FCLK | -2.8dBFS | 采样中期反转信号,第二奈奎斯特区响应平坦,适用于射频频段直接输出 |

| DES2XL(双沿采样低通) | 是 | 0~0.4FCLK | 0dBFS | 上升 / 下降沿均输出采样值,采样率翻倍,内置低通 2x 插值滤波器,抑制低频镜像 |

| DES2XH(双沿采样高通) | 是 | 0.6~1.0FCLK | 0dBFS | 内置高通 2x 插值滤波器,抑制高频镜像,适用于高奈奎斯特区信号输出 |

2. 数字上变频(DUC)与 NCO

- DUC 配置 :4 个 DUC 可独立或统一配置插值倍数(2x

256x),插值滤波器采用多级设计(如 fir1fir5、fir_3x), passband 带宽 80%, stopband 衰减>90dB;支持通道绑定功能,可将多个 DUC 输出按 1(0dB)、0.5(-6dB)、0.25(-12dB)增益缩放后求和,避免信号饱和。 - NCO 同步与重配置 :NCO 可通过 JESD204C 接口 LSB、SYSREF 信号或 SPI_SYNC 寄存器触发同步,确保多通道 / 多器件相位一致性;快速重配置接口(FR)支持 60ns 内更新 32 位频率字,且跳频保持相位相干,适配动态频率调整场景。

3. JESD204C 接口与同步

- 接口特性 :支持 2 条 SerDes 通道,速率最高 12.8Gbps,8b/10b 编码可选加扰,64b/66b 编码强制加扰;支持 subclass 0(非确定性延迟)与 subclass 1(确定性延迟),subclass 1 需通过 SYSREF 校准 LMFC/LEMC 计数器,确保多器件同步精度。

- 时序校准 :内置 SYSREF 窗口功能,可检测 SYSREF 相对于 CLK 的位置(SYSREF_POS 寄存器),自动选择最优采样时刻(SYSREF_SEL 配置),补偿温度(-0.05ps/°C)与电压(0.19ps/mV)导致的时序偏移,优化同步 margin;支持 LANE_ARR 寄存器测量 lane arrival 时间,辅助设置弹性缓冲区释放延迟(RBD),确保 deterministic latency。

4. 特殊工作模式

- DDS 模式 :通过 DDS_EN 寄存器使能,禁用 JESD204C 接口与 DUC 插值滤波器,直接通过 NCO 生成 tones,支持 4 个独立 DDS 通道;AMP 寄存器可配置各通道幅度,用于抵消 DAC 输出谐波(如 HD2、HD3),提升信号动态范围;此模式下 SYSREF 周期约束简化,无需适配 JESD204C 时序要求。

- 睡眠与掉电模式 :支持睡眠模式(MODE [1:0]=0b11)与全掉电模式(MODE [1:0]=0b11),睡眠模式下寄存器配置保留,总功耗 171mW;全掉电模式需遵循特定电源时序,避免器件损伤,唤醒后需等待内部参考稳定(约 100μs)。

五、寄存器配置

1. 寄存器 bank 核心功能

- 全局控制 bank(0x0000~0x00FF) :包含芯片复位(SOFT_RESET)、设备配置(DEVICE_CONFIG)、SYSREF 控制(SYSREF_CTRL)、温度传感器控制(TS_SLEEP)等,用于器件基础初始化与全局参数配置。

- JESD204C 配置 bank(0x0100~0x02FF) :配置 JESD 模式(JMODE)、通道数(JESD_M)、PLL 参数(REFDIV、MPY、RATE)、SerDes 均衡器(EQ_CTRL、LANE_EQ)、弹性缓冲区释放延迟(RBD),确保高速接口稳定工作。

- DAC 与 DUC 配置 bank(0x02E0~0x03FF) :配置 DAC 输出模式(MXMODE)、DUC 插值倍数(DUC_L)、NCO 频率与相位(FREQ [n]、PHASE [n])、DEM/Dither 功能(DEM_DITH),控制信号生成链路参数。

- 状态与告警 bank(0x0400~0x04FF) :包含温度传感器读数(TS_TEMP)、系统告警(SYS_ALM)、同步状态(SYNC_STATUS)、DAC 静音控制(MUTE_MASK/MUTE_REC),用于监测器件工作状态与故障排查。

2. 关键寄存器示例

| 寄存器地址 | 功能 | 关键配置示例 |

|---|---|---|

| 0x02E8(MXMODE) | DAC 输出模式选择 | MXMODE0=3(DACA 为 DES2XL 模式),MXMODE1=4(DACB 为 DES2XH 模式,仅 DDS39RF12) |

| 0x02E1(DUC_L) | DUC 插值倍数配置 | DUC_L=5(8x 插值),支持 4 个 DUC 同时工作 |

| 0x0320~0x0327(FREQ[0]) | NCO 频率配置 | FREQ [0]=0x3D09000000000000(对应 120MHz,FCLK=12GHz) |

| 0x0300(NCO_CTRL) | NCO 与 DDS 模式控制 | DDS_EN=1(使能 DDS 模式),FR_EN=1(使能快速重配置接口) |

六、应用与设计建议

1. 典型应用场景

- 卫星通信(SATCOM) :利用 12GHz 宽输出带宽与低相位噪声,生成 C/X 波段上行 / 下行信号,支持多载波同时输出;DUC 插值功能可降低基带数据率,适配 FPGA 数据处理能力。

- 合成孔径雷达(SAR)激励器 :通过 DDS 模式生成高线性度 Chirp 信号,NCO 相位相干跳频确保雷达距离分辨率;DES2XL/H 模式抑制镜像信号,减少后端滤波复杂度。

- 相控阵天线系统 :DDS39RF12 双 DAC 支持双极化信号输出,多器件通过 SYSREF 同步,确保多通道相位一致性,提升天线波束成形精度。

2. 设计建议

- 电源设计 :模拟电源(VDDA18A/B、VEEAM18/B18)与数字电源(VDDDIG、VDDCLK10)需独立供电,推荐 “开关电源 + 低噪声 LDO” 架构(如 LMS3635+TPS7A8400),每路电源引脚就近并联 0.1μF 陶瓷电容 + 10μF 钽电容去耦;模拟地、数字地、时钟地在热焊盘处单点连接,避免地弹噪声。

- PCB 布局 :

- 模拟输入(AINxP/AINxM、CLK±、SYSREF±)采用差分布线,长度匹配误差<5mil,远离数字信号线;

- SerDes 接口(6SRX±、14SRX±)布线阻抗控制为 100Ω,长度匹配误差<10mil;

- 热焊盘通过≥8 个 0.3mm 过孔连接至地平面,优化散热。

- 时钟与同步 :采样时钟(CLK±)推荐使用低噪声时钟源(如 LMK04828),AC 耦合至引脚;多器件同步时,SYSREF 与 CLK 需等长布线(误差<10ps),通过 SYSREF_POS 寄存器校准时序,确保同步精度。

- 信号完整性 :DAC 输出端建议串联 1kΩ 限流电阻(防止过流),驱动长距离信号时添加差分缓冲器(如 THS4551);JESD204C 链路使用阻抗匹配连接器(如 Samtec QSE 系列),减少信号反射。

-

DAC39RFx10 系列产品技术文档总结2025-10-27 1011

-

DDS39RF10产品技术文档总结2025-10-24 1323

-

DAC39RF12、DAC39RFS12双通道和单通道数模转换器(DAC)数据表2024-07-15 729

-

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位双通道和单通道多奈奎斯特数模转换器(DAC)数据表2024-07-12 718

-

利用ADISim DDS在线工具仿真DDS产品的频谱特性2019-07-15 5396

-

PIC12LF1840T39A产品手册免费下载2018-06-27 1728

-

STM32的AD9854 DDS模块调试总结2018-05-16 20299

-

DDS是什么意思,DDS结构,DDS原理是什么2010-03-08 48001

-

DDS,什么是DDS,DDS的结构2009-09-03 5139

全部0条评论

快来发表一下你的评论吧 !