AFE8190 16 通道射频收发器技术文档总结

描述

AFE8190是一款高性能、宽带宽的多通道收发器,集成了16个射频采样发射器链、16个射频采样接收器链和4个独立的射频采样辅助链(反馈路径)。发射器和接收器链的高动态范围允许为无线基站生成和接收 3G、4G 和 5G 信号,而宽带宽能力使该AFE8190成为多频段 4G 和 5G 基站的绝佳选择。

*附件:afe8190.pdf

每个接收器链包括一个 30dB 范围的 DSA(数字步进衰减器),然后是一个 5GSPS ADC(模数转换器)。每个接收器通道都有模拟峰值功率检测器和数字峰值和功率检测器,以辅助外部或内部自主自动增益控制器,以及用于器件可靠性保护的射频过载检测器。单数字下变频器 (DDC) 提供高达 600MHz 的信号带宽。

每个发射器链都包括一个数字上变频器(DUC),支持高达800MHz的信号带宽。DUC 的输出驱动 12GSPS DAC(数模转换器),具有混合模式输出选项,以增强二次奈奎斯特作。DAC输出包括一个可变增益放大器(TX DSA),范围为39dB,模拟步长为1dB,数字步长为0.125dB。

特性

- 16 个 RF 采样 12GSPS 发射 DAC

- 16 个 RF 采样 5GSPS 接收 ADC

- 四通道射频采样 5GSPS 反馈 ADC

- 最大射频信号带宽:

- 发射/频波:800MHz。

- 接收:600MHz

- 射频频率范围:高达 7.2GHz

- 数字步进衰减器 (DSA):

- TX:39dB范围,1dB模拟步进和0.125dB数字步进

- RX:30dB 范围,1dB 步进

- FB:25dB范围,1dB步进

- 每条链单 DUC/DDC

- 支持 TDD作,可在 TX 和 RX 之间快速切换

- 内部PLL/VCO,用于生成DAC/ADC时钟

- 可选的DAC或ADC速率的外部CLK

- 数字数据接口:

- JESD204B和JESD204C

- 16 个高达 32.5Gbps 的 SerDes 收发器

- 8b/10b 和 64b/66b 编码

- 12 位、16 位、24 位和 32 位分辨率

- 子类 1 多设备同步

- 包:

- 23mm × 23mm FCBGA,0.8mm 间距

参数

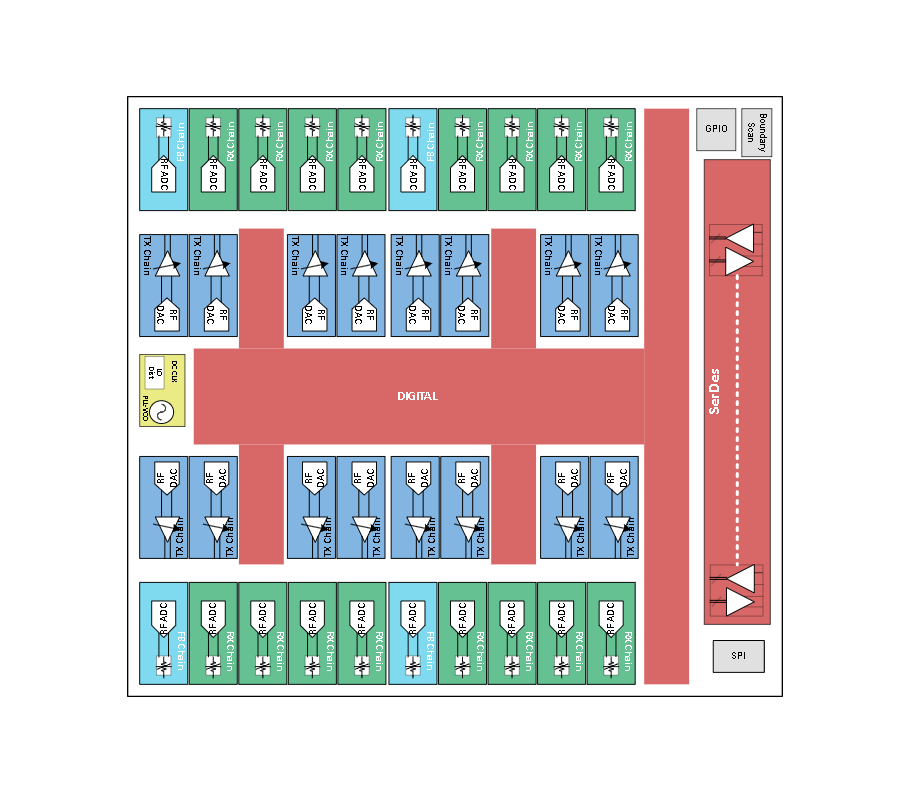

方框图

AFE8190 是德州仪器(TI)推出的高性能多通道射频(RF)收发器,集成 16 路发射链路、16 路接收链路及 4 路反馈链路,具备高采样率、宽频带与灵活数字接口特性,专为 5G 基站、有源天线系统(AAS)等无线通信场景设计,可满足多频段、大带宽信号的生成与接收需求。

一、核心特性

1. 多链路高采样率架构

- 发射链路(TX) :16 路 RF 采样 DAC,每路采样率高达 12GSPS,支持混合模式输出以优化第二奈奎斯特区性能;集成数字上变频器(DUC),单链路信号带宽最高 800MHz,适配大带宽 5G 信号生成。

- 接收链路(RX) :16 路 RF 采样 ADC,每路采样率 5GSPS,单链路信号带宽最高 600MHz;配备模拟峰值功率检测器、数字峰值 / 功率检测器,辅助自动增益控制(AGC),并含 RF 过载检测器以保护器件可靠性。

- 反馈链路(FB) :4 路独立 RF 采样 ADC,每路采样率 5GSPS,用于信号闭环校准与监测,提升系统传输精度。

2. 宽频带与灵活衰减控制

- 频率与带宽覆盖 :RF 工作频率范围最高 7.2GHz,支持 C/X 等主流通信频段;TX/FB 链路带宽 800MHz、RX 链路带宽 600MHz,可同时处理多频段 4G/5G 信号。

- 数字步进衰减器(DSA) :

- TX 链路:39dB 衰减范围,支持 1dB 模拟步进与 0.125dB 数字步进,精细调节输出功率;

- RX 链路:30dB 衰减范围,1dB 步进,适配不同强度输入信号;

- FB 链路:25dB 衰减范围,1dB 步进,优化反馈信号动态范围。

3. 时钟与同步能力

- 内置时钟生成 :集成 PLL/VCO 模块,可直接生成 DAC/ADC 工作时钟,简化外部时钟设计;

- 外部时钟选项 :支持外部输入 DAC 或 ADC 速率时钟,适配系统级时钟同步需求;

- 多器件同步 :支持 JESD204C subclass 1 标准,通过 SYSREF 信号实现多器件相位一致性,满足大规模 MIMO(mMIMO)等多通道同步场景。

4. 高速数字接口

- JESD204B/C 兼容 :配备 16 路 SerDes 收发器,单通道速率最高 32.5Gbps,支持 8b/10b(可选加扰)与 64b/66b(强制加扰)编码,适配不同传输效率需求;

- 多分辨率支持 :兼容 12 位、16 位、24 位、32 位数据分辨率,灵活匹配基带处理器(如 FPGA)数据格式。

5. 低功耗与 TDD 适配

- 分时双工(TDD)优化 :支持 TX 与 RX 模式快速切换,切换延迟低,适配 5G TDD 基站时隙调度需求;

- 封装与散热 :采用 23mm×23mm 784 引脚 FCBGA 封装(0.8mm 引脚间距),最大高度 2.751mm,裸露热焊盘设计优化散热,工作结温范围 - 40°C~85°C。

二、典型应用场景

AFE8190 凭借多通道、大带宽特性,广泛适用于无线通信基础设施,核心应用包括:

- 宏基站远端射频单元(RRU) :16 路 TX/RX 链路支持多天线阵列,满足宏基站多用户并发通信需求;

- 有源天线系统(AAS)/mMIMO :多链路同步能力与宽频带特性,适配大规模天线波束成形,提升信号覆盖与容量;

- 小基站与分布式天线系统(DAS) :紧凑封装与高集成度,减少小基站体积,降低部署成本;

- 中继器(Repeater) :反馈链路支持信号实时校准,提升中继器信号放大精度与稳定性。

三、封装与机械规格

1. 封装参数

| 型号 | 封装类型 | 封装名称 | 引脚数 | 尺寸(长 × 宽) | 引脚间距 | 最大高度 |

|---|---|---|---|---|---|---|

| AFE8190IAMJ | FCBGA | AMJ | 784 | 23mm×23mm | 0.8mm | 2.751mm |

2. 托盘与组装信息

- 托盘规格 :采用 JEDEC 标准托盘(5+1 排列),每盘 60 个器件;托盘外尺寸 135.9mm(长)×12.19mm(宽)×25.5mm(高),角部口袋中心距边缘 CL=17.25mm、CW=16.95mm,倒角标识 Pin 1 方向。

- PCB 布局建议 :焊盘设计采用非阻焊定义(NSMD)优选方案,焊盘直径 0.4mm,阻焊开窗 0.4mm,建议使用 0.15mm 厚钢网进行焊接,激光切割梯形孔与圆角设计可提升焊膏释放效果;需遵循 TI 文献 SPRU811 的布局公差与布线约束。

四、订购与环境信息

1. 订购型号参数

| 订购型号 | 状态 | 封装 | 温度范围 | RoHS 合规 | Moisture Sensitivity Level(MSL) | 峰值回流温度 |

|---|---|---|---|---|---|---|

| AFE8190IAMJ | 量产(Active) | 784 引脚 FCBGA | -40°C~85°C | 是 | 3 级(168 小时湿度敏感,260°C 峰值) | 260°C |

| AFE8190IAMJ.B | 量产(Active) | 784 引脚 FCBGA | -40°C~85°C | 咨询 TI | 咨询 TI | 咨询 TI |

2. 静电防护与可靠性

- ESD 防护 :器件对静电敏感,需遵循 JEDEC JESD22-A114 标准进行操作,避免因静电导致性能退化或永久损坏;

- 质量保证 :量产型号通过 TI 严格可靠性测试,符合工业级环境要求,适合长期稳定运行于基站等基础设施场景。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AFE8190:高性能16通道RF收发器的卓越之选2026-01-26 891

-

高性能多通道射频收发器AFE8192:5G时代通信基站的有力支撑2026-01-25 799

-

AFE7950多通道收发器技术手册2025-10-31 856

-

AFE7903 技术文档总结2025-10-30 712

-

AFE8004射频采样收发器技术文档总结2025-10-29 693

-

AFE8192技术文档完整总结2025-10-21 704

全部0条评论

快来发表一下你的评论吧 !