FPGA怎么搭复位电路 fpga复位电路设计方案

FPGA外设/外围电路

描述

FPGA和复位电路相比大家应该都比较熟悉,那么对于FPGA怎么搭复位电路你知道吗?本文介绍的就是关于FPGA怎么搭复位电路以及fpga复位电路设计方案。

复位电路

为确保微机系统中电路稳定可靠工作,复位电路是必不可少的一部分,复位电路的第一功能是上电复位。一般微机电路正常工作需要供电电源为5V±5%,即4.75~5.25V。由于微机电路是时序数字电路,它需要稳定的时钟信号,因此在电源上电时,只有当VCC超过4.75V低于5.25V以及晶体振荡器稳定工作时,复位信号才会撤除,微机电路开始正常工作。

复位电路,就是利用它把电路恢复到起始状态。就像计算器的清零按钮的作用一样,以便回到原始状态,重新进行计算。和计算器清零按钮有所不同的是,复位电路启动的手段有所不同。一是在给电路通电时马上进行复位操作;二是在必要时可以由手动操作;三是根据程序或者电路运行的需要自动地进行。复位电路都是比较简单的大都是只有电阻和电容组合就可以办到了。再复杂点就有三极管等等配合程序来进行了。

FPGA

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路数有限的缺点。

系统设计师可以根据需要通过可编辑的连接把FPGA内部的逻辑块连接起来,就好像一个电路试验板被放在了一个芯片里。一个出厂后的成品FPGA的逻辑块和连接可以按照设计者而改变,所以FPGA可以完成所需要的逻辑功能。

FPGA一般来说比ASIC(专用集成电路)的速度要慢,实现同样的功能比ASIC电路面积要大。但是他们也有很多的优点比如可以快速成品,可以被修改来改正程序中的错误和更便宜的造价。厂商也可能会提供便宜的但是编辑能力差的FPGA。因为这些芯片有比较差的可编辑能力,所以这些设计的开发是在普通的FPGA上完成的,然后将设计转移到一个类似于ASIC的芯片上。另外一种方法是用CPLD(Complex Programmable Logic Device,复杂可编程逻辑器件)。

FPGA怎么搭复位电路

异步复位:复位信号和系统时钟信号的触发可以在任何时刻。二者相互独立。

同步复位:在系统时钟信号的触发下,复位信号有效。

用verilog表示会更明显:

// 异步复位

reg a;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

a <= 'd0;

else

a <= ~a;

end

//同步复位

reg b;

always @ (posedge clk) begin

if(!rst_n)

b <= 'd0;

else

b <= ~b;

end

如果复位信号的撤销发生在系统时钟的建立和保持时间这段时间内,系统此时检测到复位信号的状态就处在一个亚稳态,无法确定是0还是1。就有可能造成系统工作不同步的问题。

异步复位会影响寄存器的recovery时间,引起设计的稳定性问题,尤其对于状态机的无意识复位,将导致进入不确定的状态。

同步复位最主要的问题是对于不带同步复位专用端口的器件会增加额外的逻辑资源。

//异步复位、同步释放

reg rst_nr1;

reg rst_nr2;

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

rst_nr1 <= 'd0;

else

rst_nr1 <= 1'b1;

end

always @ (posedge clk or negedge rst_n) begin

if(!rst_n)

rst_nr2 <= 'd0;

else

rst_nr2 <= rst_nr1;

end

简单分析一下这个电路,当异步复位发生,rst_nr2直接拉低为0,并且由于rst_nr2是在时钟沿的作用下对rst_nr1进行采样,所以当rst_nr2的置1是和时钟沿同步的。也就是异步复位、同步释放。然后用信号rst_nr2作为系统复位时钟,就不发生亚稳态现象。

但是在我的理解看来,这两个触发器仍然是采用rst_n作为复位信号,所以必然会有亚稳态的现象发生,即rst_nr2还是 有可能在不应该复位的时间点复位,但是由rst_nr2作为系统复位信号的后级电路不会发生系统工作不同步的现象。

fpga复位电路设计方案

对FPGA设计中常用的复位设计方法进行了分类、分析和比较。针对FPGA在复位过程中存在不可靠复位的现象,提出了提高复位设计可靠性的4种方法,包括清除复位信号上的毛刺、异步复位同步释放、采用专用全局异步复位/置位资源和采用内部复位。上述方法可有效提高FPGA复位的可靠性。

对FPGA芯片而言,在给芯片加电工作前,芯片内部各个节点电位的变化情况均不确定、不可控,而这种不确定且不可控的情况会使芯片在上电后的工作状态出现错误。因此,在FPGA的设计中,为保证系统能可靠进进入工作状态,以及避免对FPGA输出关联的系统产生不良影响,FPGA上电后要进行复位,且为了消除电源开关过程中引起的抖动影响,复位信号需在电源稳定后经过一定的延时才能撤销,FPGA的复位信号需保证正确、稳定、可靠。

在FPGA的设计中,多数情况下复位电路的功能虽能够正常完成,但电路并未得到精确合理的设计,仍存在可靠性设计缺陷。为确保系统复位的可靠性,有必要对FPGA复位的可靠性设计方法进行研究。

1 复位设计方法分类

复位的目的是在仿真时将设计强制定位在一个可知状态,合理选择复位方式是电路设计的关键。根据与系统时钟域的关系,复位电路可分为同步复位和异步复位。同步复位是指复位信号只在时钟沿到来时,才有效。否则,无法完成对系统的复位工作。异步复位是指无论时钟沿是否到来,只要复位信号有效,使对系统进行复位。

根据是否存在外部复位端口,复位电路又可分为外部复位和内部复位。外部复位是指复位信号主要来自外部引脚的输入,如复位按钮、电源模块输出等。内部复位信号则是主要由FPGA内部电路产生。

2 复位设计方法的比较

2.1 同步复位与异步复位

2.2.1 同步复位

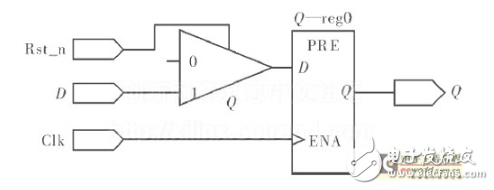

指定同步复位时,always的敏感表中仅有一个时钟沿信号,只有当时钟沿采集到同步复位的有效电平时,才会在时钟沿到达时刻进行复位操作。若目标器件或可用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可直接调用同步复位端。然而多数目标器件的触发器本身并不包含同步复位端口,需使复位信号与输入信号组成某种组合逻辑,然后将其输入到寄存器的输入端。为了提高复位电路的优先级,通常在电路描述时使用带有优先级的if…else结构,复位电路在第一个if下描述,其他电路在else或else…if分支中描述。复位电路综合后的RTL图如图1所示。

同步复位电路图

根据同步电路的特点,其电路优点有:(1)同步复位有利于基于周期机制的仿真器进行仿真。(2)使用同步复位可设计100%的同步时序电路,有利于时序分析,其综合结果的频率较高。(3)同步复位仅在时钟的有效沿生效,可有效避免因毛刺造成的亚稳态和错误。毛刺信号是由FPGA内部结构特征决定的,同步复位在进行复位和释放复位信号时,仅当时钟沿采到复位信号电平变化时进行相关操作,若复位信号树的组合逻辑出现了某种毛刺,此时时钟沿采到毛刺的概率较低,由此通过时钟沿采样,可有效过波复位电路组合逻辑产生的毛刺,增强了电路稳定性。

同步复位的缺点有:(1)多数目标器件库的触发器本身并不包含同步复位端口,使用同步复位会增加更多逻辑资源。(2)同步复位的最大问题在于必须保证复位信号的有效时间,需要一个脉宽延展器以确保复位信号有一定脉冲宽度,由此才能保证所有触发器均能有效复位。由于同步复位仅当时钟沿采到复位信号时才会进行复位操作,所以其信号的持续时间要大于设计的最长时钟周期,以保证所有时钟的有效沿都能采样到同步复位信号。事实上,仅保证同步复位信号的持续时间大于最慢的时钟周期是不够的,设计中还需考虑到同步复位信号树通过所有相关组合逻辑路径时的延时,以及由于时钟布线产生的偏斜。只有同步复位大于时钟最大周期,加上同步信号穿过的组合逻辑路径延时和时钟偏斜延时,才能确保同步复位的可靠。

2.2.2 异步复位

指定异步复位时,只需在always的敏感表中加人复位信号的有效沿即可,当复位信号有效沿到达时,无论时钟沿是否有效,复位均会立即发挥其功能。

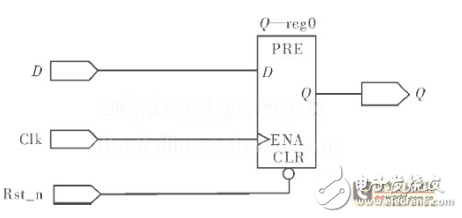

大多数目标器件和ASIC库的触发器均包含异步复位端口,异步复位会直接接人触发器的异步复位端口,综合后的RTL图如图2所示。

异步复位电路图

根据异步电路的特点,异步复位的优点有:(1)由于多数目标器件库的触发器都包含异步复位端口,异步复位会节约逻辑资源。(2)异步复位设计简单。(3)对于多数FPGA,均有专用的全局异步复位/置位资源(GSR,Global Set Reset),还可使用GSR资源,异步复位到达所有寄存器的偏斜最小。 异步复位的缺点如下:(1)异步复位的作用和释放与时钟沿并无直接关系,异步复位生效时问题并不明显;但当释放异步复位时,若异步复位信号释放时间和时钟的有效沿到达时间几乎一致,则容易造成触发器输出为亚稳态,形成逻辑错误。(2)若异步复位逻辑树的组合逻辑产生了毛刺,则毛刺的有效沿会使触发器误复位,造成逻辑错误。

2.3 外部复位和内部复位

外部复位,复位信号主要来自外部引脚的输人。复位信号在电路板上可能会受到来自其他线路的串扰,因此可能产生毛刺,在无需复位系统时,毛刺信号可能导致系统误复位。

内部复位,FPGA上电配置完成后,由FPGA内部电路产生复位信号,复位信号与时钟同步。通常内部复位的设计方法是:设计一个初始值为0X0000的SRL16,将其输人接高电平,输出作为复位信号。

3 复位可靠性设计方法

3.1 消除复位信号上的毛刺

在系统设计中,若采用低有效复位信号,可按照图3所示方法对复位信号中的毛刺进行消除。延时器件对数据进行延时的长度决定复位毛刺消除电路所能避免的毛刺长度,而延时器件的延时长度也决定需要提供有效复位信号的最短时间。

如果复位信号高有效,则将图3中的或门改为与门使用。为更好地消除毛刺,可在复位毛刺消除电路后再加上寄存器对复位信号进行时钟同步。在通常复位电路的设计中,毛刺的长度一般情况下>1个时钟周期,<16个时钟周期。为节省资源,延时器件通常选用SRL16。SRL16可设置初始值,但不带复位功能16bit移位寄存器,能够通过A0~A3的4根地在线选择从第几个寄存器输出。通常将其作为一个普通的16bit移位寄存器使用。

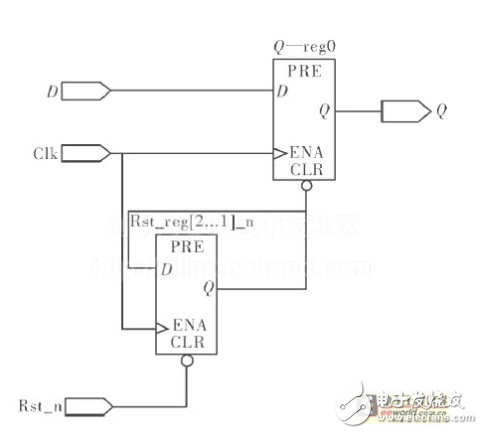

3.2 异步复位同步释放

在有些应用中,复位信号需要在时钟尚未给出或不稳定的情况下传到后级,在时钟稳定之后,再撤去复位信号。此时需使用异步复位来实现。由于异步复位时,时钟和复位关系的不确定性,易造成触发器输出亚稳态,引起逻辑错误。为确保其复位的可靠性,通常采用异步复位,同步释放的方式。

所谓异步复位,同步释放就是在复位信号到达时不受时钟信号的同步,而是在该信号释放时受时钟信号的同步。通过一个复位信号综合器便可实现异步复位,同步释放。综合后的RTL图如图3所示,其仿真结果表明该电路能有效的实现复位及脱离复位。

异步复位、同步释放电路图

3.3 采用专用全局异步复位/置位资源

全局异步复位/置位资源的主要作用是对系统中存在的所有触发器、锁存器、查找表单元的输出寄存器进行复位,不会占有额外的布线资源。使用GSR资源,异步复位到达所有寄存器的偏斜最小。

3.4 采用内部复位的设计方法

在无需复位信号先于时钟信号产生的应用中,为避免外部复位毛刺的影响、异步复位电路可能引起的亚稳态以及减少资源的使用率,可通过FPGA产生内部复位,然后采用异步的方式对其的内寄存器进行复位。由于该复位信号由FPGA内部产生,不会因外部干扰而产生毛刺,同时又与时钟同步,不存在因异步复位导致的亚稳态现象,因此可确保系统可靠复位。

结语

FPGA的可靠复位是保证系统能够正常工作的必要条件,本文对FPGA设计中常用的复位设计方法进行了分类、分析和比较,并针对各种复位方式的特点,提出了如何提高复位设计可靠性的方法。在工程实践中,上述方法可以有效减少或消除FPGA复位所产生的错误。

关于FPGA复位电路的介绍就到这里了,希望通过本文能让你对FPGA复位电路的整体架构有更深的理解,如有不足之处欢迎指正。

-

FPGA和CPLD内部自复位电路设计方案2016-07-11 7260

-

fpga设计实战:复位电路仿真设计2020-09-01 2070

-

FPGA中三种常用复位电路2023-05-14 3379

-

FPGA复位电路的设计2019-04-12 2897

-

FPGA的理想的复位方法和技巧2017-11-22 6327

-

基于FPGA的调焦电路设计方案资料下载2018-05-07 1320

-

外加电压检测复位电路设计方案2018-07-01 8150

-

FPGA设计实战-复位电路仿真设计2020-10-30 916

-

实现FPGA实战复位电路的设计和仿真2020-12-22 873

-

stm32复位电路设计2022-06-26 1159

-

FPGA复位电路的实现——以cycloneIII系列芯片为例2023-03-13 4772

-

FPGA内部自复位电路设计方案2023-04-06 2135

-

FPGA复位电路的实现方式2023-05-25 4465

-

FPGA同步复位和异步复位2024-07-17 3241

-

FPGA复位的8种技巧2024-11-16 1759

全部0条评论

快来发表一下你的评论吧 !