DAC39RFx10-SP/SEP 系列数模转换器技术文档总结

描述

DAC39RF10-Sx 和 'RFS10-Sx 是一系列具有 16 位分辨率的双通道和单通道数模转换器 (DAC)。这些器件可用作非插值或插值DAC,用于直接RF采样或复杂基带信号生成。单通道的最大输入数据速率为 20.8GSPS,双通道的最大输入数据速率为 10.4 GSPS。这些器件可以在超过 10GHz 的载波频率下生成高达 10、7.5 和 5GHz 信号带宽(8、12 和 16 位输入分辨率)的信号,从而实现 X 波段的直接采样。

高采样率、输出频率范围、64 位 NCO 频率分辨率和任何具有相位相干性的跳频也使 DAC39RF10-Sx 和 'RFS10-Sx 能够进行任意波形生成 (AWG) 和直接数字合成 (DDS)。

*附件:dac39rf10-sp.pdf

JESD204B和JESD204C兼容的串行接口具有 16 个接收器对,速度高达 12.8Gbps。该接口JESD204B,JESD204C符合子类 1 标准,可通过使用 SYSREF 实现确定性延迟和多设备同步。

特性

- 辐射硬度保证 DAC39RFx10-SP:

- 单事件扰乱 (SEU) 免疫寄存器

- 单事件闩锁 (SEL):120MeV-cm2/mg

- RLAT 总电离剂量 (TID):300krad (Si)

- 耐辐射 DAC39RFx10-SEP:

- 单事件扰乱 (SEU) 免疫寄存器

- 单事件闩锁 (SEL):43MeV-cm2/mg

- RLAT 总电离剂量 (TID):30krad (Si)

- 16位、10.4或20.8GSPS、多奈奎斯特DAC内核

- 最大输入数据速率:

- 8 位,单通道,DES 模式:20.8GSPS

- 12 位,单通道,DES 模式:15.5GSPS

- 16 位,单通道:10.4GSPS

- 8 位,双通道,10.4GSPS

- 12 位,双通道:7.75GSPS/通道

- 16 位,双通道:6.2GSPS/通道

- 输出带宽 (-3dB):12GHz

- fOUT = 2.997GHz、DES2XL模式、DEM/抖动关闭时的性能

- 本底噪声(小信号):–155dBFS/Hz

- SFDR (-0.1dBFS):60dBc

- IMD3(每音-7dBFS):–62dBc

- 加相位噪声,10kHz 偏移:-138dBc/Hz

- 四个集成数字上变频器 (DUC)

- 插值:1x、2x、3x、4x、6x、8x、12x ...256 倍

- 用于 I/Q 输出的复杂基带 DUC

- 复杂到实数上转换,用于双通道直接射频采样

- 64 位频率分辨率 NCO

- JESD204C界面

- 多达 16 个通道,最高可达 12.8Gbps

- C-S 类,子类 1 兼容

- 内部交流耦合电容器

- 用于自动 SYSREF 时序校准的 SYSREF 窗口

- 空间筛选和保证:

- 符合 ASTM E595 释气规范

- 一个制造、组装和测试站点

- 晶圆批次可追溯性

- 延长产品生命周期

- 辐射批次验收测试 (RLAT)

- 生产老化(仅限 DAC39RFx10-SP)

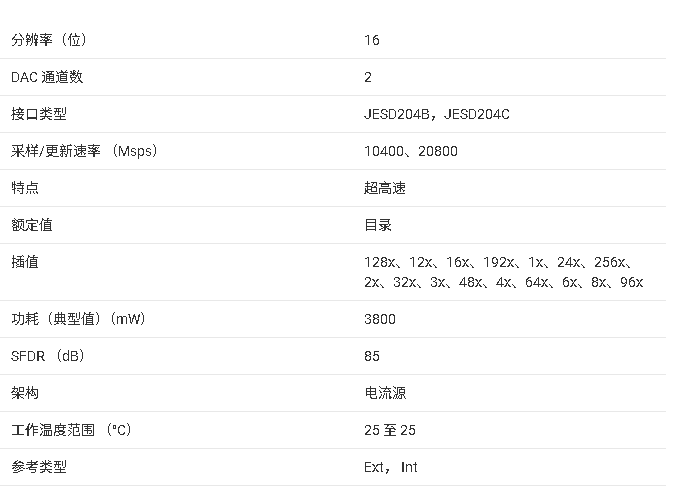

参数

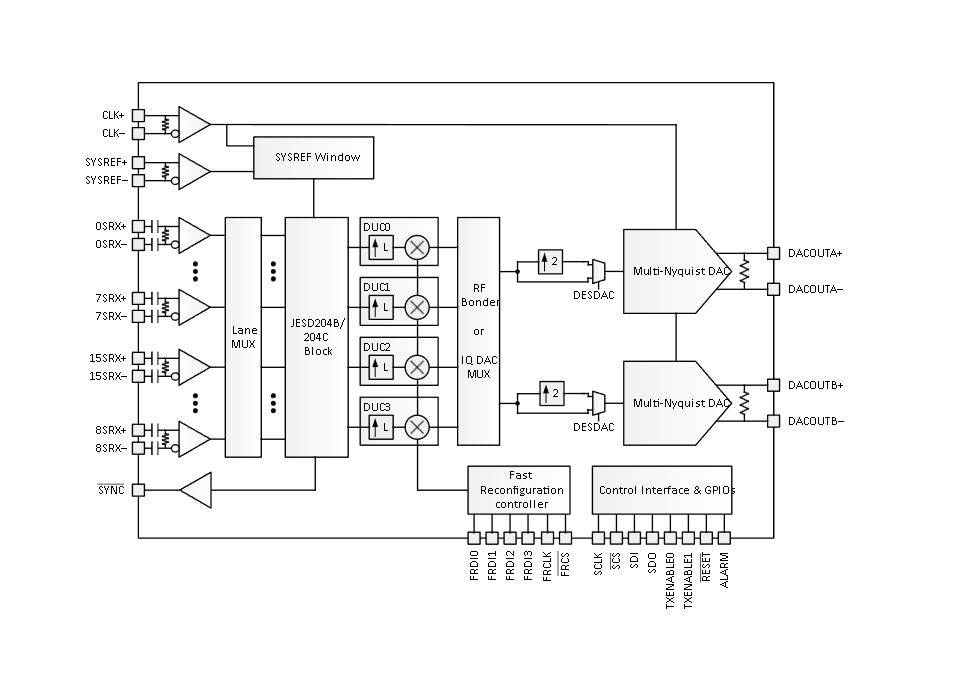

方框图

DAC39RFx10-SP/SEP 系列是德州仪器(TI)推出的 高采样率、高分辨率数模转换器(DAC)家族 ,包含双通道(DAC39RF10)与单通道(DAC39RFS10)型号,分为抗辐射增强型(-SP)与耐辐射型(-SEP)两个等级,以10.4/20.8GSPS 高采样率、16 位分辨率、JESD204C 高速接口为核心优势,集成数字上变频器(DUC)、多 Nyquist DAC 内核等功能,适配卫星通信、相控阵天线、合成孔径雷达(SAR)等高端射频(RF)与空间应用场景,工作温度覆盖 - 55°C~+125°C,兼具高性能与严苛环境适应性。

一、核心特性与器件分类

1. 共性核心特性

- 高采样率与分辨率 :

- 采样率:单通道最高 20.8GSPS(DES 模式)、双通道最高 10.4GSPS,支持 8/12/16 位输入分辨率(8 位对应 10.4GHz 信号带宽、12 位 7.5GHz、16 位 5GHz);

- 输出带宽:-3dB 带宽达 12GHz,可生成载波频率超 10GHz 的信号,支持 X 波段直接采样。

- 抗辐射与可靠性 :

- 全型号寄存器具备单粒子翻转(SEU)免疫能力;

- 满足 ASTM E595 释气规范,支持晶圆批次追溯,量产型号通过温度循环、湿度偏压测试,平均无故障时间(MTBF)达 10⁶小时以上。

- 高性能指标 (f_OUT=2.997GHz,DES2XL 模式,DEM/Dither 关闭):

- 噪声基底(小信号):-155dBFS/Hz;

- 无杂散动态范围(SFDR,-0.1dBFS):60dBc;

- 三阶互调失真(IMD3,-7dBFS 双音):-62dBc;

- 附加相位噪声(10kHz 偏移):-138dBc/Hz。

- 灵活数字功能 :

- 集成 4 个数字上变频器(DUC),支持 1x~256x 插值,64 位频率分辨率数控振荡器(NCO),可实现相干跳频与任意波形生成(AWG);

- 支持动态元素匹配(DEM)与抖动(Dither)功能,优化非线性失真,降低杂散信号。

- 高速接口与同步 :

- JESD204C 接口:支持 16 路通道,每路最高 12.8Gbps 速率,兼容 8b/10b 与 64b/66b 编码,Class C-S subclass-1 合规,支持确定性延迟与多器件同步;

- SYSREF 窗口功能:自动校准 SYSREF 时序,确保多器件同步精度。

2. 器件分类(按辐射等级与通道数)

系列器件按辐射耐受性与通道数分为多个型号,核心差异如下表:

| 型号 | 通道数 | 最高采样率(单通道 / DES 模式) | 单粒子闩锁(SEL) | 总电离剂量(TID) | 核心定位 |

|---|---|---|---|---|---|

| DAC39RF10-SP | 2 | 20.8GSPS | 120MeV-cm²/mg | 300krad(Si) | 抗辐射增强型,空间飞行级 |

| DAC39RFS10-SP | 1 | 20.8GSPS | 120MeV-cm²/mg | 300krad(Si) | 抗辐射增强型,空间飞行级 |

| DAC39RF10-SEP | 2 | 20.8GSPS | 43MeV-cm²/mg | 30krad(Si) | 耐辐射型,工业 / 近空间级 |

| DAC39RFS10-SEP | 1 | 20.8GSPS | 43MeV-cm²/mg | 30krad(Si) | 耐辐射型,工业 / 近空间级 |

二、封装与引脚功能

1. 封装规格

全系采用 17mm×17mm 256 引脚倒装芯片 BGA(FC-BGA)封装 ,底部裸露热焊盘(需与 PCB 接地铜皮充分焊接),热阻参数优化散热性能,具体如下:

| 热阻参数 | 数值(°C/W) | 说明 |

|---|---|---|

| 结到环境(RθJA) | 15.8 | 芯片结温到环境温度热阻 |

| 结到壳顶(RθJC (top)) | 0.9 | 芯片结温到封装顶部热阻 |

| 结到板(RθJB) | 4.2 | 芯片结温到 PCB 板热阻 |

2. 关键引脚分类与功能

引脚按功能分为电源与地、模拟输入 / 输出、数字控制、高速接口四类,核心引脚功能如下表:

| 引脚类别 | 关键引脚示例 | 类型 | 核心功能 |

|---|---|---|---|

| 电源与地 | VDDA18A/B(1.8V 模拟)、VEEAM18/BM18(-1.8V 模拟)、VSSCLK(时钟地) | 电源输入 | 模拟电源独立供电,降低噪声耦合;VSSCLK 单独接地,确保时钟信号稳定性 |

| 模拟输出 | DACOUTA±/B±(A12/A13、T12/T13) | 模拟输出 | 差分 DAC 输出,需符合输出合规电压(VDDA18A/B-0.5V~VDDA18A/B+0.5V)以保证性能 |

| 时钟与同步 | CLK±(D16/E16)、SYSREF±(M16/N16) | 数字输入 | CLK 为采样时钟(内建 100Ω 差分端接),SYSREF 为 JESD204C 同步参考(内建 100Ω 端接) |

| JESD204C 接口 | 0SRX± | 高速输入 | 16 路 SerDes 通道,含片内 AC 耦合电容与 100Ω 差分端接,支持 8b/10b/64b/66b 编码 |

| 控制接口 | SPI(SCLK/E8、SDI/D8、SDO/D7)、RESET/D6 | 数字 I/O | SPI 用于寄存器配置,RESET 为低有效硬件复位(需≥100ns 脉冲) |

三、电气规格与性能指标

1. 电源与功耗(典型值,TA=25°C,双通道,F_CLK=10.24GHz)

| 电源类型 | 电压范围 | 典型电流(正常模式) | 典型电流(掉电模式) |

|---|---|---|---|

| VDDA18A/B(模拟) | 1.71~1.89V | 75mA(双通道) | - |

| VEEAM18/BM18(模拟负电源) | -1.89~-1.71V | 123mA(双通道) | - |

| VDDDIG(数字) | 0.95~1.05V | 2263mA(双通道) | - |

| 总功耗(PDIS) | - | 3747mW(模式 1) | 165mW(睡眠模式) |

2. 静态性能指标(TA=25°C,VREF = 内部参考,I_FS_SWITCH=20.5mA)

| 参数 | 典型值 | 单位 | 说明 |

|---|---|---|---|

| 分辨率 | 16 | bits | 全型号一致 |

| 微分非线性(DNL) | ±2.2 | LSB | 全温度范围最大偏差 |

| 积分非线性(INL) | ±9 | LSB | 全温度范围最大偏差 |

| 满量程电流(I_FS_SWITCH) | 41 | mA | CUR_2X_EN=1 时,3.6kΩ RBIAS 电阻 |

| 满量程电流漂移 | -8.6 | uA/°C | 温度变化导致的电流偏差 |

| 输出端接电阻 | 102 | Ω | 差分输出端接,确保阻抗匹配 |

3. 动态性能指标(TA=25°C,F_CLK=10.24GHz,I_FS_SWITCH=20.5mA)

| 参数 | 测试条件 | 典型值 | 单位 |

|---|---|---|---|

| 无杂散动态范围(SFDR) | f_OUT=97MHz,NRZ 模式 | 85 | dBc |

| f_OUT=2997MHz,NRZ 模式 | 61 | dBc | |

| 三阶互调失真(IMD3) | f_OUT=97±10MHz,-7dBFS 双音 | -91 | dBc |

| f_OUT=2997±10MHz,-7dBFS 双音 | -64 | dBc | |

| 噪声谱密度(NSD) | f_OUT=97MHz,70MHz 偏移 | -158 | dBc/Hz |

| f_OUT=3997MHz,70MHz 偏移 | -148 | dBc/Hz | |

| 相位噪声(10kHz 偏移) | f_OUT=997MHz,NRZ 模式 | -143 | dBc/Hz |

四、核心功能与工作模式

1. DAC 输出模式

支持四种多 Nyquist 输出模式,适配不同频率范围需求,具体如下表:

| 输出模式 | 频率范围 | 峰值输出功率 | 关键特性 | 适用场景 |

|---|---|---|---|---|

| 非归零(NRZ) | 0~F_CLK/2 | 0dBFS | 标准零阶保持,适用于第一 Nyquist 区 | 中低频信号生成 |

| 归零(RTZ) | 0~F_CLK | -6dBFS | 半周期归零,第二 Nyquist 区损耗低 | 跨 Nyquist 区信号传输 |

| 射频(RF) | F_CLK/2~F_CLK | -2.8dBFS | 采样中期反转,第二 Nyquist 区平坦度最优 | 射频信号直接输出(X 波段) |

| 双沿采样(DES) | 0~F_CLK | 0dBFS | 时钟双沿采样,采样率翻倍,含 DES2XL(低通)/DES2XH(高通)子模式 | 超高速信号生成(20.8GSPS) |

2. 数字上变频器(DUC)

- 插值功能 :支持 1x~256x 插值(2x/3x/4x 等步进),通过多级 FIR 滤波器实现,通带纹波 <0.01dB,阻带衰减> 90dB;

- NCO 特性 :64 位频率分辨率,支持相位连续 / 相干 / 同步三种更新模式,可实现无杂散跳频,频率更新通过 SPI 或快速配置(FR)接口触发;

- 混频能力 :支持复信号到实信号 / 复信号的混频,1:1 缩放无饱和,适配多通道信号合成。

3. JESD204C 接口

- 编码与速率 :支持 8b/10b(≤12.8Gbps)与 64b/66b(≤12.8Gbps)编码,64b/66b 需强制扰码以保证时钟恢复;

- 多器件同步 :Subclass 1 合规,通过 SYSREF 窗口功能自动校准时序,弹性缓冲区(EB)确保确定性延迟;

- ** lane 配置 **:16 路 SerDes 可灵活映射,支持 lane 交叉开关(Crossbar)优化 PCB 布线,lane 速率通过 PLL 寄存器(REFDIV/MPY/RATE)配置。

4. 功耗控制模式

- 正常模式 :全功能启用,双通道总功耗典型 3747mW(F_CLK=10.24GHz);

- 睡眠模式 :MODE [1:0]=11,总功耗降至 165mW,仅保留 SPI 与温度传感器供电;

- 单通道模式 :双通道器件可配置为单通道工作,降低 VEE 与数字电源电流(如 DAC39RF10-SP 单通道模式功耗 2848mW)。

五、寄存器配置与接口

1. 核心寄存器功能(关键寄存器)

| 地址 / 寄存器组 | 核心功能 |

|---|---|

| JMODE 寄存器 | 配置 JESD204C 模式(编码方式、lane 数、分辨率),如 JMODE0 对应 16 位 8b/10b 16lane |

| DUC_L 寄存器 | 设置 DUC 插值因子(1x~256x),控制信号采样率提升倍数 |

| NCO_CONT/NCO_AR | NCO 更新模式:NCO_CONT=1 为相位连续,NCO_AR=1 为相位同步 |

| SYSREF_POS/SYSREF_SEL | SYSREF 窗口配置:SYSREF_POS 检测时序,SYSREF_SEL 选择最优采样位置 |

| DEM_DITH 寄存器 | 启用 DEM(动态元素匹配)与 Dither 功能,优化非线性失真 |

2. 配置接口

- SPI 接口 :3 线制(SCLK/SDI/SDO),最高 15.625MHz 时钟,支持寄存器读写,写操作 24 位帧(8 位地址 + 16 位数据),读操作需先发送读命令再接收数据;

- 快速配置(FR)接口 :支持 200MHz FRCLK,4 位数据(FRDI0~3),用于 NCO 频率快速更新,降低跳频延迟;

- 初始化流程 :上电→等待 5ms(电源稳定)→RESET 引脚复位(≥100ns)→配置 PLL(SerDes 速率)→配置 JESD204C 与 DUC→启用 SYSREF 同步。

六、应用设计建议

1. 典型应用场景

- 卫星通信(SATCOM) :20.8GSPS 采样率 + 12GHz 带宽,支持多载波射频信号生成,抗辐射特性适配空间环境;

- 相控阵天线 :4 个 DUC 支持多通道波束成形,JESD204C 同步确保多 DAC 相位一致性;

- 合成孔径雷达(SAR) :高 SFDR(60dBc@2.997GHz)与低相位噪声,满足雷达信号高保真需求;

- 高端测试仪器 :AWG 功能 + 任意波形生成,适配射频信号源、频谱分析仪等设备。

2. 硬件设计建议

(1)电源与去耦

- 模拟电源(VDDA18A/B、VEEAM18/BM18)采用 LDO(如 TI TPS7A8101)二次稳压,降低开关噪声;

- 关键电源引脚去耦:VDDA18 旁并联 10μF(钽电容)+0.1μF(陶瓷电容),VSSCLK 与 AGND 单点连接,避免数字噪声耦合;

- 电源序列:无严格时序要求,但需确保 VDD 先于 VEE 上电,防止器件损坏。

(2)PCB 布局

- 模拟区与数字区分区:DACOUTA±/B±(模拟)与 SRX±(数字)间距≥5mm,模拟地(AGND)与数字地(DGND)仅在热焊盘单点连接;

- 时钟与 SYSREF 布线:CLK± 与 SYSREF± 采用差分对布线,阻抗控制 100Ω,长度差 < 1mm,远离电源噪声源;

- 热焊盘处理:256BGA 底部热焊盘通过 4 个 0.3mm 过孔连接至内层地平面,确保散热效率。

(3)阻抗匹配与保护

- 模拟输出:DACOUTA±/B± 外接 2:1 巴伦(如 Mini-Circuits ADT1-1WT+)转换为单端 50Ω,匹配射频负载;

- ESD 防护:全引脚遵循 HBM±1000V、CDM±250V 防护规范,布局时增加 TVS 二极管(如 TI TPD4E001);

- 时钟输入:CLK± 推荐使用差分时钟源(如 TI CDCE6214),单端时钟需通过电阻分压将共模电压拉至 0.4V(CLK 最佳共模)。

-

10位电流输出数模转换器DAC100技术解析2026-04-16 181

-

探索DAC5675A - SP:高性能数模转换器的卓越之选2025-11-27 774

-

DAC3154 双通道、10位、500MSPS数模转换器(DAC)技术手册2025-11-14 1001

-

DAC39RFx10 系列产品技术文档总结2025-10-27 962

-

DAC5670-SP 14位2.4 GSPS数模转换器(DAC)数据表2024-07-30 509

-

DAC39RF12、DAC39RFS12双通道和单通道数模转换器(DAC)数据表2024-07-15 705

-

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位双通道和单通道多奈奎斯特数模转换器(DAC)数据表2024-07-12 688

-

DAC数模转换器介绍2023-03-22 4878

-

介绍DAC数模转换器以及DMA的使用2021-08-12 3696

-

数模转换器是什么2021-07-26 3302

-

DAC10QM:自含式数模转换器废弃数据表2021-04-16 828

-

数模转换器的基本原理及DAC类型简介2016-08-16 23771

全部0条评论

快来发表一下你的评论吧 !