ADC12DL2500技术文档总结

描述

ADC12DL500、ADC12DL1500 和 ADC12DL2500 是模数转换器 (ADC) 系列,在双通道模式下可采样高达 500MSPS、1.5GSPS 和 2.5GSPS,在单通道模式下采样高达 1GSPS、3GSPS 和 5GSPS。通道数(双通道模式)和采样率(单通道模式)的可编程权衡允许开发灵活的硬件,以满足高通道数或宽瞬时信号带宽应用的需求。

*附件:adc12dl2500.pdf

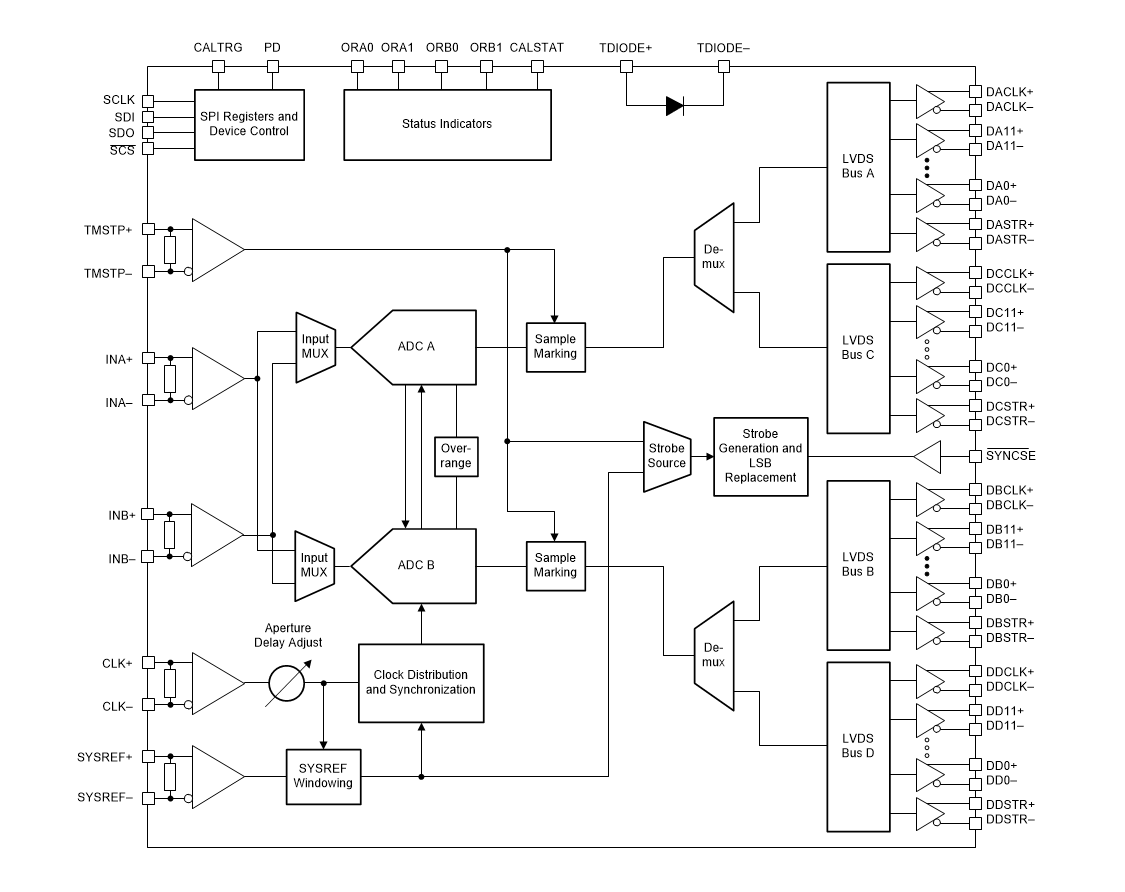

这些器件使用低延迟、低电压差分信号 (LVDS) 接口,用于对延迟敏感的应用或首选 LVDS 的简单性。该接口使用多达 48 个数据对、四个双倍数据速率 (DDR) 时钟和四个选通信号,排列在四个 12 位数据总线中。该接口支持高达 1.6Gbps 的信令速率。频闪信号简化了总线之间和多个设备之间的同步。选通在内部生成,可通过SYSREF输入在确定性时间复位。创新的同步功能(如无噪声孔径延迟 (TAD)调整和 SYSREF 窗口化)进一步简化了多器件同步。

特性

- ADC内核:

- 12 位分辨率

- 单通道模式下高达 1GSPS、3GSPS、5GSPS

- 双通道模式下高达 500MSPS、1.5GSPS、2.5GSPS

- 用于低幅度、高阶谐波的内部抖动

- 低延迟LVDS接口:

- 总延迟:< 10ns

- 多达 48 个数据对,速度为 1.6Gbps

- 四个DDR数据时钟

- 频闪信号简化了同步

- 本底噪声(无输入,VFS = 1VPP-DIFF):

- 双通道模式:-143.5、-148、-149.8dBFS/Hz

- 单通道模式:-146.2、-150.3、-152.2dBFS/Hz

- VCMI为0V的缓冲模拟输入:

- 模拟输入带宽 (–3dB):8GHz

- 满量程输入电压(VFS,默认):0.8VPP

- 无噪声光圈延迟 (TAD) 调节:

- 精确采样控制:19fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 易于使用的同步功能:

- 自动 SYSREF 定时校准

- 样品标记的时间戳

- 功耗:2.6、2.8、3W

参数

方框图

一、产品概述

ADC12DLx500 系列是德州仪器推出的高速 12 位模数转换器(ADC)家族,核心优势在于灵活的通道与采样率配置、低延迟 LVDS 接口及优异的信号处理能力,专为高带宽信号采集场景设计。该系列器件支持双通道与单通道模式切换,可适配示波器、电子战(SIGINT/ELINT)、激光雷达(LiDAR)、微波回传、汽车雷达测试、光谱分析等多样化应用,能满足宽瞬时信号带宽或多通道采集的硬件需求。

核心模式与采样率配置

| 型号 | 双通道模式采样率 | 单通道模式采样率 |

|---|---|---|

| ADC12DL500 | 最高 500MSPS | 最高 1GSPS |

| ADC12DL1500 | 最高 1.5GSPS | 最高 3GSPS |

| ADC12DL2500 | 最高 2.5GSPS | 最高 5GSPS |

二、核心特性

(一)ADC 核心与信号性能

- 精度与噪声

- 12 位分辨率,无失码,微分非线性(DNL)典型值 ±0.17LSB,积分非线性(INL)典型值 ±1.5LSB,保证信号转换精度;

- 低噪声特性:双通道模式下噪声谱密度(NSD)低至 - 143.5

-149.8dBFS/Hz,单通道模式下低至 - 146.2-152.2dBFS/Hz; - 动态性能优异:典型信噪比(SNR)56

57dBFS,无杂散动态范围(SFDR)最高 75dBFS,三阶互调失真(IMD3)低至 - 87dBc,有效位数(ENOB)约 8.89.2bits。

- 输入与带宽

- 模拟输入带宽达 8GHz(-3dB),支持 AC/DC 耦合,输入共模电压(VCMI)典型值 0V,差分输入满量程(VFS)默认 0.8VPP,可通过寄存器调整至 480~1040VPP;

- 内置输入缓冲器,隔离采样电容噪声,输入端集成 50Ω 终端电阻,简化外部电路设计。

(二)低延迟 LVDS 接口

- 接口配置 :最多 48 组数据对、4 路 DDR 时钟、4 路选通信号(Strobe),分为 4 个 12 位数据总线,信号速率最高 1.6Gbps,总延迟 < 10ns,适配 latency 敏感场景;

- 同步机制 :选通信号(Strobe)简化多总线 / 多器件同步,可通过 SYSREF 输入实现确定性复位;支持自动 SYSREF 时序校准、无噪声孔径延迟(TAD)调整(19fs 步进),解决高速同步难题;

- 灵活输出模式 :支持 12/11/10/8 位输出宽度,可选数据加扰功能(减少频谱峰值耦合),支持专用选通引脚、LSB 替换选通、全数据通道选通等多种同步方式,平衡性能与引脚资源。

(三)功能增强设计

- 校准与补偿 :支持前景校准(Foreground Calibration),自动优化线性度、增益与偏移,校准期间输出中值码(0x000);可独立调整输入偏移电压(±55mV 范围)、增益及输入终端电阻,适配不同系统误差需求;

- 过范围检测 :双通道模式下每通道配备 2 个可编程阈值(OVR_T0/OVR_T1),通过 ORA0/ORA1(通道 A)、ORB0/ORB1(通道 B)引脚输出状态,响应时间快,助力系统增益动态调整;

- 温度与参考 :内置温度监测二极管(TDIODE±),支持外部温度传感器接入;提供 1.1V 带隙基准电压输出(BG 引脚),输出电流 ±100μA,可用于系统参考校准。

三、器件信息

(一)型号与封装

| 型号 | 封装规格 | 关键参数 |

|---|---|---|

| ADC12DL500 | 17mm×17mm 256 球倒装芯片球栅阵列(FCBGA) | 双通道 500MSPS / 单通道 1GSPS,工作温度 - 40~85°C |

| ADC12DL1500 | 同规格 FCBGA | 双通道 1.5GSPS / 单通道 3GSPS,工作温度 0~85°C |

| ADC12DL2500 | 同规格 FCBGA | 双通道 2.5GSPS / 单通道 5GSPS,工作温度 0~85°C |

(二)热学特性

| 热参数 | 数值 | 单位 |

|---|---|---|

| 结到环境热阻(RθJA) | 16.5 | °C/W |

| 结到顶部外壳热阻(RθJC (top)) | 0.94 | °C/W |

| 结到板热阻(RθJB) | 5.4 | °C/W |

| 结到顶部特征参数(ΨJT) | 0.5 | °C/W |

| 结到板特征参数(ΨJB) | 5.1 | °C/W |

| 工作结温(TJ) | 最高 105 | °C |

| 存储温度范围 | -65~150 | °C |

四、电气规格

(一)电源与电压

- 推荐电源电压 :模拟电源 VA19(1.9V,范围 1.8

2.0V)、VA11(1.1V,范围 1.051.15V);数字电源 VD11(1.1V,范围 1.051.15V);LVDS 接口电源 VLVDS(1.11.9V,范围 1.05~2.0V); - 输入电压限制 :模拟输入(INA±/INB±)电压范围 - 1

1V,数字引脚(如 SYSREF±/TMSTP±)电压范围 - 0.31.4V,避免过压损坏器件。

(二)功耗特性(典型值,TA=25°C)

| 型号 | 工作模式 | 总功耗(典型值) | VA19 电流 | VA11 电流 | VD11 电流 | VLVDS 电流 |

|---|---|---|---|---|---|---|

| ADC12DL500 | 单通道(1GSPS) | 2.6W | 835mA | 185mA | 40mA | 389mA |

| ADC12DL500 | 双通道(500MSPS) | 2.72W | 913mA | 185mA | 35mA | 389mA |

| ADC12DL1500 | 单通道(3GSPS) | 2.99W | 833mA | 419mA | 188mA | 388mA |

| ADC12DL2500 | 单通道(5GSPS) | 3.12W | 911mA | 419mA | 169mA | 389mA |

| 所有型号 | 睡眠模式(PD 引脚高) | 0.1W | 33mA | 23mA | 3mA | 0mA |

(三)时序特性

- 孔径延迟(TAD) :典型值 360ps,支持精细调整(粗调 1.13ps / 步,细调 19fs / 步),无噪声干扰,适配多器件同步;

- 孔径抖动(TAJ) :均方根(rms)值 55~80fs,保证高速采样的时序稳定性;

- LVDS 输出时序 :DDR 时钟频率最高 800MHz,通道内时序偏差≤75ps,全通道偏差≤125ps,确保数据传输同步。

五、功能描述

(一)模拟输入与信号处理

- 输入保护与调整 :模拟输入内置钳位二极管,耐受最高 16.4dBm 峰值 RF 功率;支持输入满量程电压(VFS)精细调整(FS_RANGE_A/B 寄存器),适配不同幅度输入信号;

- ADC 核心架构 :采用 6 个 ADC 子核(Bank),双通道模式下 2 核一组 interleaving(2 路交织),单通道模式下 4 核一组 interleaving(4 路交织),提升采样率的同时优化动态性能;

- 内部抖动(Dither) :可开启 12 位内部抖动,抑制低幅度高次谐波,平衡 SNR 与杂散性能,抖动幅度与误差模式可通过寄存器配置。

(二)时钟与同步系统

- 时钟输入 :支持差分 / 单端时钟,差分模式 AC 耦合(推荐),单端模式 DC 耦合,时钟频率范围 500MHz~5GHz,占空比 30%~70%;内置时钟占空比校正器,降低外部时钟要求;

- SYSREF 同步 :SYSREF 信号用于多器件同步与确定性延迟,支持自动校准(SRC_EN 寄存器),通过调整 TAD 使内部时钟沿与 SYSREF 对齐;支持 SYSREF 窗口 ing(SYSREF_ZOOM),优化时序裕量;

- 孔径延迟调整(TAD Adjust) :支持时钟相位反转(TAD_INV)、粗调(256 级)与细调(256 级),总延迟范围随时钟频率变化,调整过程无额外噪声,适配外部交织扩展采样率。

(三)LVDS 数字接口

- 数据输出配置 :

- 输出模式:支持交错(Staggered)与对齐(Aligned)模式,交错模式减少输出切换干扰,对齐模式简化接收端时序;

- 引脚优化:可禁用冗余时钟 / 选通引脚(如 DCLKx_EN/STBx_EN),减少 PCB 布线;支持 LSB 替换选通(损失 1 位精度)或全通道选通(临时中断数据),平衡同步需求与性能;

- 数据加扰与测试 :支持 XOR 加扰(SCR 寄存器),降低重复数据的频谱峰值耦合;内置用户自定义测试模式(UPAT0~UPAT7 寄存器),可生成 8 样本重复图案,用于系统调试与链路验证。

(四)校准与电源管理

- 前景校准 :需暂停信号采样,自动校准各子核的线性度、增益与偏移,校准状态通过 CALSTAT 引脚或 FG_DONE 寄存器反馈;支持偏移校准(CAL_OS),修正输入缓冲器偏移,避免 DC 偏移与 fS/2 杂散;

- 电源 - down 模式 :PD 引脚或 MODE 寄存器可触发全局掉电,掉电时 LVDS 输出禁用,恢复后需等待数据管道刷新;支持单通道 / 子核独立掉电(PD_ACH/PD_BCH),优化功耗。

六、应用设计指南

(一)电源设计

- 电源架构 :模拟电源(VA19/VA11)与数字电源(VD11/VLVDS)独立供电,推荐 “开关稳压器 + LDO” 组合(如 TPS7H4002-SP+TPS7A4501-SP),避免数字噪声耦合至模拟电路;

- 去耦配置 :VA19/VA11/VD11/VLVDS 引脚旁并联 10μF+0.1μF 陶瓷电容,BG 引脚旁并联 10μF+0.1μF 电容,均需靠近引脚放置,减少寄生电感。

(二)PCB 布局

- 信号布线 :

- 模拟输入(INA±/INB±)与时钟(CLK±):100Ω 差分布线,长度匹配误差 < 5mil,避免过孔,远离数字区域;

- LVDS 输出(DAx±/DBx± 等):100Ω 紧密耦合差分对,与模拟区域间距≥2mm,减少串扰;

- 接地与散热 :模拟地(AGND)与数字地(DGND)单点连接,散热焊盘(DAP)直接接地(建议多过孔),PCB 堆叠采用 “电源层 - 接地层 - 信号层” 结构,提升散热与抗干扰能力。

(三)初始化流程

- 上电:同时施加 VA19/VA11/VD11/VLVDS,等待 2ms 使内部参考稳定;

- 时钟与模式配置:施加采样时钟,通过 SPI 配置 DES_EN(单 / 双通道)、LDEMUX(解复用倍数)、LALIGNED(输出对齐);

- 校准:触发前景校准(CAL_TRIG 引脚或 CAL_SOFT_TRIG),等待 CALSTAT 或 FG_DONE 寄存器置 1,完成校准;

- 同步与输出:配置 SYSREF 同步(自动校准或手动窗口 ing),启用 LVDS 输出(LVDS_EN),确认数据正常输出。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深入剖析ADC12DL080:高性能12位A/D转换器的设计与应用2025-12-02 1376

-

ADC12DL065:高性能12位A/D转换器的深度解析2025-12-01 683

-

ADC12D1000RF 12 位高采样率 RF 采样 ADC 技术文档总结2025-11-18 952

-

ADC12DL3200 技术规格与应用总结2025-11-05 693

-

ADC12DLx500 系列技术文档总结2025-10-27 808

-

ADC12DL040的clk由系统给出,是3.3V的电平,直接接到ADC12DL040的3.3V输入口有没有问题?2024-11-21 354

-

ADC12DL066单芯片CMOS模数转换器数据表2024-07-22 432

-

ADC12DL3200 6.4GSPS单通道或3.2GSPS双通道12位模数转换器(ADC)数据表2024-07-15 517

-

ADC12DL065,pdf datasheet (Dual2009-10-10 614

全部0条评论

快来发表一下你的评论吧 !