ADS1288 技术文档总结

描述

该ADS1288是一款 32 位、低功耗、模数转换器 (ADC),具有可编程增益放大器 (PGA) 和有限脉冲响应 (FIR) 滤波器。该ADC专为地震设备苛刻要求而设计,需要低功耗以延长电池运行时间。

低噪声PGA将ADC动态范围扩展到增益1至64。PGA 允许直接连接到检波器和变压器耦合水听器,无需外部放大器。可选的单位增益缓冲器可降低功耗。

*附件:ads1288.pdf

该ADC集成了一个高分辨率的δ-Σ(ΔΣ)调制器和一个具有可编程相位响应的FIR滤波器。高通滤波器从信号中去除直流和低频成分。采样率转换器可补偿时钟频率误差,频率精度高达7ppb。

该ADC支持3.3V工作电压,以最大限度地降低器件功耗。缓冲模式工作时功耗为3mW(典型值),PGA模式工作时功耗为5mW(典型值)。

该ADC采用紧凑的5mm×5mm VQFN封装,在–40°C至+85°C环境温度范围内完全额定。

特性

- 功耗:

- PGA 工作:5mW(典型值)

- 缓冲器作:3mW(典型值)

- 动态范围:

- PGA增益:1, 500SPS(122dB,典型值)

- 缓冲器作:500SPS(122dB,典型值)

- 总谐失真:< –120dB(典型值)

- CMRR:120dB(典型值)

- 灵活的数字滤波器:

- 可选 sinc + FIR + IIR

- 线性或最小相位

- 高通滤波器

- 数据速率:125SPS 至 2000SPS

- PGA 增益:1 到 64

- SYNC 输入

- 时钟误差补偿

- 双通道多路复用器

- 失调和增益校准

- 通用数字 I/O

- 模拟电源作:5V、3.3V 或 ±2.5V

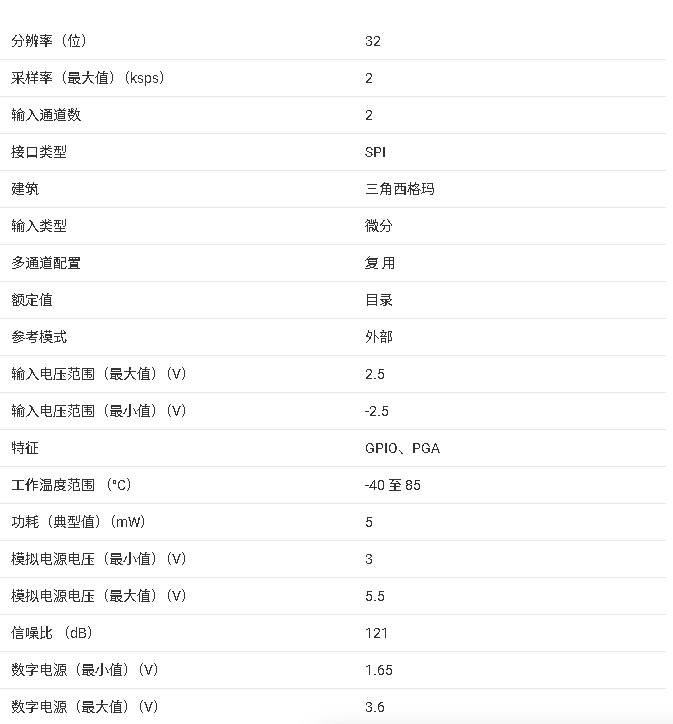

参数

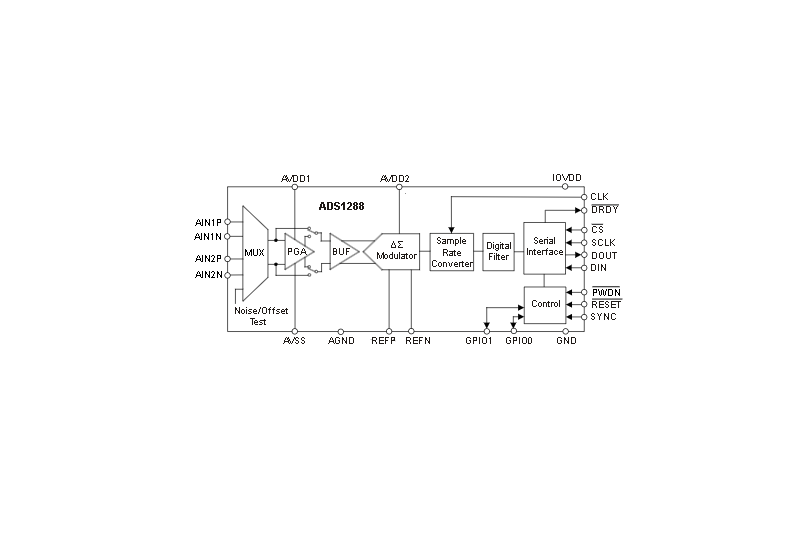

方框图

一、产品概述

ADS1288 是德州仪器推出的 32 位高精度 ΔΣ 模数转换器(ADC) ,专为地震监测、能源勘探、地球科学等对低功耗与高分辨率要求严苛的场景设计。其核心优势在于低功耗运行(PGA 模式典型 5mW、缓冲模式典型 3mW)、122dB 高动态范围及灵活的数字滤波功能,可直接连接地震检波器、变压器耦合水听器等传感器,无需外部放大器,能有效延长电池供电设备的运行时间。

二、核心特性

(一)精度与动态性能

- 分辨率与线性度 :32 位输出分辨率,支持 1~64 倍可编程增益放大器(PGA),积分非线性(INL)、微分非线性(DNL)误差极小,确保微弱信号精准转换;

- 动态范围 :500SPS 采样率下,PGA 模式与缓冲模式动态范围均达 122dB(典型值) ,总谐波失真(THD)< -120dB(典型值),共模抑制比(CMRR)120dB(典型值),可有效抑制环境噪声与共模干扰;

- 噪声性能 :PGA 增益 16 时输入电压噪声密度低至 2.5nV/√Hz,输入电流噪声密度低至 1.4~3pA/√Hz(典型值),适配高阻抗传感器信号采集。

(二)灵活的信号调理与滤波

- 可编程增益与缓冲

- PGA 支持 1、2、4、8、16、32、64 共 7 档增益,其中 1

16 倍为模拟增益,3264 倍为数字增益; - 可禁用 PGA 切换至 ** unity-gain 缓冲模式 **,降低功耗的同时支持 ±2.5VPP 宽输入范围(3.3V 供电时需用缓冲模式)。

- PGA 支持 1、2、4、8、16、32、64 共 7 档增益,其中 1

- 数字滤波系统

- 三级滤波架构 :包含可变抽取率的 5 阶 sinc 滤波器、固定抽取率(32 倍)的 FIR 滤波器(支持线性 / 最小相位选择)、一阶 IIR 高通滤波器;

- 滤波特性 :FIR 滤波器通带纹波 ±0.003dB,阻带衰减 135dB,可有效滤除低频干扰与高频噪声;高通滤波器(HPF)截止频率可编程(0.1~10Hz),能去除直流分量与低频漂移;

- 采样率适配 :数据率(fDATA)可在 125SPS~2000SPS 间调节,不同数据率对应不同滤波带宽(如 500SPS 时,-3dB 带宽约 206.5Hz)。

(三)低功耗与多供电适配

- 功耗控制 :PGA 模式典型功耗 5mW,缓冲模式典型功耗 3mW,掉电模式电流仅 1~5μA,支持软件待机(STANDBY)与硬件掉电(PWDN 引脚);

- 供电灵活性 :模拟供电(AVDD1/AVDD2)支持 3.3V、5V 或 ±2.5V,数字 I/O 供电(IOVDD)支持 1.65

1.95V 或 2.73.6V,适配不同系统电源架构。

(四)同步与校准功能

- 同步机制 :支持 SYNC 引脚同步(脉冲同步 / 连续同步)与软件同步命令,可实现多器件协同采集,同步后数字滤波器自动重启以保证数据时序一致性;

- 校准功能 :内置 24 位偏移校准寄存器与 24 位增益校准寄存器,支持自动校准(OFSCAL/GANCAL 命令)与手动校准,校准范围覆盖 ±6% 满量程(FSR),可补偿温漂与器件误差;

- 时钟误差补偿 :采样率转换器(SRC)支持 ±244ppm 时钟频率误差补偿,分辨率达 7.45ppb,确保高频率精度场景下的数据准确性。

三、器件信息

(一)封装与尺寸

| 型号 | 封装类型 | 尺寸 | 引脚数 | 关键参数 |

|---|---|---|---|---|

| ADS1288 | 32 引脚 VQFN(RHB 封装) | 5mm×5mm | 32 | 工作温度 - 40~85°C,散热焊盘需连接 AVSS(最负电源) |

(二)热学特性

| 热参数 | 数值(32 引脚 VQFN) | 单位 |

|---|---|---|

| 结到环境热阻(RθJA) | 30 | °C/W |

| 结到顶部外壳热阻(RθJC (top)) | 19.4 | °C/W |

| 结到板热阻(RθJB) | 10.9 | °C/W |

| 工作结温(TJ) | 最高 105 | °C |

| 存储温度范围 | -60~150 | °C |

四、电气规格

(一)供电与电压

| 供电引脚 | 功能 | 推荐电压范围 | 备注 |

|---|---|---|---|

| AVDD1 | PGA 与缓冲器正供电 | 3~5.25V(相对 AVSS) | 单供电时 AVSS 接 GND,双供电时支持 ±2.5V |

| AVDD2 | 调制器正供电 | 2.375~5.25V(相对 AGND) | 可与 AVDD1 共接以简化供电 |

| AVSS | PGA 负供电 | 0V(单供电)/-2.625~0V(双供电) | 需与 AGND 单点连接 |

| IOVDD | 数字 I/O 与内核供电 | 1.65 | 1.65~1.95V 时可与 CAPD 引脚短接(禁用内部 LDO) |

(二)输入特性

- 模拟输入 :2 路差分输入(AIN1±/AIN2±),输入范围 ±VREF / 增益(VREF 典型 2.5V),PGA 模式输入电压需满足 AVSS+1.1V

AVDD1-0.85V,缓冲模式支持 AVSS+0.1VAVDD1-0.1V; - 参考电压 :差分参考输入(REFP/REFN),推荐 2.5V(范围 2.4~2.6V),参考输入电流 80μA/V(典型值),需外接 0.1μF+10μF 电容滤波。

(三)时序与采样特性

- 时钟输入 :CLK 引脚需接入 3~4.15MHz 时钟(推荐 4.096MHz 晶振),时钟抖动需极小以避免性能劣化;

- 采样率与延迟 :数据率(fDATA)125~2000SPS,线性相位 FIR 滤波器群延迟 31/fDATA,最小相位 FIR 滤波器建立时间 62/fDATA(如 500SPS 时群延迟 62μs);

- 同步与复位时序 :SYNC 引脚高电平需保持 2 个 CLK 周期,RESET 引脚低电平需保持 2 个 CLK 周期,确保器件稳定重启。

五、功能模块详解

(一)模拟前端与信号调理

- 输入多路复用器(MUX) :支持 2 路差分输入切换,内置短路测试模式(0Ω/400Ω 短路),可用于 offset 与噪声自检,400Ω 模式可模拟地震检波器热噪声;

- PGA 与缓冲器 :PGA 采用斩波稳定架构,降低 1/f 噪声与输入失调电压(校准后失调误差 ±1μV);缓冲器由电荷泵提升供电电压,扩展输入动态范围;

- 输入保护 :模拟输入内置 ESD 钳位二极管,耐受 AVSS-0.3V~AVDD1+0.3V 过压,建议系统级增加 TVS 管(如 TVS0701)防护 ESD 事件。

(二)ΔΣ 调制器与数字滤波

- 调制器 :多比特 ΔΣ 架构,通过噪声整形将量化噪声推至高频,采样频率 fMOD= fCLK/4(4.096MHz 时钟时为 1.024MHz),过载时恢复特性稳定,无数据丢失风险;

- FIR 滤波器 :4 级结构(2 级半带滤波 + 2 级整形滤波),线性相位模式保证多频信号无相位失真,最小相位模式降低延迟(如 500SPS 时延迟 124μs);

- IIR 高通滤波器 :截止频率通过 HPF [15:0] 寄存器编程,可快速去除直流偏移(如 0.1Hz 截止频率适用于长期地震监测)。

(三)数字接口与控制

- SPI 接口 :4 线 SPI(CS、SCLK、DIN、DOUT),支持模式 0(CPOL=0、CPHA=0),DRDY 引脚(低有效)指示数据就绪,可直接读取数据或通过命令(RDATA)重读历史数据;

- 命令集 :支持唤醒(WAKEUP)、待机(STANDBY)、同步(SYNC)、复位(RESET)、校准(OFSCAL/GANCAL)等命令,寄存器读写支持多字节连续操作;

- 通用 I/O(GPIO) :2 路 GPIO 引脚(GPIO0/GPIO1),可配置为输入或输出,用于控制外部开关或诊断测试,未使用时需下拉避免浮空。

(四)校准与补偿

- 偏移校准 :短接输入后发送 OFSCAL 命令,81 个转换周期后完成校准,OFFSET [23:0] 寄存器自动更新补偿值;

- 增益校准 :施加满量程校准信号(如 2.4V@增益 1),发送 GANCAL 命令,校准后 GAIN [23:0] 寄存器值确保输出与输入信号匹配;

- HPF 初始化 :启用高通滤波器时,可将 OFFSET 寄存器值作为 HPF 累加器初始值,缩短滤波器建立时间(无需等待直流分量自然衰减)。

六、应用设计指南

(一)电源与去耦设计

- 供电架构 :模拟电源(AVDD1/AVDD2)与数字电源(IOVDD)独立布线,推荐 “线性稳压器(LDO)+ 电容去耦” 组合(如 AVDD1 用 TPS7A4700),避免数字噪声耦合至模拟电路;

- 去耦配置 :AVDD1/AVDD2 引脚旁并联 1μF+0.1μF 陶瓷电容,IOVDD 旁并联 1μF+0.1μF 电容,CAPD(LDO 输出)旁并联 220nF 电容,均需靠近引脚放置以减少寄生电感。

(二)PCB 布局要点

- 信号隔离 :模拟输入(AIN1±/AIN2±)、参考电压(REFP/REFN)与时钟(CLK)布线远离数字电路(如 MCU、SPI 线),差分信号线长度匹配误差 < 5mil,阻抗控制为 100Ω;

- 接地处理 :模拟地(AGND)与数字地(DGND)单点连接(推荐在 ADC 下方),散热焊盘连接至 AVSS(单供电时接 AGND),避免地环路;

- 关键电容 :PGA 电容(CAPP/CAPN)需用 10nF C0G 材质,缓冲器电容(CAPBP/CAPBN)用 47nF C0G 材质,电荷泵电容(CAPC)用 4.7nF/10V 电容,确保滤波性能稳定。

(三)典型应用电路

- 地震检波器接口 :检波器信号经 20kΩ termination 电阻(提供偏置电流回路)接入 AIN1±,REF6225 提供 2.5V 参考电压,OPA391 缓冲参考电压用于信号电平偏移(将共模电压设为 AVDD1/2),BAS70 二极管防护输入过压;

- 校准与测试 :通过 DAC1282 生成低失真测试信号,接入 ADC 输入以验证 THD 性能,测试时可将 CAPP/CAPN 电容增至 10nF 优化性能。

七、器件与文档支持

(一)订购信息与封装

| 订购型号 | 封装 | 数量 | RoHS 合规 | 工作温度 |

|---|---|---|---|---|

| ADS1288IRHBR | 32 引脚 VQFN(5mm×5mm) | 3000 片 / 卷 | 是 | -40~85°C |

| ADS1288IRHBT | 32 引脚 VQFN(5mm×5mm) | 250 片 / 卷 | 是 | -40~85°C |

(二)ESD 与可靠性

- ESD 防护:人体放电模型(HBM)±2000V,带电器件模型(CDM)±1000V,操作需遵循静电防护流程;

- 文档支持:可通过 TI 官网订阅文档更新,技术支持通过 TI E2E™论坛获取,包含参考设计、常见问题解答及布局指南。

八、补充说明

- 温度影响 :-40

85°C 工作范围内,增益漂移仅 2ppm/°C(典型值),偏移漂移 0.51μV/°C,定期校准可进一步补偿温漂; - 多器件同步 :多片 ADS1288 可通过 SYNC 引脚或同步命令实现协同采集,需确保 CLK 与 SYNC 信号时序一致,避免采样偏差;

- 传感器匹配 :适配 1000~5000Ω 阻抗的地震检波器,当传感器阻抗为 5000Ω 时,需关注电流噪声 × 阻抗带来的额外噪声(典型增加 0.22μV),可通过 PGA 增益提升抵消。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS1115-Q1 汽车级模数转换器技术文档总结2025-11-18 820

-

ADS1262/ADS1263 32 位高精度 ADC 技术文档总结2025-11-11 2494

-

ADS7056 技术文档核心总结2025-11-07 690

-

ADS7067 技术文档总结2025-10-30 1005

-

ADS131B23 技术文档总结2025-10-29 831

-

ADS9817 技术文档总结2025-10-27 793

-

ADS9212 技术文档总结2025-10-24 686

-

Texas Instruments ADS1288低功耗Δ-Σ ADC数据手册2025-08-02 1560

-

FM1288调试过程是怎样的2022-01-07 1282

-

DC1288A-设计文件2021-06-16 384

-

BLE技术总结文档2015-10-29 813

全部0条评论

快来发表一下你的评论吧 !