DAC61401技术文档总结

描述

16位DAC81401和12位DAC61401(DACx1401)器件是引脚兼容的单通道、缓冲、高压输出数模转换器(DAC)系列,集成了2.5V内部基准电压源。这些器件指定为单调,并提供小于1LSB(最大值)的卓越线性度。

DACx1401 提供 ±20V、±10V、±5V 的双极性输出电压,以及 40V、10V 和 5V 的满量程单极性输出电压。DAC 输出范围是可编程的。

*附件:dac61401.pdf

DACx1401 集成了一个上电复位 (POR) 电路,可为 DAC 输出供电,并使器件保持掉电模式,直到输出使能。

与器件的通信通过与行业标准微处理器和支持 1.7V 至 5.5V作的微控制器兼容的高速 4 线串行接口完成。

DACx1401 的工作温度范围为 –55°C 至 +125°C,采用小型 16 引脚 QFN 和 20 引脚 TSSOP 封装。

特性

- 卓越性能:1LSB INL/DNL(最大)

- 超低毛刺能量:1nV-s

- 宽电源:

- 单极模式:+4.5V 至 +41.5V

- 双极性模式:±4.5V 至 ±21.5V

- 14 个用户可编程输出范围

- ±5V、±10V、±20V

- 0V 至 5V、0V 至 10V、0V 至 20V、0V 至 40V

- 20% 超量程(±20V 和 0V 至 40V 除外)

- 集成 10ppm/°C、2.5V 精密基准电压源

- 可靠性特点:

- 循环冗余校验 (CRC)

- 故障引脚

- 50MHz、4线SPI兼容接口

- 回读

- 菊花链

- 温度范围:–55°C 至 +125°C

- 包:

- 20 引脚 TSSOP (PW)

- 16引脚WQFN(RTE)

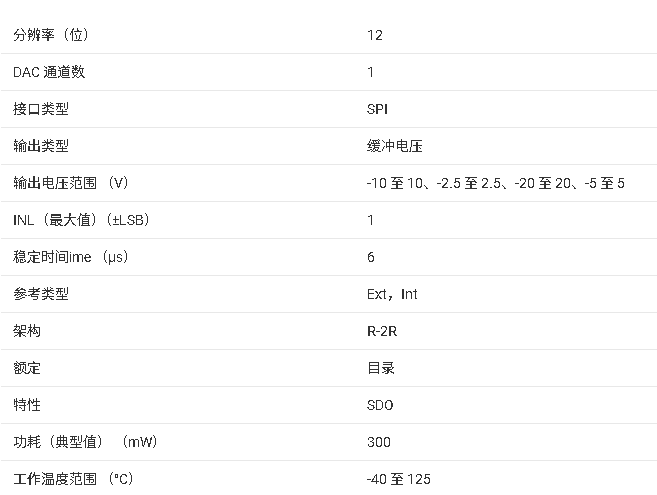

参数

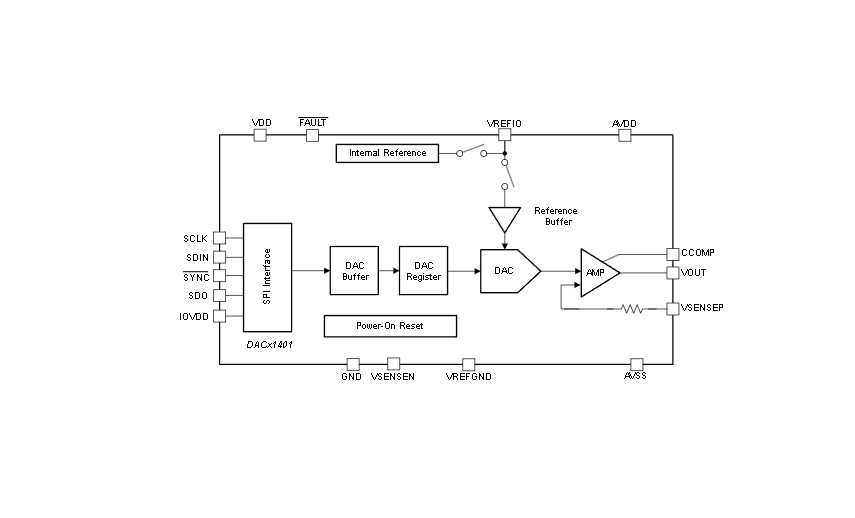

方框图

一、产品概述

DAC61401(12 位)与 DAC81401(16 位)是德州仪器推出的单通道高压输出数模转换器(DAC) 系列,核心优势在于高精度(INL/DNL 最大 1LSB)、宽输出范围(单极性 040V / 双极性 ±20V)及集成精密基准源,专为半导体测试、工业控制、实验室仪器等高压高精度场景设计。通过可编程增益输出缓冲、SPI 接口及故障检测功能,在简化系统设计的同时,确保全温域(-55125°C)下的稳定性与可靠性。

二、核心特性

(一)高精度与高压输出

- 分辨率与线性度 :DAC61401 为 12 位,DAC81401 为 16 位,两者均保证单调特性,积分非线性(INL)与微分非线性(DNL)最大 1LSB,全温域总未调整误差(TUE)最大 0.05% FSR,满足精密测量需求;

- 输出范围 :支持 14 种用户可编程输出范围,覆盖单极性(0

5V/10V/20V/40V,部分范围支持 20% 超量程,如 05V 可扩展至 0~6V)与双极性(±5V/±10V/±20V),适配不同高压驱动场景; - 动态性能 :超低毛刺能量(1nV・s),5V 量程下建立时间 7μs(±2LSB),40V 量程下 22μs(±2LSB),压摆率最高 4V/μs(非 40V 量程),确保高速响应。

(二)低功耗与灵活供电

- 功耗优化 :正常模式下模拟供电电流(IAVDD)最大 1.6mA,数字供电电流(IVDD)最大 2.5mA,全局掉电模式功耗仅 10μA,支持分模块掉电(如关闭内部基准、DAC 输出)进一步降低功耗;

- 供电配置 :需四电源供电,模拟正电源(AVDD)4.5

41.5V、模拟负电源(AVSS)-21.50V(双极性模式需负电源)、数字核心电源(VDD)4.55.5V、接口电源(IOVDD)1.75.5V,电源序列无强制要求,简化系统供电设计。

(三)集成精密基准与故障防护

- 内部基准 :集成 2.5V 精密基准源,温度漂移最大 10ppm/°C,输出噪声(0.1~10Hz)典型值 30μVpp,支持外部基准输入(VREFIO 引脚),适配更高精度需求场景;

- 故障检测 :具备循环冗余校验(CRC)、温度告警(结温超 140°C 触发)、DAC 忙状态指示功能,FAULT 引脚(开漏输出)可配置为故障告警输出,支持 CRC 错误、温度超限、DAC 忙等多触发源;

- 可靠性设计 :输出短路保护(短路电流限制 40mA),ESD 防护符合 HBM±1000V/CDM±500V 标准,确保工业环境下的抗干扰能力。

(四)灵活的数字接口与控制

- SPI 接口 :支持 50MHz 高速 4 线 SPI(SCLK/SDIN/SDO/SYNC),兼容 1.7~5.5V 逻辑电平,支持寄存器读写、数据回读及菊花链(Daisy-Chain)多器件级联,适配多通道同步控制;

- 配置功能 :通过寄存器可配置输出范围、基准源(内部 / 外部)、掉电模式、CRC 校验等,支持软件复位与软件清除(清零代码 / 中量程代码),适配动态系统调整需求。

三、器件信息与电气规格

(一)型号差异与封装

| 型号 | 分辨率 | 封装类型 | 引脚数 | 工作温度 | 关键差异 |

|---|---|---|---|---|---|

| DAC61401 | 12 位 | 20 引脚 TSSOP(PW)、16 引脚 WQFN(RTE) | -55~125°C | 无超量程扩展至 ±20V/0~40V,功耗较 16 位型号低约 15% | |

| DAC81401 | 16 位 | 20 引脚 TSSOP(PW)、16 引脚 WQFN(RTE) | -55~125°C | 支持全范围超量程,更高分辨率,适合精密高压控制 |

(二)热学特性(典型值)

| 封装类型 | 结到环境热阻(RθJA) | 结到顶部外壳热阻(RθJC (top)) | 结到板热阻(RθJB) |

|---|---|---|---|

| 20 引脚 TSSOP(PW) | 36.0°C/W | 21.7°C/W | 17.9°C/W |

| 16 引脚 WQFN(RTE) | 19.0°C/W | 30.2°C/W | 18.9°C/W |

(三)核心电气参数(TA=-40~125°C,AVDD=15V,AVSS=-15V,VREF=2.5V)

| 参数 | DAC61401(12 位) | DAC81401(16 位) | 测试条件 |

|---|---|---|---|

| INL(最大) | 1LSB | 1LSB | 全量程,-40~125°C |

| DNL(最大) | 1LSB | 1LSB | 全量程,-40~125°C |

| 增益误差(最大) | ±0.075%FSR | ±0.075%FSR | 外部基准,25°C |

| 增益温度漂移 | ±3ppm/°C | ±3ppm/°C | 外部基准 |

| 输出噪声(0.1~10Hz) | 30μVpp | 25μVpp | 10V 量程,内部基准 |

| 输出电流能力 | ±10mA(AVDD≤5.5V) | ±10mA(AVDD≤5.5V) | 负载电流范围,保证线性 |

| 电源抑制比(PSRR-AC) | 75dB | 75dB | 60Hz,±10V 输出 |

四、功能模块详解

(一)模拟输出与基准模块

- R-2R 梯形 DAC 架构

- 采用分段式 R-2R 梯形网络,配合专用基准缓冲器,确保输入阻抗恒定(参考引脚 VREFIO 阻抗典型值 50kΩ),通过生产校准实现低非线性;

- 输出缓冲放大器支持轨到轨输出,单极性模式下输出阻抗 0.05Ω,双极性模式下 0.05Ω,负载调整率 50μV/mA,保证大负载下的电压稳定性。

- 基准源配置

- 内部基准 :默认掉电状态,需通过 GENCONFIG 寄存器(0x04)启用,输出 2.5V(±0.1% 精度),支持 5mA 负载电流,VREFIO 引脚需并联 150nF 滤波电容;

- 外部基准 :需将内部基准掉电,外部 2.5V 基准接入 VREFIO 引脚,推荐使用高精度基准源(如 REF5025),此时增益误差温度漂移降至 - 35ppm/°C,提升长期稳定性。

- 高压输出与保护

- 输出级支持 ±15mA 驱动电流(AVDD>5.5V 时),具备 1.5V 电源裕量(输出离电源轨 1.5V 内仍保证线性);

- 短路保护:输出短路至 AVSS/AVDD 时,电流限制 40mA(AVDD>5.5V),避免器件损坏,短路状态下结温可能超上限,需避免长期短路。

(二)数字信号处理与控制

- 可编程增益输出

- 输出增益随量程自动配置,如 0~5V 量程增益 2.0、±5V 量程增益 4.0、40V 量程增益 16.0,输出电压计算公式如下:

- 单极性:VOUT =2NCODE**×VREFIO ×GAIN**(CODE 为十进制输入代码,N 为分辨率)

- 双极性:VOUT =(2N2**×CODE**− 1 )×VREFIO**×GAIN**

- 支持负载电压 sensing(VSENSEP 引脚),通过反馈补偿 PCB 线路压降,确保负载端电压精度。

- 输出增益随量程自动配置,如 0~5V 量程增益 2.0、±5V 量程增益 4.0、40V 量程增益 16.0,输出电压计算公式如下:

- 故障检测与告警

- 温度告警 :结温超 140°C 时触发热关断,TEMP-ALM bit 置 1,DAC 输出进入掉电模式,需通过 ALM-RESET bit 清除告警;

- CRC 校验 :启用后 SPI 帧扩展为 32 位(含 8 位 CRC-8 校验),CRC 错误时 CRC-ALM bit 置 1,FAULT 引脚可配置为低电平告警;

- DAC 忙指示 :DAC 更新期间 DAC-BUSY bit 置 1,FAULT 引脚可配置为忙状态指示,避免连续更新导致数据错误。

- 掉电模式

- 支持全局掉电(DEV-PWDWN)与 DAC 单独掉电(DAC-PWDWN),掉电时 DAC 输出通过 10kΩ 电阻接地,寄存器数据保持,恢复后输出恢复至掉电前值;

- 掉电电流:AVDD/AVSS 掉电电流最大 10μA,VDD/IOVDD 掉电电流最大 10μA,适合低功耗待机场景。

(三)SPI 接口与寄存器控制

- 多接口模式

- 标准 SPI :24 位帧(1 位 R/W+1 位保留 + 6 位地址 + 16 位数据),支持读写寄存器,SCLK 最高 50MHz(IOVDD=2.7~5.5V 时);

- 菊花链模式 :多器件通过 SDO 级联,需满足 24×N 个 SCLK 周期(N 为器件数),SYNC 高电平时数据锁存至各器件;

- CRC 模式 :32 位帧(1 位 R/W+1 位 CRC-ERROR+6 位地址 + 16 位数据 + 8 位 CRC),用于噪声环境下确保通信完整性。

- 关键寄存器 | 地址(十六进制)| 寄存器名称 | 功能描述 ||----|----|----||0x02|STATUS | 状态寄存器,显示 CRC 告警、DAC 忙、温度告警状态 ||0x03|SPICONFIG|SPI 配置,控制故障引脚触发源、掉电模式、CRC 使能 ||0x04|GENCONFIG | 通用配置,控制内部基准掉电 / 使能 ||0x0A|DACRANGE | 输出量程配置,4 位字段选择 14 种输出范围 ||0x0E|TRIGGER | 触发寄存器,支持软件复位、软件清除、告警清除 ||0x10|DAC|DAC 数据寄存器,存储 16 位输入代码(12 位型号高 4 位无效)|

五、典型应用场景

(一)半导体测试与 ATE 设备

- 应用架构 :DAC81401 通过 SPI 接收 FPGA 配置指令,输出 0

40V 高压信号,经外部运算放大器(如 OPA593)增益扩展至 080V,驱动半导体测试探针;VSENSEP 引脚反馈负载电压,补偿线路压降;CRC 校验确保配置指令无误,温度告警防止器件过热; - 关键配置 :启用内部基准(2.5V),配置 DAC 量程为 0

20V,外部放大器增益 4 倍,实现 080V 输出;FAULT 引脚配置为温度告警与 CRC 错误触发,确保测试过程稳定; - 性能优化 :CCOMP 引脚并联 470pF 电容,支持 1μF 负载电容,建立时间 1.2ms(±2LSB),满足测试设备的高压快速切换需求。

(二)工业 PLC 模拟输出模块

- 应用架构 :DAC61401 接收 PLC 主机指令,输出 4

20mA 对应电压信号(如 010V),经电压 - 电流转换器(OPA333+NPN 三极管)转换为 4~20mA 电流信号,驱动远程执行器;SPI 接口支持菊花链,实现多通道同步输出; - 关键配置 :选择双极性 ±10V 量程,软件清除功能确保上电时输出中量程(0V),避免执行器误动作;掉电模式用于待机节能,恢复后快速输出目标值;

- 可靠性设计 :FAULT 引脚外接上拉电阻,监测 DAC 忙状态,避免主机连续发送更新指令;TVS 管(36V 双向)并联于 VOUT 引脚,防护 ESD 与电压瞬变。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC38RF80 系列技术文档核心总结2025-11-07 794

-

DAC53204-Q1 与 DAC63204-Q1 技术文档总结2025-10-29 820

-

DAC39RFS10-SEP产品技术文档总结2025-10-27 869

-

DAC60516 ADC 产品文档总结2025-10-23 805

-

RT-Thread文档_DAC 设备2023-02-22 646

-

基于dac0832的波形发生器设计与实现2021-09-17 1263

-

DSP教程---ADC和DAC2021-09-16 1466

-

PWM DAC文档2016-05-03 705

-

BLE技术总结文档2015-10-29 813

全部0条评论

快来发表一下你的评论吧 !