ADS9817 技术文档总结

描述

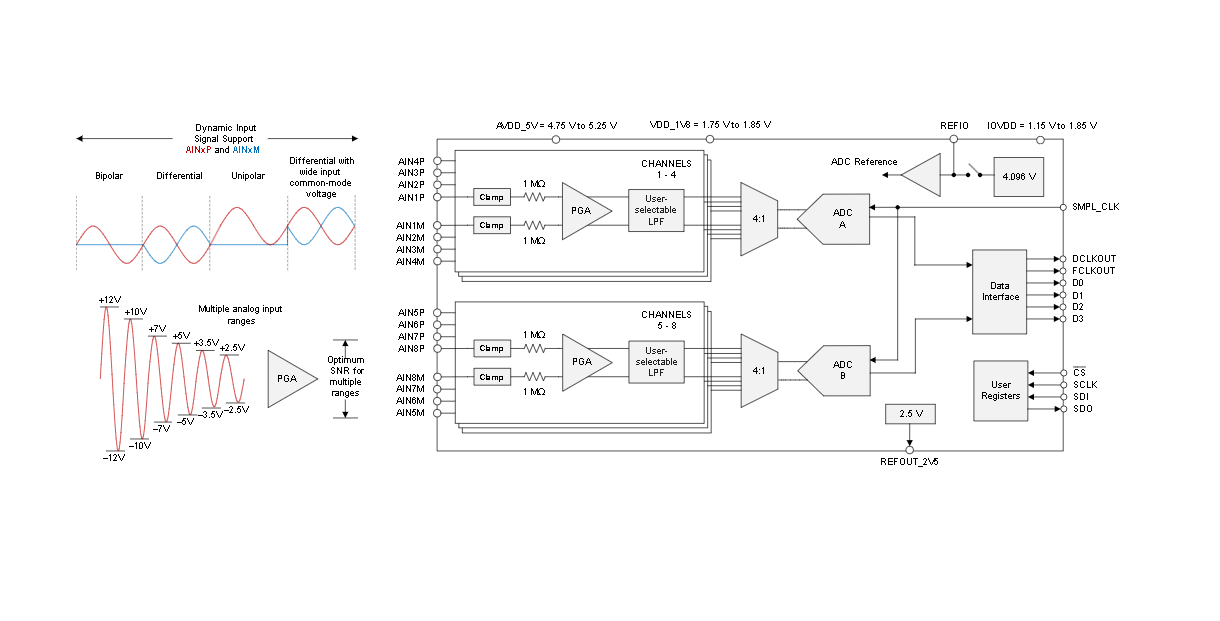

ADS981x是一款8通道数据采集(DAQ)系统,基于双通道、同步采样、18位逐次逼近寄存器(SAR)模数转换器(ADC)。ADS981x为每个通道提供完整的模拟前端,具有输入箝位保护电路、1MΩ输入阻抗和具有用户可选带宽选项的可编程增益放大器(PGA)。高输入阻抗允许直接与传感器和变压器连接,从而消除了对外部驱动电路的需求。ADS981x可配置为接受共模电压高达±12V的单极性或双极性输入。

*附件:ads9817.pdf

该器件还具有用于ADC的4.096V基准电压源和用于外部电路的2.5V基准电压源输出。支持1.2V至1.8V工作的数字接口使ADS981x无需外部电压电平转换器即可使用。

特性

- 8通道、18位ADC,带模拟前端:

- 双通道、同步采样:4 × 1 通道

- 恒定的 1MΩ 输入阻抗前端

- 可编程模拟输入范围:

- ±12V、±10V、±7V、±5V、±3.5V和±2.5V

- 单端和差分输入

- ±12V 共模电压范围

- 输入过压保护:高达 ±18V

- 用户可选择的模拟输入带宽:

- 21kHz 和 400kHz

- 集成低漂移精密基准电压源

- ADC基准电压源:4.096V

- 2.5V 基准输出,用于外部电路

- 全通量下的出色交流和直流性能:

- DNL:±0.5LSB,INL:±0.8LSB

- 信噪比:92dB,总谐波扰:–113dB

- 电源:

- 模拟和数字:5V 和 1.8V

- 数字接口:1.2V 至 1.8V

- 温度范围:–40°C 至 +125°C

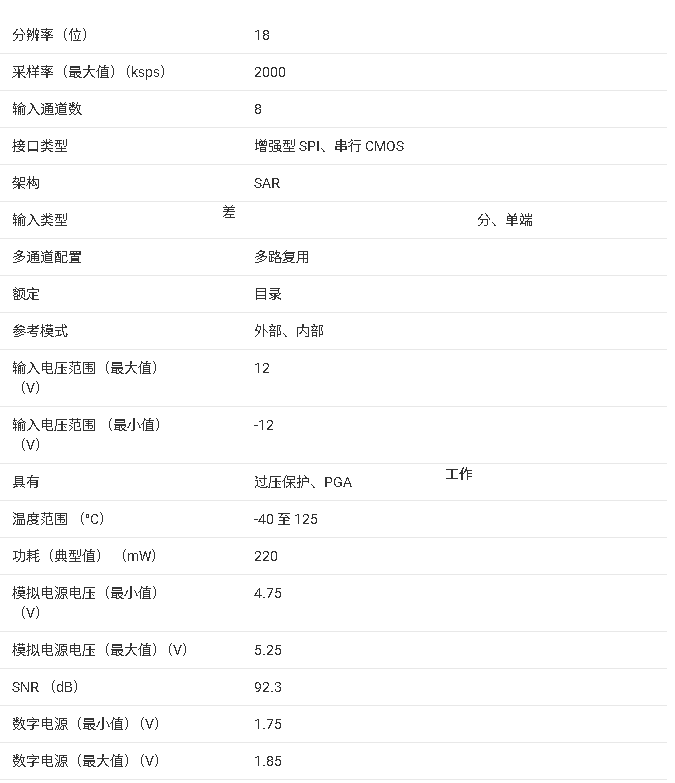

参数

方框图

一、产品概述

ADS9815 与 ADS9817 是德州仪器推出的 18 位双路同步采样 ADC ,核心优势在于集成完整模拟前端(含输入钳位、可编程增益放大器 PGA、低通滤波器),支持 8 通道模拟输入,适配参数测量单元(PMU)、电池化成测试设备、数据采集(DAQ)等高精度工业场景。器件采用 56 引脚 VQFN(RSH 封装,7mm×7mm),支持 - 40~125°C 宽温工作,通过双路 SAR ADC 实现同步采样,ADS9815 最高采样率 1MSPS / 通道,ADS9817 最高 2MSPS / 通道,兼顾高精度与高吞吐量需求。

二、核心特性

(一)多通道高精度采样

- 模拟输入与前端

- 通道配置 :8 路差分 / 单端输入,支持 ±2.5V/±3.5V/±5V/±7V/±10V/±12V 可编程输入范围,±12V 共模电压范围,输入阻抗恒定 1MΩ(不受采样频率、输入范围影响),可直接连接传感器或变压器,无需外部驱动电路;

- 输入保护 :集成钳位电路,支持 ±18V 过压保护,输入电流限制≤10mA,搭配串联电阻可进一步抑制浪涌电流;

- 带宽选择 :每通道配备可编程低通滤波器(LPF),低带宽模式(21kHz)优化噪声性能,高带宽模式(182kHz~400kHz,随输入范围变化)适配高速信号采样,例如 ±7V 范围下带宽 400kHz,±2.5V 范围下 182kHz。

- ADC 性能指标

- 静态精度 :微分非线性(DNL)±0.5LSB,积分非线性(INL)±0.8LSB(-40~125°C),零漂 ±1.5ppm/°C,增益漂移 ±3ppm/°C,总未调整误差(TUE)校准后仅 0.0016%(25°C±5°C),确保高精度测量;

- 动态性能 :信噪比(SNR)最高 92dBFS(低带宽模式,±12V 范围),总谐波失真(THD)-113dB,无杂散动态范围(SFDR)113dB,支持微弱信号精准采集;

- 同步采样 :双路 ADC 同步工作,通道间相位差 < 1ns,适配多通道相位敏感测量(如功率分析、振动监测)。

(二)灵活供电与低功耗

- 供电配置 :三路独立电源 —— 模拟 5V(AVDD_5V:4.75

5.25V)、数字 1.8V(VDD_1V8:1.751.85V)、数字接口 1.2~1.8V(IOVDD),无供电时序要求,简化系统设计; - 功耗优化 :ADS9815 最大功耗 165mW(1MSPS / 通道),ADS9817 最大 232mW(2MSPS / 通道);掉电模式下电流≤2mA(AVDD_5V)、≤8mA(VDD_1V8),适配电池供电的便携式设备。

(三)智能功能与可靠性

- 参考与校准

- 内置基准 :集成 4.096V 低漂移基准(温度系数 ±25ppm/°C),REFIO 引脚可配置为基准输出 / 外部基准输入,REFOUT_2V5 引脚提供 2.5V 基准供外部电路使用;

- 增益校准 :支持全局 / 通道级增益误差校准(GE_CAL_EN1~EN4 寄存器),校准后增益误差≤±0.05% FSR,消除系统误差;

- 数据格式 :输出支持二进制补码 / 原码,18 位转换结果以 24 位数据包输出(低 6 位补 0),适配不同处理器接口。

- 故障防护与测试

- 数据随机化 :可选 XOR 操作对输出数据随机化,减少地弹噪声对模拟性能的干扰;

- 测试模式 :支持固定图案、数字斜坡、交替图案等测试模式,可替换 ADC 输出数据,用于接口调试与链路验证;

- 同步功能 :SMPL_SYNC 引脚支持多器件同步,确保多 ADC 采样时钟与数据帧对齐,适配多通道扩展场景。

三、器件信息与电气规格

(一)型号差异与封装

| 型号 | 采样率 | 最大功耗 | 订购型号 | 包装规格 |

|---|---|---|---|---|

| ADS9815 | 1MSPS / 通道 | 165mW | ADS9815RSHR/ADS9815RSHR.A | 2500 片 / 大卷带,MSL Level-3(260°C,168 小时吸湿) |

| ADS9817 | 2MSPS / 通道 | 232mW | ADS9817RSHR/ADS9817RSHR.A/ADS9817RSHT | 2500 片 / 大卷带(RSHR)、250 片 / 小卷带(RSHT),MSL Level-3 |

(二)热学特性(56 引脚 VQFN)

| 热参数 | 值 | 单位 |

|---|---|---|

| 结到环境热阻(RθJA) | 23.2 | °C/W |

| 结到顶部外壳热阻(RθJC (top)) | 10.5 | °C/W |

| 结到板热阻(RθJB) | 6.1 | °C/W |

| 结到顶部特征参数(ΨJT) | 0.1 | °C/W |

| 结到板特征参数(ΨJB) | 6.0 | °C/W |

(三)核心电气参数(TA=-40~125°C,AVDD_5V=5V)

| 参数 | ADS9815 | ADS9817 | 测试条件 |

|---|---|---|---|

| 采样率 | 1MSPS / 通道 | 2MSPS / 通道 | 最大吞吐量 |

| SNR(低带宽) | 91dBFS | 92dBFS | ±12V 范围,fIN=2kHz |

| THD | ≤-113dB | ≤-113dB | 全输入范围,fIN=2kHz |

| 输入电容 | 10pF | 10pF | 所有输入范围 |

| AVDD_5V 电流 | 25mA(典型) | 26mA(典型) | 最大吞吐量,内置基准 |

| 掉电电流(AVDD_5V) | 2mA(最大) | 2mA(最大) | PD_CHIP=1 |

四、功能模块详解

(一)模拟前端与信号调理

- 可编程增益与滤波

- PGA 增益 :通过 RANGE_CHx 寄存器配置输入范围,增益随范围自动匹配,例如 ±5V 范围对应增益 0.8192(基于 4.096V 基准),±12V 范围对应增益 0.3413;

- 滤波特性 :低带宽模式(21kHz)适用于低频小信号(如传感器输出),高带宽模式适配高速信号(如电机振动、快速电压瞬变),例如 ±10V 范围下高带宽 385kHz,阶跃信号 settling 时间 13μs(99.99% FS)。

- 共模抑制与校准

- 共模配置 :通过 CM_CTRL_EN、CM_EN_CHx 寄存器启用宽共模抑制,支持 ±RANGE/2、±6V、±12V 共模范围,例如 ±5V 输入范围可配置 ±2.5V 共模,±12V 范围支持 ±12V 共模;

- 增益校准 :启用 GE_CAL_EN1~EN4 后,输入范围精度提升,未校准前范围扩大 1.024 倍(如 ±5V 变为 ±5.12V),校准后恢复标称范围,误差≤±0.05% FSR。

(二)ADC 采样与数据接口

- 采样时钟与同步

- 时钟输入 :支持单端(SMPL_CLKP 输入,SMPL_CLKM 接地)或差分(SMPL_CLKP/SMPL_CLKM 差分输入)时钟,ADS9815 时钟频率 3.9

4.1MHz,ADS9817 3.98.1MHz,时钟占空比 45%~55%,建议使用低抖动时钟(≤100fs)以优化 SNR; - 同步控制 :SMPL_SYNC 引脚用于多器件同步,上电或复位后需触发一次同步,确保所有 ADC 采样通道与帧时钟(FCLKOUT)对齐,避免通道间相位偏差。

- 时钟输入 :支持单端(SMPL_CLKP 输入,SMPL_CLKM 接地)或差分(SMPL_CLKP/SMPL_CLKM 差分输入)时钟,ADS9815 时钟频率 3.9

- 数据输出接口

- 模式配置 :支持 2 通道 / 4 通道数据 lanes,单数据率(SDR)/ 双数据率(DDR)模式,例如 4 通道 DDR 模式下,ADS9817 数据时钟 48MHz,2 通道 DDR 模式下 96MHz;

- 信号定义 :D0~D3 为数据输出,DCLKOUT 为数据时钟(源同步),FCLKOUT 为帧时钟(每 8 通道数据一个帧脉冲),数据输出 MSB 优先,18 位结果封装为 24 位(低 6 位补 0);

- 菊花链支持 :通过 DAISY_CHAIN_LEN 寄存器配置多器件菊花链,最多支持 32 个 ADC 级联,简化多通道系统布线。

(三)参考与电源管理

- 基准电路

- 内置基准 :默认启用 4.096V 基准,REFIO 引脚需并联 10μF 陶瓷电容滤波,温度系数 ±25ppm/°C,初始精度 ±0.1%;

- 外部基准 :PD_REF=1 时禁用内置基准,REFIO 引脚接入 4.092~4.100V 外部基准(如 REF7040),需确保基准噪声≤10μVrms,避免影响 ADC 精度。

- 电源与去耦

- 供电要求 :AVDD_5V、VDD_1V8、IOVDD 需独立供电,AVDD_5V 与 VDD_1V8 建议使用线性稳压器,IOVDD 可与 FPGA/MCU 接口电压兼容(1.2~1.8V);

- 去耦设计 :每个电源引脚需靠近器件放置 0.1μF 陶瓷电容 + 1μF 钽电容,REFIO 与 REFM 之间并联 10μF 电容,AGND 与 PGND 单点连接,减少地弹噪声。

五、典型应用场景

(一)参数测量单元(PMU)

- 应用架构 :ADS9817 作为核心采样器件,8 路输入分别连接 PMU 输出,通过 PGA 适配 PMU 的电压(0~12V)与电流(通过分流电阻转换为电压)信号,低带宽模式(21kHz)用于静态参数测量(如直流电压 / 电流),高带宽模式(400kHz)用于动态响应测试(如瞬态电压变化);

- 关键配置 :输入范围配置为 ±12V(覆盖 PMU 输出范围),启用增益校准(GE_CAL_EN1=3),数据接口采用 4 通道 DDR 模式,FCLKOUT 与 FPGA 同步,确保多通道测量时序一致性;

- 可靠性设计 :输入串联 1kΩ 电阻限制过流,REFIO 使用内置基准并并联 10μF 电容,AVDD_5V 采用 5V/2A 线性稳压器,减少电源噪声对采样精度的影响。

(二)电池化成测试设备

- 应用架构 :ADS9815 用于电池单体电压采样(8 通道对应 8 节电池),输入范围 ±3.5V(适配 3.7V 锂电池),通过差分输入抑制共模噪声(如地线干扰),低带宽模式(21kHz)过滤开关电源噪声;

- 关键配置 :共模范围配置为 ±6V(CM_RNG_CHx=1),启用 XOR 数据随机化(XOR_EN=1),减少地弹噪声,采样率 1MSPS / 通道,满足电池化成过程中 100ms 间隔的电压监测需求;

- 校准策略 :每批次设备出厂前进行两点校准(零刻度 / 满刻度),通过 OFFSET 与 GAIN 寄存器补偿系统误差,确保长期测量精度≤0.1%。

六、设计指南

(一)PCB 布局与防护

- 布局要点

- 分区设计 :模拟部分(AINxP/AINxM、REFIO、REFM)与数字部分(D0~D3、DCLKOUT、FCLKOUT)分开布局,模拟地与数字地单点连接,避免数字噪声耦合;

- 走线要求 :模拟输入走线长度≤50mm,宽度≥0.2mm,差分对走线长度差≤1mm,阻抗匹配 1MΩ(串联电阻可选);数字走线采用 50Ω 阻抗控制,远离模拟区域;

- 热管理 :暴露热焊盘(Thermal pad)需连接≥20mm² 铜皮,打 4 个 0.3mm 过孔(间距 1mm)至内层地平面,ADS9817 满负荷工作时结温≤100°C(环境温度 50°C)。

- ESD 与 EMC 防护

- ESD 防护 :器件 HBM ESD±2000V,CDM±500V,调试时需佩戴防静电手环,PCB 预留 TVS 管位置(如 SMBJ18CA)用于输入过压保护;

- EMC 优化 :电源端串联共模电感(10μH),模拟输入并联 0.1μF 滤波电容,数字接口使用屏蔽线,满足 EN 61326-1 工业 EMC 标准。

(二)初始化与配置流程

- 上电初始化

- 配置寄存器组 0(REG_BANK_SEL=0),设置 INIT_1=1011b(地址 0x04);

- 切换至寄存器组 1(REG_BANK_SEL=2),设置 INIT_2=1(地址 0xF6);

- 切换至寄存器组 2(REG_BANK_SEL=16),设置 INIT_3=1、INIT_4=1、INIT_5=1(地址 0x12、0x13、0x0A),等待 10μs 后复位 INIT_5;

- 依次复位 INIT_2、INIT_4、INIT_3、INIT_1,写入 INIT_KEY=11b(地址 0x33),启动 INIT=1(地址 0xF4),等待 1ms 后复位 INIT,完成初始化。

- 核心配置

- 输入范围 :通过 RANGE_CH1~CH8 寄存器(地址 0xC2、0xC3)配置每通道输入范围,例如 CH1 配置为 ±5V(RANGE_CH1=0);

- 带宽选择 :ANA_BW 寄存器(地址 0xC0)设置每通道带宽,例如 CH1~CH4 设为高带宽(ANA_BW [3:0]=1111);

- 数据接口 :DATA_LANES=0(4 通道)、DATA_RATE=0(DDR)(地址 0xC1),FCLKOUT 与 FPGA 时钟同步。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

ADS1115-Q1 汽车级模数转换器技术文档总结2025-11-18 850

-

ADS1262/ADS1263 32 位高精度 ADC 技术文档总结2025-11-11 2574

-

ADS7056 技术文档核心总结2025-11-07 707

-

ADS7067 技术文档总结2025-10-30 1020

-

ADS131B23 技术文档总结2025-10-29 863

-

ADS1288 技术文档总结2025-10-27 852

-

ADS9212 技术文档总结2025-10-24 715

-

德州仪器ADS9813/ADS9817评估模块技术解析与应用指南2025-08-14 1987

-

ADS9817评估模块2024-11-05 482

-

PS9817A-1,-2数据表2023-07-03 393

-

PS9817A-1,-2 数据表2023-01-13 431

-

BLE技术总结文档2015-10-29 820

全部0条评论

快来发表一下你的评论吧 !