DAC39RF10技术文档总结

描述

DAC39RF10 和 'RFS10 是具有 16 位分辨率的双通道和单通道数模转换器 (DAC) 系列。这些器件可用作非插值或插值DAC,用于直接RF采样或复杂基带信号生成。单通道的最大输入数据速率为20.48GSPS,两个通道的最大输入数据速率为10.24GSPS。这些器件可以在超过 8GHz 的载波频率下生成高达 10、7.5 和 5GHz 信号带宽(8、12 和 16 位输入分辨率)的信号,从而能够通过 C 波段直接采样并进入 X 波段。

*附件:dac39rf10.pdf

高采样率、输出频率范围、64 位 NCO 频率分辨率和任何具有相位相干性的跳频也使该器件能够进行任意波形生成 (AWG) 和直接数字合成 (DDS)。

JESD204B和JESD204C兼容的串行接口具有 16 个接收器对,速度高达 12.8Gbps。该接口JESD204B,JESD204C符合子类 1 标准,可通过使用 SYSREF 实现确定性延迟和多设备同步。

特性

- 16位、10.24/20.48GSPS、多奈奎斯特DAC内核

- 最大输入数据速率:

- 8 位,单通道,DES 模式:20.48GSPS

- 12 位,单通道,DES 模式:15.5GSPS

- 16 位,单通道:10.24GSPS

- 8 位,双通道,10.24GSPS

- 12 位,双通道:7.75GSPS/通道

- 16 位,双通道:6.2GSPS/通道

- 输出带宽 (-3dB):12GHz

- fOUT = 2.997GHz、DES2XL模式、DEM/抖动关闭时的性能

- 本底噪声(小信号):–155dBFS/Hz

- SFDR (-0.1 dBFS):60dBc

- IMD3(每音-7 dBFS):–62dBc

- 加相位噪声,10kHz 偏移:-138dBc/Hz

- 四个集成数字上变频器 (DUC)

- 插值:1x、2x、3x、4x、6x、8x ...256 倍

- 用于 I/Q 输出的复杂基带 DUC

- 用于双通道直接射频采样的复杂到实际上变频

- 64 位频率分辨率 NCO

- 快速重新配置接口,实现快速跳频

- 4位数据,200MHz时钟

- 60ns 重新配置(32 位频率)

- 任何具有相位相干性的跳频

- JESD204C界面

- 多达 16 个通道,最高可达 12.8Gbps

- C-S类,子类-1兼容

- 内部交流耦合电容器

- 用于自动 SYSREF 时序校准的 SYSREF 窗口

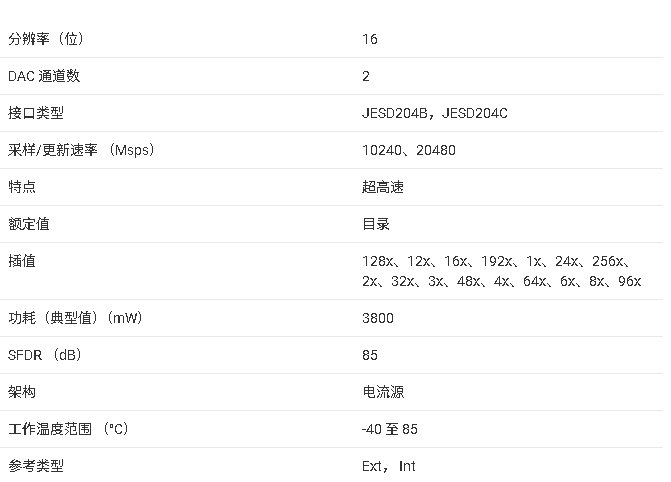

参数

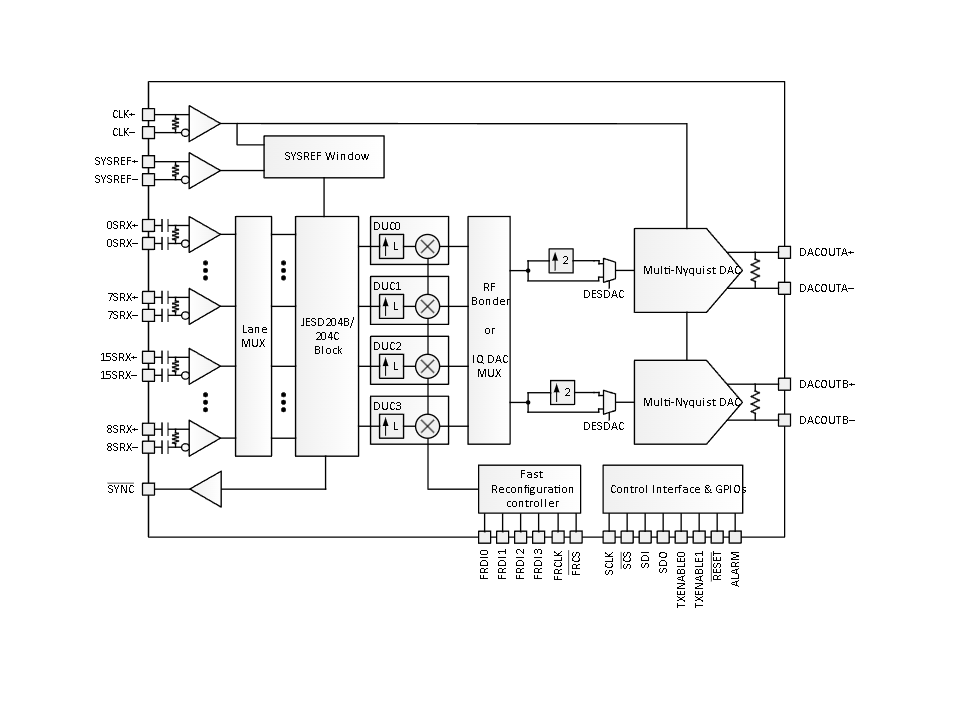

方框图

一、产品概述

DAC39RF10 与 DAC39RFS10 是德州仪器推出的16 位高采样率数模转换器(DAC) ,核心定位为多奈奎斯特频段信号生成,适配卫星通信(SATCOM)、相控阵天线、合成孔径雷达(SAR)激励器、无线通信测试仪及任意波形发生器(AWG)等高端射频场景。两款器件均采用 256 引脚 FCBGA 封装(17mm×17mm,1mm 间距),支持 - 40~85°C 工作温度,核心差异在于通道数量:DAC39RF10 为双通道设计,DAC39RFS10 为单通道设计,均具备高带宽、低噪声、相位相干跳频等关键特性,可直接生成 C 波段至 X 波段的射频信号。

二、核心特性

(一)高采样率与宽频带输出

- 采样率与分辨率适配支持动态调整输入分辨率与采样率,平衡带宽与性能需求,具体参数如下:

- 8 位分辨率:单通道 DES 模式下最高 20.48GSPS,双通道 10.24GSPS / 通道;

- 12 位分辨率:单通道 DES 模式下最高 15.5GSPS,双通道 7.75GSPS / 通道;

- 16 位分辨率:单通道最高 10.24GSPS,双通道 6.2GSPS / 通道;

- 模拟输出带宽(-3dB):12GHz,可在载波频率超 8GHz 时生成最高 10GHz(8 位)、7.5GHz(12 位)、5GHz(16 位)带宽的信号。

- 卓越动态性能在输出频率 2.997GHz、DES2XL 模式、DEM/Dither 关闭条件下,关键指标如下:

- 噪声基底(小信号):-155dBFS/Hz;

- 无杂散动态范围(SFDR,-0.1dBFS 输入):60dBc;

- 三阶互调失真(IMD3,-7dBFS 双音输入):-62dBc;

- 附加相位噪声(10kHz 偏移):-138dBc/Hz。

(二)灵活的数字信号处理能力

- 集成数字上变频器(DUC) 内置 4 个独立 DUC,支持 1×、2×、3×、4×…256× 插值,可实现:

- 复基带信号 I/Q 输出,适配正交调制场景;

- 复信号转实信号上变频,支持双通道直接射频采样;

- 每通道配备 64 位频率分辨率 NCO(数控振荡器),频率精度达 Hz 级,支持相位相干跳频。

- 快速重配置与跳频提供 4 位数据 + 200MHz 时钟的快速重配置接口,32 位频率配置仅需 60ns,支持任意频率跳频且保持相位连续性,满足雷达、通信系统的动态频率切换需求。

(三)高速 JESD204C 接口

- 接口规格 :支持最多 16 条 SerDes lanes,单 lane 最高速率 12.8Gbps,兼容 8b/10b 与 64b/66b 编码;

- 同步特性 :符合 JESD204C Class C-S、Subclass-1 标准,支持确定性延迟与多器件同步,内置 SYSREF 窗口校准功能,自动优化 SYSREF 采样时序;

- 抗干扰设计 :集成片内 AC 耦合电容与 100Ω 差分终端,减少外部电路复杂度,提升信号完整性。

三、器件信息与电气规格

(一)型号差异与扩展系列

| 型号 | 通道数 | 最高采样率(单 / 双沿) | 抗辐射特性 | JESD 接口 |

|---|---|---|---|---|

| DAC39RF10 | 2 | 10.24/20.48 GSPS | 无 | 支持 |

| DAC39RFS10 | 1 | 10.24/20.48 GSPS | 无 | 支持 |

| DAC39RF12 | 2 | 12/24 GSPS | 无 | 支持(仅 2 lane) |

| DAC39RFS12 | 1 | 12/24 GSPS | 无 | 支持(仅 2 lane) |

| DAC39RF10-SP | 2 | 10.4/20.8 GSPS | 120MeV SEL/SEFI,300krad TID | 支持 |

| DAC39RFS10-SP | 1 | 10.4/20.8 GSPS | 120MeV SEL/SEFI,300krad TID | 支持 |

(二)核心电气参数(TA=25°C,VDD 标称值)

| 参数 | 条件 | DAC39RF10(双通道) | DAC39RFS10(单通道) | 单位 |

|---|---|---|---|---|

| 微分非线性(DNL) | 全温度范围 | ±2.2 | ±2.2 | LSB |

| 积分非线性(INL) | 全温度范围 | ±9 | ±9 | LSB |

| 满量程输出电流(IFS_SWITCH) | RBIAS=3.6kΩ,CUR_2X_EN=1 | 20.5(典型) | 20.5(典型) | mA |

| 静态输出电流(ISTATIC) | RBIAS=3.6kΩ | 4.8(典型) | 4.8(典型) | mA |

| 输出电容(COUT) | 单端对地 | 0.25 | 0.25 | pF |

| JESD lane 速率 | 8b/10b 编码 | 0.78125~12.8 | 0.78125~12.8 | Gbps |

| 总功耗(PDIS) | 10.24GSPS,NRZ 模式 | 3747(典型) | 2848(典型) | mW |

(三)热学特性(256 引脚 FCBGA)

| 热参数 | 值 | 单位 |

|---|---|---|

| 结到环境热阻(RθJA) | 15.8 | °C/W |

| 结到顶部外壳热阻(RθJC (top)) | 0.9 | °C/W |

| 结到板热阻(RθJB) | 4.2 | °C/W |

| 结到顶部特征参数(ΨJT) | 0.4 | °C/W |

| 结到板特征参数(ΨJB) | 4.2 | °C/W |

四、功能模块详解

(一)DAC 核心与输出模式

多奈奎斯特输出模式支持 4 种输出模式,适配不同频段与应用场景,核心特性如下表:

模式 是否通直流 最优频率范围 峰值输出功率 备注 非归零(NRZ) 是 0~FCLK/2 0dBFS 标准零阶保持模式,适用于 1st 奈奎斯特区 归零(RTZ) 是 0~FCLK -6dBFS 采样周期后半段归零,改善 2nd 奈奎斯特区性能 射频(RF) 否 FCLK/2~FCLK -2.8dBFS 样本中途反转,2nd 奈奎斯特区平坦度最优 双沿采样(DES) 是 0~FCLK 0dBFS CLK 升降沿均输出样本,采样率翻倍,存在占空比镜像 电流调整与非线性优化

- 满量程电流(IFS)通过外部 RBIAS 电阻与 COARSE_CUR/FINE_CUR 寄存器调节,支持 2 倍电流使能(CUR_2X_EN),最大可至 41mA;

- 集成动态元件匹配(DEM)与数字抖动(Dither)功能:DEM 通过随机化电流源切换改善非线性,Dither 添加 8 种数字码抵消高次谐波,二者可根据频率动态使能(750MHz 以下 DEM_ADJ=1,以上 DEM_ADJ=0)。

(二)数字上变频(DUC)与 NCO

- DUC 功能每通道 DUC 支持多速率插值与复信号混频,具体特性:

- 插值范围:2×~256×,支持多级滤波(如 2× 用 fir1、4× 用 fir1+fir2),通带纹波 <0.01dB,阻带衰减> 90dB;

- 信号合成:4 个 DUC 输出可通过通道绑定器(Channel Bonder)缩放(1×、0.5×、0.25×)后求和,避免饱和,支持实信号或复信号输出。

- NCO 特性

- 频率分辨率:64 位,支持相位连续 / 相干 / 同步三种更新模式,满足跳频系统相位一致性需求;

- 同步触发:可通过 JESD204C 数据 LSB、SYSREF 或 SPI 寄存器触发 NCO 同步, latency 可通过 Excel 工具计算,确保多器件协同。

(三)JESD204C 接口与同步

- 接口配置

- 编码支持:8b/10b(兼容 JESD204B)与 64b/66b(强制加扰),后者提升带宽效率;

- lane 映射:16 条物理 lane 可通过交叉开关(Crossbar)灵活映射到逻辑 lane,简化 PCB 布线;

- 多器件同步:Subclass-1 模式下通过 SYSREF 校准 LMFC(多帧时钟),弹性缓冲区(EB)释放点可通过 RBD 参数调节,确保确定性延迟。

- 关键时序

- SYSREF 周期需为 CLK 周期的 16 倍以上,且与 LMFC 周期匹配;

- SerDes lane 速率与 CLK 频率满足 F_BIT = R×F_CLK(R 为比例系数,如 1.25、2.5 等),需通过 REFDIV/MPY/RATE 寄存器配置 PLL,确保 VCO 频率在 1.5625~3.2GHz 范围内。

(四)电源与功耗管理

- 供电配置 :需多组独立电源,包括模拟 1.8V(VDDA18A/B)、负模拟 1.8V(VEEAM18/BM18)、数字 1.0V(VDDDIG/VDDE/A/B)、时钟 1.0V(VDDCLK10)等,各组电源需单独去耦(0.1μF 陶瓷电容 + 1μF 钽电容);

- 功耗优化 :支持 14 种功耗模式,例如睡眠模式(MODE [1:0]=11b)功耗仅 165mW,双通道 10.24GSPS NRZ 模式功耗约 3747mW,单通道可低至 2577mW。

-

DAC38RF80 系列技术文档核心总结2025-11-07 891

-

DAC53001技术文档总结2025-10-29 878

-

DAC39RFx10 系列产品技术文档总结2025-10-27 1011

-

DDS39RF10产品技术文档总结2025-10-24 1323

-

DAC39RF20核心信息总结2025-10-22 1587

-

请问DAC39RF10B的新版说明书里面INL的单位Codes是怎么定义的?2024-11-14 386

-

DAC39RF12、DAC39RFS12双通道和单通道数模转换器(DAC)数据表2024-07-15 729

-

DAC39RF10、DAC39RFS10 10.24、20.48GSPS 16位双通道和单通道多奈奎斯特数模转换器(DAC)数据表2024-07-12 717

全部0条评论

快来发表一下你的评论吧 !