DAC63202W 智能数模转换器(DAC)技术总结

描述

该DAC63202W是一款 12 位、双通道、缓冲、电压输出和电流输出智能数模转换器 (DAC)。DAC63202W器件支持Hi-Z掉电模式和断电条件下的Hi-Z输出。DAC输出提供力检测选项,用作可编程比较器和电流吸收器。多功能 GPIO、功能生成和可编程非易失性存储器 (NVM) 使这些智能 DAC 能够实现无处理器应用和设计重用。该器件可自动检测I2C、SPI和PMBus接口,并包含内部基准电压源。

该智能DAC的功能集与微型封装和低功耗相结合,是电压裕量和缩放、用于偏置和校准的直流设定点以及波形生成等应用的绝佳选择。

*附件:dac63202w.pdf

特性

- 具有灵活配置的可编程电压或电流输出:

- 电压输出:

- 1LSB DNL

- 收益为 1 ×、1.5 ×、2 ×、3 ×和 4 ×

- 电流输出:

- 1LSB INL 和 DNL(8 位)

- ±25μA、±50μA、±125μA、±250μA输出范围选项

- 电压输出:

- 适用于所有通道的可编程比较器模式

- VDD关闭时的高阻抗输出

- 高阻抗和电阻下拉掉电模式

- 50MHz SPI 兼容接口

- 自动检测 I2C、SPI 或 PMBus™ 接口

- 1.62V VIH,VDD = 5.5V

- 通用输入/输出 (GPIO) 可配置为多种功能

- 预定义波形生成:正弦波、余弦波、三角波、锯齿波

- 用户可编程非易失性存储器 (NVM)

- 内部、外部或电源作为参考

- 工作范围广:

- 电源:1.8V 至 5.5V

- 温度:–40°C 至 +125°C

- 小包装:

- 16 引脚 DSBGA:1.76mm × 1.76mm,标称值

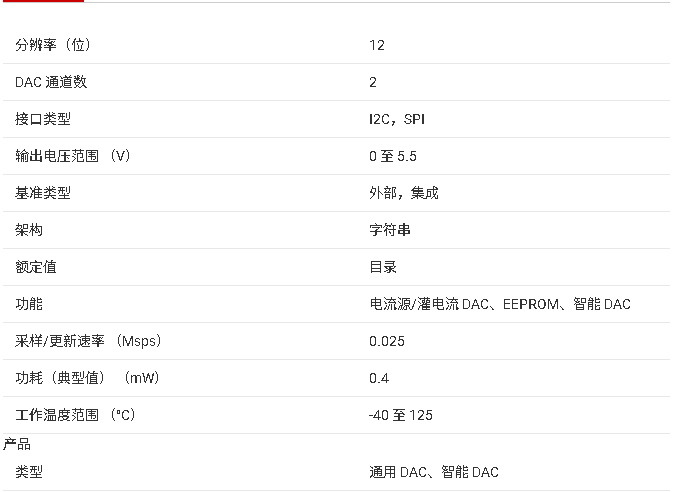

参数

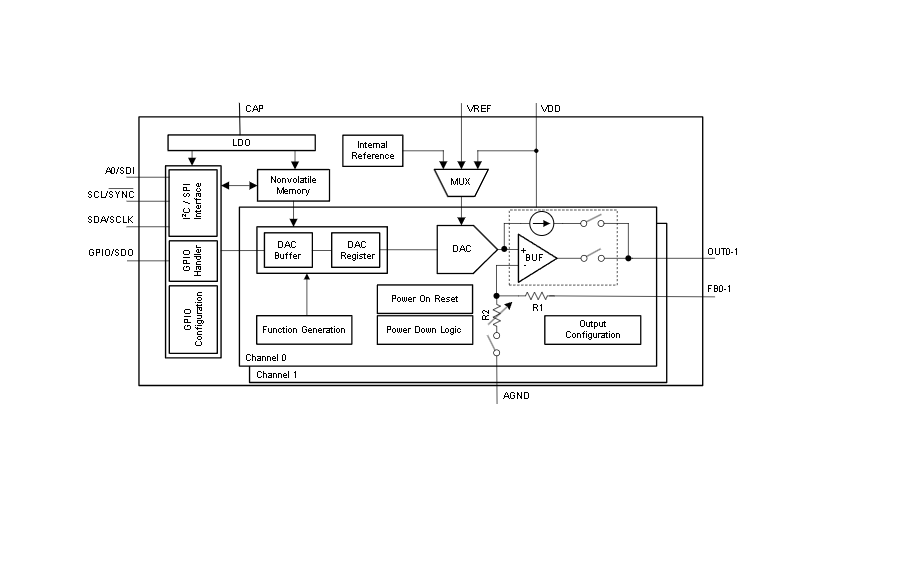

方框图

DAC63202W 是德州仪器(Texas Instruments)推出的 12 位双通道智能数模转换器(DAC),主打电压 / 电流双输出模式、自动协议检测与可编程波形生成功能,适配光模块、高性能计算、笔记本电脑等场景的电源电压调节、信号校准与故障监测需求。其核心优势在于高集成度(内置基准、NVM、比较器)与灵活的功能扩展,结合小尺寸与宽环境适应性,成为精密模拟信号转换的高效解决方案。以下从核心特性、性能参数、功能模块、应用设计及使用信息等方面展开总结。

一、核心特性与产品定位

1. 基础参数与架构

- 分辨率与通道配置 :12 位分辨率双通道 DAC,每通道独立支持电压输出(0-VDD)或电流输出(±25μA/±50μA/±125μA/±250μA 可选),集成 4 路比较器输入(FB0-FB1 复用)与 1 路多功能 GPIO,支持比较器、波形生成等扩展功能。

- 低功耗与宽电压 :工作电压 1.8V-5.5V,电压输出模式静态电流典型值 150μA / 通道,电流输出模式低至 42μA / 通道(±25μA 量程);内部集成低压差稳压器(LDO),CAP 引脚需外接 1.5μF 旁路电容保障稳定性。

- 高集成度 :内置 1.21V 高精度电压基准(温度漂移最大 50ppm/°C)、非易失性存储器(NVM)、可编程比较器与波形生成器,支持参数掉电保存与独立故障管理,减少外部元器件数量。

2. 环境适应性与可靠性

- 工作温度 :-40°C 至 125°C(结温最高 150°C),满足工业级宽温需求,适配恶劣环境下的精密信号转换。

- ESD 防护 :人体放电模型(HBM)±2000V,带电器件模型(CDM)±500V,符合 JEDEC 抗静电标准,降低装配与使用过程中的损坏风险。

- 封装规格 :16 引脚 DSBGA(YBH 封装),尺寸仅 1.76mm×1.76mm,最大高度 0.4mm,底部球栅阵列设计,适配高密度 PCB 布局,尤其适合空间受限的消费电子与工业设备。

二、关键性能指标

1. 电压输出模式性能(典型值,TA=25°C,VDD=5.5V,增益 = 1×)

| 性能参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 积分非线性(INL) | 全量程,代码 32d-4064d | -5 | - | 5 | LSB |

| 微分非线性(DNL) | 全量程,无失码 | -1 | - | 1 | LSB |

| 总未调整误差(TUE) | -40°C 至 125°C,相对于满量程(FSR) | -0.5 | - | 0.5 | %FSR |

| 零码误差 | 外部基准,VDD=5.5V | 6 | - | 12 | mV |

| 输出阻抗(ZO) | 内部基准,增益 = 1.5×/2× | 400 | 500 | 600 | kΩ |

| 建立时间 | 1/4-3/4 量程,settling 至 10% FSR | - | 20 | - | μs |

| 压摆率 | VDD=5.5V | - | 0.3 | - | V/μs |

| 输出噪声(0.1Hz-10Hz) | DAC 中码,内部基准,增益 = 4× | - | 90 | - | μVpp |

2. 电流输出模式性能(典型值,TA=25°C,VDD=5.5V,±250μA 量程)

| 性能参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 积分非线性(INL) | 全量程,代码 0d-255d | -1 | - | 1 | LSB |

| 微分非线性(DNL) | 全量程,无失码 | -1 | - | 1 | LSB |

| 偏移误差 | 各量程通用 | - | ±1 | - | %FSR |

| 增益误差 | 各量程通用 | - | ±1.3 | - | %FSR |

| 输出阻抗(ZO) | DAC 中码,VOUT=VDD/2 | 60 | - | - | MΩ |

| 建立时间 | 1/4-3/4 量程,settling 至 1LSB | - | 60 | - | μs |

| 输出噪声(0.1Hz-10Hz) | DAC 中码 | - | 150 | - | nApp |

三、电源与功耗

1. 电源需求

| 电源类型 | 电压范围(MIN-NOM-MAX) | 典型电流(TA=25°C,VDD=3.3V) | 单位 |

|---|---|---|---|

| VDD(主电源) | 1.8-3.3-5.5V | 150(电压输出)/42(电流输出) | μA / 通道 |

| IOV(数字接口) | 1.71-3.3-5.5V | 6 | μA |

| VREF(基准) | 1.21V(固定,内部) | 10 | μA |

2. 功耗分布

- 正常模式 :电压输出模式总功耗约 0.5mW / 通道(VDD=3.3V),电流输出模式低至 0.14mW / 通道(±25μA 量程)。

- 睡眠模式 :内部基准关闭时功耗 28μA,仅保留必要电路供电,适配设备待机场景。

四、应用设计要点

1. 电源与基准设计

- 供电架构 :VDD 推荐使用线性稳压器(如 TPS7A02)或低噪声 DC/DC(如 TPS62803),避免开关噪声耦合至模拟信号;CAP 引脚需靠近器件放置 1.5μF X7R 陶瓷电容,VDD 引脚旁并联 0.1μF 去耦电容。

- 基准选择 :优先使用内部 1.21V 基准(需设置 EN-INT-REF=1),若需更高精度可外接 1.8V-VDD 范围的外部基准(VREF 引脚),注意外部基准需在 VDD 稳定后上电,避免损坏器件。

2. PCB 布局

- 信号分区 :将模拟信号(OUT0-OUT1、FB0-FB1、VREF)与数字信号(SCL/SYNC、SDA/SCLK、GPIO)分开布线,模拟地(AGND)与数字地单点连接,减少串扰;VREF 引脚旁放置 0.1μF 去耦电容,保障基准稳定性。

- 封装焊接 :DSBGA 封装需采用激光钢网(厚度 0.075mm),焊盘直径 0.2mm,焊接后需检查焊点完整性,避免虚焊导致的基准漂移或通信故障。

3. 初始化与配置

- 模式切换 :通过 COMMON-CONFIG 寄存器配置通道工作模式:

- 电压输出:设置 VOUT-PDN-X=00,IOUT-PDN-X=1,短接 OUTx 与 FBx 构成闭环。

- 电流输出:设置 IOUT-PDN-X=0,VOUT-PDN-X=11(高阻),FBx 引脚悬空。

- 关键寄存器配置 :

- 波形生成:通过 DAC-X-FUNC-CONFIG 配置 FUNC-CONFIG-X(波形类型)、CODE-STEP(步长)与 SLEW-RATE(步长时间)。

- 比较器:设置 DAC-X-VOUT-CMP-CONFIG 的 CMP-X-EN=1,配置输入阻抗(CMP-X-HIZ-IN-DIS)与输出模式(推挽 / 开漏)。

- NVM 保存:配置完成后,设置 COMMON-TRIGGER 的 NVM-PROG=1,将参数写入 NVM,掉电后自动加载。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC3154 双通道、10位、500MSPS数模转换器(DAC)技术手册2025-11-14 946

-

DAC539E4W 智能数模转换器(DAC)技术总结2025-10-28 898

-

DAC63202和DAC53202智能数模转换器(DAC)数据表2024-07-16 590

-

DAC63204.DAC53204.DAC43204数模转换器(DAC)数据表2024-07-15 572

-

DAC3152/DAC3162数模转换器(DAC)数据表2024-06-20 480

-

DAC数模转换器介绍2023-03-22 4788

-

如何使用智能数模转换器生成脉宽调制信号?2022-11-04 711

-

DAC数模转换器的主要特点有哪些2022-01-11 1445

-

介绍DAC数模转换器以及DMA的使用2021-08-12 3688

-

数模转换器是什么2021-07-26 3294

-

如何设计16位高速数模转换器(DAC)?2021-04-06 3832

-

一文看懂理想数模转换器 (DAC) 的重要属性2018-04-20 20693

-

DAC0832仿真程序 数模转换器DAC0832 protues2017-01-14 3130

-

数模转换器的基本原理及DAC类型简介2016-08-16 23641

全部0条评论

快来发表一下你的评论吧 !