AMC131M03 三通道隔离型 ΔΣ ADC 技术总结

描述

该AMC131M03是一款精密、三通道、数据和电源隔离、同步采样、24位、三角积分(ΔΣ)模数转换器(ADC)。该AMC131M03提供宽动态范围、低功耗和电能测量专用功能,专为电能计量和功率计量应用而设计。由于该器件具有高输入阻抗,ADC输入可以直接连接到电阻分压器网络或分流电流传感器。

*附件:amc131m03.pdf

该AMC131M03具有完全集成的隔离式 DC/DC 转换器,允许从器件的低端进行单电源作。增强型电容隔离栅已通过 VDE 0884-17 和 UL1577 认证。该隔离栅将系统中在不同共模电压电平下运行的部件分开,并保护低压部件免受损坏,使该AMC131M03成为使用并联电流传感器的多相电能计量应用的绝佳选择。

特性

- 三个隔离式同步采样ΔΣ ADC,具有差分或单端输入

- 单电源作(3.3 V 或 5 V),集成 DC/DC 转换器

- 低 EMI:符合 CISPR-11 和 CISPR-25 标准

- 可编程数据速率:高达 64 kSPS

- 可编程增益:高达 128

- 低漂移内部基准电压源

- 内部温度传感器

- 具有循环冗余校验 (CRC) 功能的 4 线 SPI 接口

- 安全相关认证:

- 7070V 峰值增强隔离,符合 DIN EN IEC 60747-17 (VDE 0884-17) 标准

- 5000V RMS 隔离 1 分钟,符合 UL1577 标准

- 封装:20引脚宽体SOIC

- 工作温度范围:–40°C 至 +125°C

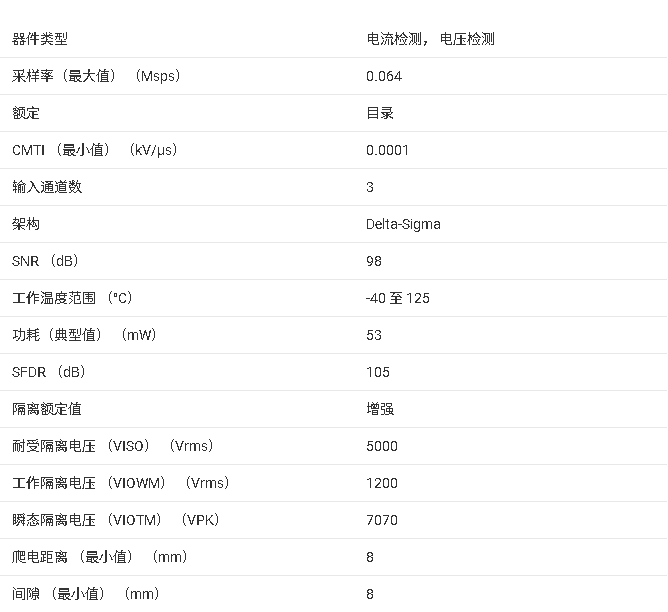

参数

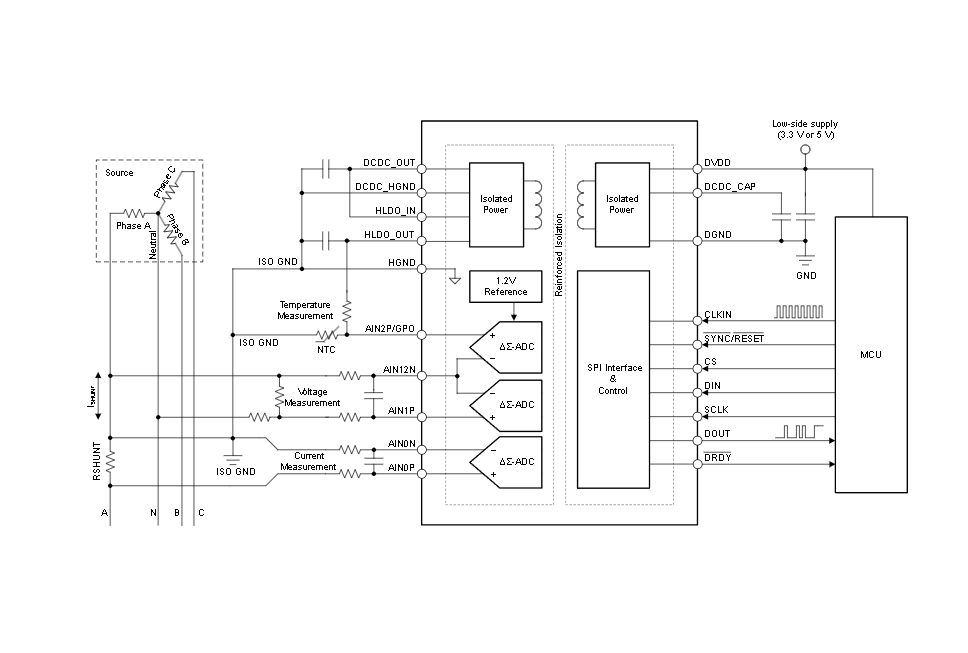

方框图

AMC131M03 是德州仪器(Texas Instruments)推出的 三通道同步采样隔离型 ΔΣ ADC ,集成数据与电源隔离功能、内置 DC/DC 转换器,专为高精度能量计量、电力监测及工业控制场景设计。其核心优势在于强化隔离性能、宽增益范围与低噪声特性,可直接适配分流电阻、电压分压网络等传感器,满足商用 / 民用电表、断路器、EV 充电站及电池管理系统(BMS)的严苛需求。以下从核心特性、性能参数、功能模块、应用设计及订购信息等方面展开总结。

一、核心特性与产品定位

1. 基础参数与架构

- ADC 通道配置 :3 路同步采样 24 位 ΔΣ ADC,支持差分或单端输入;每路通道独立可编程增益(1×-128×),适配 0.05A-100A 电流范围(配合分流电阻)与 100V-240V 电压范围(配合分压电阻)。

- 隔离性能 :采用 SiO₂电容隔离屏障,符合 DIN EN IEC 60747-17(VDE 0884-17)强化隔离标准(7070Vₚₖ峰值隔离电压)、UL1577 标准(5000Vᵣₘₛ隔离电压,持续 1 分钟);隔离屏障电容约 4.5pF,绝缘电阻>10¹²Ω(25℃),抗共模瞬态干扰(CMTI)达 150V/ns,适配高压系统高低侧隔离监测。

- 集成电源方案 :内置隔离型 DC/DC 转换器,支持单电源供电(低压侧 3.3V/5V),高压侧输出 3.0V(DCDC_OUT),经 LDO 后提供 2.6-3.2V(HLDO_OUT),可对外提供 1mA 辅助电流(如为外部滤波器供电),简化多隔离电源设计。

- 环境适应性 :符合 AEC-Q100 Grade 1 温度标准(-40°C 至 125°C 工作温度,结温最高 150°C);ESD 防护达人体放电模型(HBM)±2000V、带电器件模型(CDM)±1000V;电磁辐射(EMI)满足 CISPR-11 与 CISPR-25 标准,减少对系统敏感设备干扰。

2. 封装与物理特性

- 封装规格 :20 引脚宽体 SOIC(DFM 封装),尺寸 12.8mm×10.3mm,引脚间距 1.27mm,适配常规 PCB 布局;底部无热焊盘,需通过 HGND 引脚优化散热。

- 隔离间距 :外部爬电距离与电气间隙均≥8.0mm,内部绝缘距离≥0.021mm,符合污染等级 2、气候类别 40/125/21,适配 600Vₐₙ以下电网系统。

二、关键性能指标

1. ADC 核心性能(典型值,TA=25°C,DVDD=3.3V,fCLKIN=8.192MHz,增益 = 1,OSR=1024)

| 性能参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 分辨率 | 3 路 ADC 通道 | - | 24 | - | Bits |

| 满量程范围(FSR) | 增益 = 1× | - | ±1.2 | - | V |

| 增益 = 128× | - | ±9.375 | - | mV | |

| 输入失调误差(基准) | 通道 0/1,外部短接,TA=25°C | -100 | ±10 | 330 | µV |

| 全局斩波模式开启,通道 0/1 | -100 | 6 | 100 | µV | |

| 失调误差温度系数 | 全局斩波模式开启 | -0.3 | ±0.1 | 0.3 | µV/°C |

| 增益误差 | TA=25°C,端点拟合,通道 0 | -0.2 | ±0.025 | 0.2 | %FSR |

| 增益漂移 | 含内部基准漂移 | - | 8 | 25 | ppm/°C |

| 共模抑制比(CMRR) | DC 条件,共模电压范围内 | - | 110 | - | dB |

| 输入等效噪声(0.1Hz-10Hz) | 增益 = 1×,fDATA=4kSPS | - | 10 | - | µVᵣₘₛ |

| 动态范围(DR) | 增益 = 1× | - | 98 | - | dB |

| 增益 = 32×,通道 0 | - | 80 | - | dB | |

| 总谐波失真(THD) | fIN=50/60Hz,VIN=-0.5dBFS | - | -102 | -94 | dB |

| 通道串扰 | 相邻通道间,fIN=50/60Hz | - | -120 | - | dB |

2. 电源与温度传感器性能

| 性能参数 | 测试条件 | 数值范围 / 典型值 | 单位 | ||

|---|---|---|---|---|---|

| 低压侧电源电流(IDVDD) | 高分辨率模式,所有通道使能 | - | 19.5-24 | mA | |

| 低功耗模式,fCLKIN=4.096MHz | - | 16-21 | mA | ||

| 待机模式,所有通道禁用 | - | 160-210 | µA | ||

| DC/DC 转换器输出电压 | DCDC_OUT 至 HGND,无负载 | - | 3.0 | V | |

| 高压侧 LDO 输出(HLDO_OUT) | 无负载,任意通道使能 | 2.6 | 2.9 | 3.2 | V |

| 内部温度传感器 | TA=25°C 输出电压,增益 = 8× | - | 80.5 | - | mV |

| 温度系数(TS_TC) | - | 265 | - | µV/°C | |

| 测量误差(未校准) | - | ±3 | ±5 | °C |

三、核心功能模块

1. ADC 信号链与采样机制

(1)ΔΣ 调制器与数字滤波器

- 调制器架构 :采用二阶 ΔΣ 调制器,调制频率(fMOD)由外部时钟(CLKIN)经可编程分频器(N_DIV=2/4/8/12)得到,默认 fMOD=fCLKIN/2(如 fCLKIN=8.192MHz 时,fMOD=4.096MHz);通过过采样(OSR)降低量化噪声,OSR 可编程范围 64-16384(Turbo 模式下 OSR=64),数据率范围 125SPS-64kSPS。

- 数字滤波器 :

- 主滤波器:sinc³ 低通滤波器,对 OSR≤1024 时直接输出,OSR>1024 时级联 sinc¹ 滤波器,确保带内噪声抑制;滤波器建立时间随 OSR 增加延长(OSR=1024 时约 3120 个 CLK 周期),需忽略未稳定数据。

- 快速建立滤波器:上电或复位后优先启用 sinc¹ 滤波器,2 个转换周期后切换至 sinc³ 滤波器,缩短启动阶段数据稳定时间,适配快速唤醒场景。

(2)可编程增益与输入配置

- 增益控制 :每路通道独立配置 PGA 增益(1×/2×/4×/8×/16×/32×/64×/128×),通过 GAIN 寄存器的 PGAGAINx [2:0] 位设置;增益>4× 时自动启用输入预充电缓冲器,提升输入阻抗(增益 = 8× 时输入阻抗约 0.5MΩ),减少外部信号源负载影响。

- 输入模式 :支持差分、单端、伪差分测量;内置负电荷泵,允许输入电压低于 HGND 1.3V,适配分流电阻电流双向测量(如电池充放电监测);输入多路复用器(MUXn [1:0])可选择外部信号、HGND(偏移校准)或内部测试信号(DC/AC 诊断)。

(3)全局斩波与校准

- 全局斩波模式 :开启后(GC_EN=1b)通过两次极性相反的采样平均,降低器件固有偏移误差与温度漂移(偏移误差降至 ±6µV,漂移 ±0.1µV/°C),适合高精度直流测量场景;数据率约为正常模式的 1/3,需平衡精度与速度。

- 校准机制 :

- 偏移校准:每路通道 24 位偏移校准寄存器(OCALn [23:0]),支持用户写入实测零输入偏移值,自动减法修正。

- 增益校准:每路通道 24 位增益校准寄存器(GCALn [23:0]),支持 0-2 倍增益修正(默认值 8000h 对应增益 1×),补偿系统增益误差。

- 相位校准:10 位相位延迟寄存器(PHASEn [9:0]),可调整通道间采样相位(-OSR/2 至 OSR/2-1 个调制周期),补偿传感器相位差(如电流互感器与电压分压网络的相位偏差)。

2. 隔离与电源管理

(1)隔离 DC/DC 转换器

- 架构与同步 :集成原边 LDO、全桥逆变器、空气芯变压器、副边整流器及 LDO,采用扩频时钟技术降低 EMI;DC/DC 工作频率需与调制器时钟同步,通过 DCDC_FREQ [3:0] 配置(支持 1.4MHz-4.1MHz 范围),避免干扰 ADC 采样。

- 故障检测 :SEC_FAIL 位(STATUS 寄存器)指示 DC/DC 故障(如副边供电不稳定、隔离通信错误),故障状态锁存,需读取 STATUS 寄存器清除;DC/DC 使能后需等待副边电压稳定(tPOR_SEC),通过两次读取 SEC_FAIL 确认正常后再采集 ADC 数据。

(2)高低侧电源分配

- 低压侧(低电位端) :DVDD(3.0V-5.5V)供电,需外接 1nF+1µF 去耦电容;DCDC_CAP 引脚(DC/DC 原边输入)外接 100nF 低 ESR 电容,靠近引脚布局。

- 高压侧(高电位端) :DCDC_OUT(3.0V)连接至 HLDO_IN,HLDO_OUT(2.6V-3.2V)为 ADC 模拟电路供电,外接 1nF+100nF 去耦电容;HGND 为高压侧地,需与分流电阻负极或电压分压网络地单点连接,避免地环流。

3. 功能安全与诊断

- 寄存器 CRC 校验 :启用后(REG_CRC_EN=1b)对可写寄存器空间(02h-31h)持续计算 16 位 CRC(CCITT/ANSI 多项式可选),REG_MAP 位指示 CRC 错误,保障配置数据完整性。

- SPI 通信安全 :4 线 SPI 接口(CS、SCLK、DIN、DOUT),支持 16/24/32 位数据宽度,输入 CRC(RX_CRC_EN)与输出 CRC(强制启用)可选,检测通信错误;SPI 超时功能(TIMEOUT=1b)防止 CS 永久拉低导致的通信挂死,超时周期 32768 个 MCLK 周期。

- 温度监测 :通道 2 可配置为内部 / 外部温度传感器模式(TS_EN=1b):

- 内部传感器:测量芯片结温,增益 = 8× 时误差 ±3°C(TA=25°C),适配器件过热保护。

- 外部传感器:支持 NTC/PTC 输入,通过 HLDO_OUT 分压提供基准,实现环境或传感器温度监测(如分流电阻温度补偿)。

4. 数字接口与控制

- 数据就绪与同步 :DRDY 引脚(低有效)指示新数据可用,可配置触发源(最滞后 / 最超前通道、所有通道 OR 逻辑);SYNC/RESET 引脚支持同步(脉冲宽度 1-tw (RSL) 个 CLK 周期)或硬件复位(脉冲宽度≥tw (RSL)=2048 个 CLK 周期),多器件同步采样时需同时触发 SYNC。

- GPIO 功能 :AIN2P/GPO 引脚可复用为通用输出(GPO_EN=1b),逻辑电平基于 HLDO_OUT,支持推挽驱动(最大 1mA 负载),可用于外部报警或继电器控制。

四、应用设计要点

1. 电源与布局设计

- 供电配置 :

- 低压侧:DVDD 外接 1nF(0603 封装,靠近引脚)+1µF(1206 封装)去耦电容,DCDC_CAP 外接 100nF 低 ESR 电容(X7R 材质)。

- 高压侧:DCDC_OUT 与 DCDC_HGND 间外接 1nF+1µF 电容,HLDO_OUT 与 HGND 间外接 1nF+100nF 电容;建议在 DCDC_OUT-HLDO_IN、DCDC_HGND-HGND 间串联铁氧体磁珠(如 Wurth 74269244182),降低 EMI。

- 隔离布局 :

- 严格区分高低侧地(HGND 与 DGND),单点连接(建议通过 PCB 地层单点互联),避免地环流。

- 高压采样电路(如电压分压)与低压控制电路(SPI)间距≥8mm,满足爬电距离;模拟信号迹线短而粗,数字迹线远离 ADC 输入,减少串扰。

- 分流电阻至 ADC 输入(AIN0P/AIN0N)采用对称布线,长度差≤0.5mm,降低寄生电感导致的相位差。

2. 模拟输入设计

- 电流采样 :

- 分流电阻选择:根据最大电流(如 100A)与 ADC 满量程(增益 = 32× 时 ±37.5mV)计算,推荐 200µΩ/2W 型号(电压降 ±20mV),温度系数<25ppm/°C。

- 抗混叠滤波:分流电阻与 ADC 输入间串联 RC 滤波器(推荐 50Ω+4.7nF,截止频率<数据率 1/2),双绞线传输差分信号,减少噪声耦合。

- 电压采样 :

- 分压网络:高压电压(如 240V)通过 2 个 1MΩ/200V 电阻分压(输出 450mV),电阻选用高精度(±0.1%)、低温度系数(<10ppm/°C)型号,分压节点串联 RC 滤波(1kΩ+10nF)。

- 伪差分配置:AIN12N(通道 1 负输入)连接至 VCMA(0.78V 偏置),适配高压单端信号转换为差分信号,提升 CMRR。

- 温度采样 :

- 内部传感器:通道 2 配置 TS_EN=1b、TS_SEL=0b,增益 = 8×,通过公式计算温度。

- 外部 NTC:串联 1kΩ 限流电阻,NTC 两端电压通过 ADC2 单端测量,利用分压比计算电阻值,再通过 NTC 特性曲线换算温度。

3. 初始化与同步

- 启动流程 :

- 上电后等待 DRDY 上升(tPOR=250µs),配置 CLK_DIV(如 N_DIV=2)与 DCDC_FREQ(匹配 fMOD)。

- 使能 DC/DC(DCDC_EN=1b),等待 SEC_FAIL 位清零(需两次读取 STATUS 寄存器确认)。

- 配置 ADC 增益、OSR、斩波模式,触发 SYNC 同步,等待滤波器建立时间(如 OSR=1024 时 3120 个 CLK 周期)后开始采集。

- 多器件同步 :

- 多 AMC131M03 并行时,共享 CLKIN 与 SYNC 信号,CS 独立控制;同步脉冲后需等待所有器件 DRDY 下降,确保采样时刻一致。

- 相位校准:以通道 0 为基准,通过 PHASE1、PHASE2 调整其他通道相位,补偿 PCB 布线或传感器导致的相位差(如电流通道滞后电压通道 10°,需配置相位延迟)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

深度解析AMC130M03:高精度三通道ADC的卓越之选2026-01-20 493

-

ADS131M03 三通道、24位、64kSPS、同步采样、Delta-Sigma ADC技术手册2025-11-01 1162

-

ADS131M03-Q1 技术文档总结2025-10-30 859

-

AMC131M03-Q1 汽车级隔离式 ΔΣ ADC 技术总结2025-10-28 854

-

德州仪器AMC131M03EVM评估模块技术解析与应用指南2025-08-14 2288

-

AMC131M02隔离式Δ-Σ ADC技术解析与应用指南2025-08-12 1215

-

AMC131M03评估模块(AMC131M03EVM)用户指南2024-11-06 826

-

AMC131M02 2通道、64kSPS、同步采样、24位增强型隔离式Δ-Σ ADC数据表2024-08-16 755

-

AMC131M03-Q1具有集成直流/直流转换器的汽车类、3通道、64kSPS、同步采样、24位增强型隔离式 Δ-Σ ADC数据表2024-08-15 539

全部0条评论

快来发表一下你的评论吧 !