PCIe Gen5/Gen6 信号传输可以用极细同轴线束吗?

描述

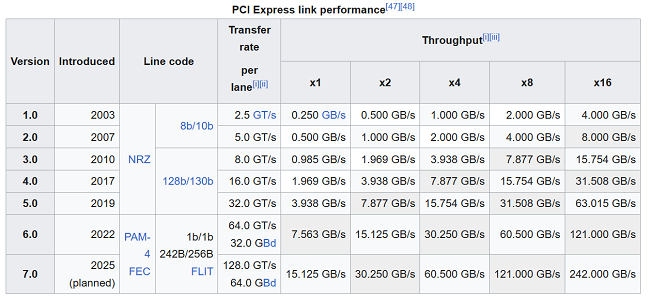

随着高速互连技术的不断演进,PCI Express(PCIe)标准已从 Gen3 的 8 GT/s 发展到 Gen5 的 32 GT/s,甚至到 Gen6 已达到 64 GT/s 级别。如此高的传输速率,对信号通道的损耗控制、阻抗匹配与抗干扰性能提出了前所未有的挑战。

在此背景下,设计工程师们开始探索新的互连方式——例如采用 极细同轴线束(micro coaxial cable),也就是内部用于传输高速信号的极细同轴结构电缆。它是否能胜任 PCIe Gen5/Gen6 的高速信号传输任务?下面我们从结构特性、信号完整性及设计要点三个角度进行分析。

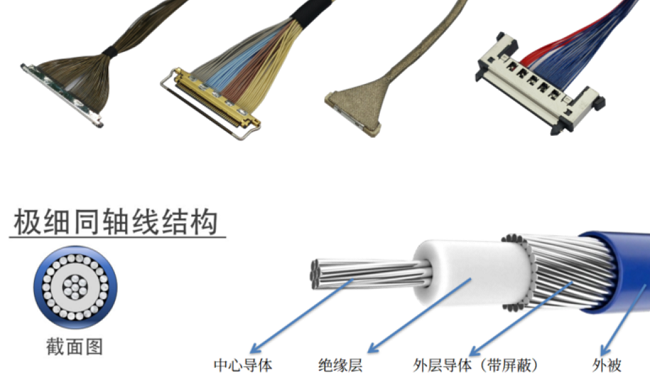

一、极细同轴线束的结构与特点

极细同轴线束由内导体、绝缘层、外导体屏蔽层及外护层组成,通常线径非常细(如 AWG 36~40),可实现高密度、柔性化布线。与传统的 PCB 差分走线相比,它具有以下几个显著特点:

1.1、高屏蔽性能:同轴结构能够有效抑制电磁干扰(EMI)与串扰。

1.2、柔性布线能力:可弯折、可绕行,适合空间受限的设备内部连接。

1.3、机械轻巧:重量轻、体积小,有助于模块化设计与小型化系统集成。

这些特性使得极细同轴线束在摄像模组、MIPI 接口、CoaXPress 工业相机等高速信号领域被广泛采用。那么,它是否同样适用于 PCIe Gen5/Gen6 呢?

二、PCIe Gen5/Gen6 的信号完整性挑战

PCIe Gen5 与 Gen6 的信号速率已进入几十 GHz 的频率范围,任何微小的不匹配或损耗都会导致误码率上升和眼图收缩。主要挑战包括:

2.1、带宽与插入损耗控制:通道损耗必须控制在极低范围内,否则信号幅度衰减严重。

2.2、回波损耗与阻抗一致性:系统要求严格的 85 Ω 或 100 Ω 差分阻抗匹配,任何过渡段都可能造成反射。

2.3、串扰与模式转换:多通道并行传输下的互扰问题更为突出。

2.4、通道均衡与噪声管理:需配合均衡电路、预加重及接收端滤波等方案共同优化。

这些因素共同决定了,PCIe Gen5/Gen6 的通道设计容差极小,对互连介质和结构的要求极为苛刻。

三、极细同轴线束用于 PCIe 高速信号的可行性分析

优势方面:

3.1、出色的屏蔽性能:同轴屏蔽层可显著降低外部干扰影响,对于高速通道非常有利。

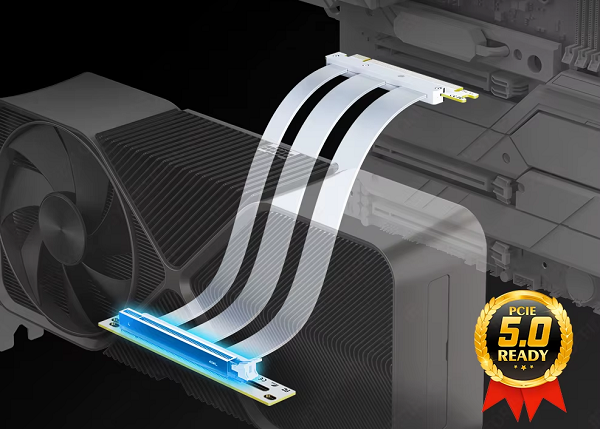

3.2、布局灵活性强:相比 PCB 差分走线,线束可在有限空间内灵活布设,特别适合模块化、可插拔或紧凑型系统。

3.3、模块化连接优势:通过高速连接器可实现板间、模组间连接,便于维护和升级。

挑战方面:

3.4、信号损耗问题:极细同轴线束直径小,内部导体与绝缘层尺寸限制导致插入损耗较大,频率越高衰减越明显。

3.5、阻抗匹配难度:需确保整个链路(包括连接器、线束及 PCB)阻抗保持一致,否则会引起反射和眼图闭合。

3.6、连接器与端接工艺要求高:高速同轴线的接头必须具备极低的寄生电容与电感特性,否则会成为系统瓶颈。

3.7、制造一致性与成本压力:微细结构对加工精度要求高,批量一致性与成本控制需权衡。

综合来看,极细同轴线束确实具备支撑 PCIe Gen5/Gen6 传输的潜力,但要在工程上实现稳定可靠的信号性能,必须满足严格的材料、电气与结构要求。

四、设计实践中的关键建议

4.1、尽量缩短线束长度:高速信号路径应尽可能短,避免多余的绕行或折弯。

4.2、阻抗匹配设计:建议采用差分对同轴结构(如双同轴线束)以获得更好的平衡特性。

4.3、高性能连接器选型:选择专为 32 GT/s 或更高速率设计的微同轴接口产品,确保端接稳定。

4.4、信号完整性仿真与实测:在设计阶段进行 S 参数仿真与眼图分析,并通过实测验证损耗与抖动指标。

4.5、结构固定与屏蔽接地:确保线束不因震动或应力而改变电气特性,屏蔽层接地可靠。

通过以上方法,极细同轴线束不仅能在结构空间上提供灵活性,还能在信号层面保持可控的损耗和低串扰,满足高速互联需求。极细同轴线束可在特定条件下用于 PCIe Gen5/Gen6 信号传输,但必须建立在高质量线束、严格的阻抗控制、专业的连接器选型与完善的信号仿真验证基础之上;对于高密度、模块化、可插拔的高速设计来说,它是一种值得探索的解决方案;但若忽视信号完整性与损耗控制,则可能导致严重的系统性能问题。

我是【苏州汇成元电子科技】,专注于高速信号互连与极细同轴线束定制,期待在电子发烧友平台与更多工程师一起深入探讨高速接口设计中的创新与实践!

-

高速信号传输为什么要用极细同轴线束?2025-08-22 1368

-

极细同轴线束能否传输电源?设计中的应用边界解析2025-08-24 1168

-

极细同轴线束到底是什么?一文带你入门2025-08-31 1221

-

极细同轴线束和USB线有什么不同?2025-09-04 1095

-

极细同轴线束在高速传输应用中如何控制和降低信号衰减?2025-09-07 965

-

极细同轴线束能做到多细?揭秘高速互连中的极限工艺2025-09-08 1290

-

极细同轴线束如何解决AI设备的高速信号传输难题?2025-09-11 1260

-

极细同轴线束能传输哪些信号?电子工程师必看入门指南2025-09-17 1441

-

极细同轴线与传统射频同轴线区别有哪些?2025-09-18 1587

-

极细同轴线束绝缘材料如何影响高速信号传输性能?2025-09-20 1430

-

USB3.1传输能用极细同轴线吗?要注意哪些选型误区?2025-09-26 1437

-

极细同轴线束在 HDMI 高速信号传输中的应用与全解析2025-10-21 650

-

极细同轴线束如何助力 MIPI 高速信号实现低损高稳传输?2025-10-22 463

-

极细同轴线束在Jetson摄像头高速传输中的结构与设计要点2025-10-29 289

-

极细同轴线束如何决定 USB 3.2 的真实传输速度?2025-10-30 428

全部0条评论

快来发表一下你的评论吧 !