AFE7768D双通道 RF 收发器技术总结

描述

AFE77xxD 是一个引脚兼容的高性能多通道收发器系列,集成了四个 (AFE7768D/AFE7769D) 或两个 (AFE7728D) 个直接上变频发射器链、四个 (AFE7768D/AFE7769D) 或两个 (AFE7728D) 直接下变频接收器链、两个宽带射频采样数字化辅助链(反馈路径)和用于功率放大器 (PA) 线性化的低功耗数字预失真 (DPD) 引擎。发射器和接收器链的高动态范围使无线基站能够发射和接收 2G、3G、4G 和 5G 信号。集成的波峰因数降低 (CFR) 单元有助于降低输入信号的峰均比 (PAR),从而通过功率放大器实现更高效的传输。集成的硬件加速 DPD 估计器和校正器为 PA 线性化提供了灵活高效的 DPD 解决方案。集成的 DPD 引擎可校正高达 200MHz (AFE77x8D) / 300MHz (AFE7769D) 瞬时带宽和高达 650MHz (AFE77x8D) / 730MHz (AFE7769D) DPD 扩展带宽内信号的 PA 非线性失真。专用的 GaN 校正器可解决由于 GaN PA 的电荷捕获而导致的长期非线性记忆效应。

*附件:afe7768d.pdf

AFE77xxD 的低功耗和高密度通道集成使该器件能够解决 4G 和 5G 基站的功率和尺寸限制。宽带和高动态范围反馈路径可以通过在各个拦截点进行智能数据捕获来辅助发射器链中功率放大器的 DPD。可用的 29.5Gbps SerDes 速度有助于减少将数据传入和传出设备所需的通道数量。

AFE77xxD 的每个接收器链包括一个 28 dB 范围数字步进衰减器 (DSA),然后是一个宽带无源 IQ 解调器,以及一个基带放大器,该放大器集成了具有可编程带宽的抗混叠低通滤波器,可驱动连续时间 Σ-Δ ADC。RX 链可以接收高达 200 MHz (AFE77x8D) / 300 MHz (AFE7769D) 的瞬时带宽 (IBW)。每个接收器通道都有两个模拟峰值功率检测器和各种数字功率检测器,以协助接收器通道的外部或内部自主 AGC 控制,以及一个用于器件可靠性保护的射频过载检测器。集成的 QMC(正交失配补偿)算法能够连续监控和校正 RX 链 I 和 Q 不平衡失配,而无需注入任何特定信号或执行离线校准。

每个发射器链包括两个 14 位、3.3 Gsps IQ DAC,然后是一个可编程重建和 DAC 镜像抑制滤波器,一个 IQ 调制器驱动具有 39 dB 范围增益控制的宽带 RF 放大器。TX 链集成了 QMC 和 LO 泄漏消除算法,利用 FB 路径可以持续跟踪和校正 TX 链 IQ 失配和 LO 泄漏。

每个FB路径都基于RF采样架构,包括一个驱动14位、3.3Gsps RF ADC的输入RF DSA。直接采样架构提供了固有的宽带接收器链,并简化了TX链损伤的校准。FB路径集成了两个独立的NCO,允许在两个观察到的RF输入频段之间快速切换。

合成器部分集成了四个小数N分频RF PLL,可以生成四个不同的RF LO,使该器件能够支持多达两个不同的频段,每个频段配置为两个发射器、两个接收器和一个反馈路径(带AFE7768D/AFE7769D),或者一个发射器、一个接收器和一个反馈路径(带AFE7728D)。

特性

- 基于 0-IF 上变频架构的四通道 (AFE776xD) / 双通道 (AFE7728D) 发射机:

- 每条链高达 650 MHz (AFE77x8D) / 730 MHz (AFE7769D) 的射频传输 DPD 扩展带宽

- 基于0-IF下变频架构的四通道(AFE776xD)/双通道(AFE7728D)接收器:

- 每条链高达 200 MHz (AFE77x8D) / 300 MHz (AFE7769D) 的射频接收带宽

- 基于直接射频采样架构的反馈链:

- 高达 650 MHz (AFE77x8D) / 730 MHz (AFE7769D) 的射频观察 DPD 扩展带宽

- 用于 PA 线性化的集成 CFR/DPD

- 高达 200MHz (AFE77x8D) / 300MHz (AFE7769D) 瞬时带宽

- 高达 650MHz (AFE77x8D) / 730MHz (AFE7769D) DPD 扩展带宽

- 用于 PA 线性化的集成 CFR/DPD

- 多级 CFR,具有可配置的消除脉冲

- 硬件加速 DPD 估计引擎

- 基于信号动力学的GaN PA线性化校正器

- 智能数据采集

- 射频频率范围:600 MHz 至 6 GHz

- 四个宽带小数N PLL,用于TX和RX LO的VCO

- 专用整数 N PLL、VCO,用于数据转换器时钟生成

- JESD204B和JESD204C SerDes 接口支持:

- 4 个高达 29.5 Gbps 的 SerDes 收发器

- 8b/10b 和 64b/66b 编码

- 16 位、12 位、24 位和 32 位格式化

- 子类 1 多设备同步

- 封装:17 mm × 17 mm FCBGA,0.8 mm 间距

参数

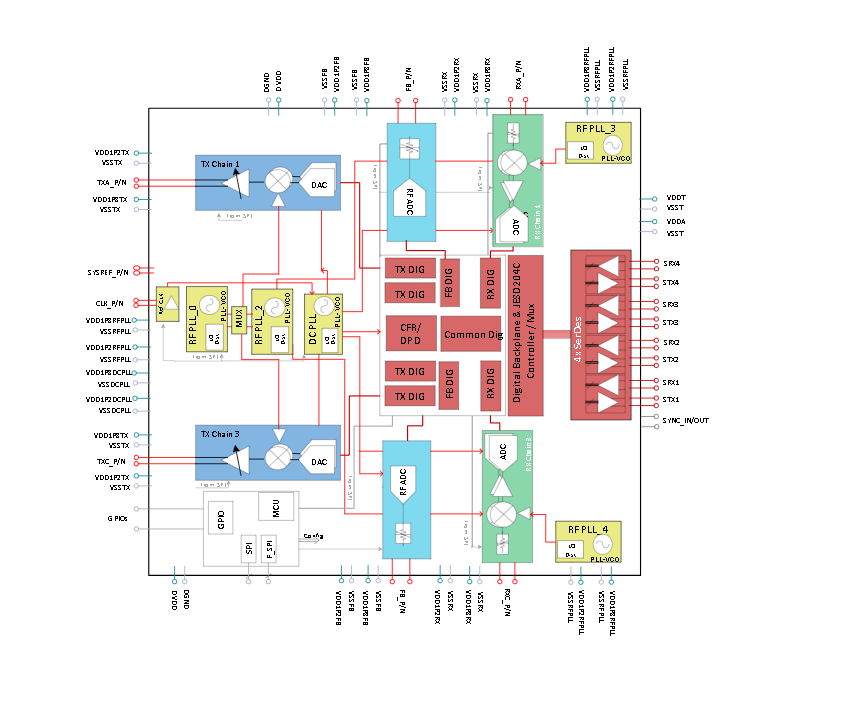

方框图

一、核心特性与产品定位

1. 基础参数与架构

- 通道配置 :

- 发射链路(TX):2 条 0-IF 上变频链路,每条支持最高 650MHz DPD 扩展带宽(瞬时带宽 200MHz),集成 14 位 3.3Gsps IQ DAC、可编程重建滤波器及 39dB 增益控制的 RF 放大器。

- 接收链路(RX):2 条 0-IF 下变频链路,每条支持最高 200MHz 瞬时带宽,集成 28dB 数字步进衰减器(DSA)、宽带无源 IQ 解调器、抗混叠低通滤波器及连续时间 sigma-delta ADC。

- 反馈路径(FB):2 条基于直接 RF 采样的辅助链路,每条集成 14 位 3.3Gsps RF ADC、输入 RF DSA 及 2 个独立 NCO(数控振荡器),支持快速切换观测频段,辅助 TX 链路校准与 PA 线性化。

- 核心增强功能 :

- PA 线性化:内置硬件加速 DPD 估计器与校正器,支持 GaN PA 电荷捕获导致的长期非线性记忆效应补偿,DPD 扩展带宽最高 650MHz,瞬时带宽 200MHz,降低 PA 非线性失真。

- 信号优化:集成多阶段 CFR(峰值因子降低),可配置抵消脉冲,减少输入信号峰均比(PAR),提升 PA 效率。

- 校准能力:TX/RX 链路均支持正交失配补偿(QMC)与 LO 泄漏抵消,无需注入特定信号或离线校准,实时修正 I/Q 失衡与本振泄漏。

- 频率与时钟 :

- RF 频率范围:600MHz-6GHz,覆盖 4G/5G 主流频段(如 Sub-6GHz)。

- 时钟生成:集成 4 个分数 - N RF PLL(生成 TX/RX LO)与 1 个整数 - N PLL(为数据转换器提供时钟),支持 4 种不同 RF LO,可适配 2 个不同工作频段。

- 接口与同步 :

- 高速接口:支持 JESD204B/C SerDes,4 个 SerDes 收发器最高速率 29.5Gbps,支持 8b/10b 与 64b/66b 编码,16/12/24/32 位数据格式,减少数据传输 lanes 数量。

- 同步能力:支持 Subclass 1 多器件同步,通过 SYSREF 与 SYNC 引脚实现多 AFE7728D 或多通道系统的时钟与数据同步,适配 mMIMO(大规模多输入多输出)场景。

2. 环境适应性与封装

- 工作条件 :

- 温度范围:-40°C 至 85°C,满足工业级宽温需求,适配基站户外机柜、分布式天线等复杂环境。

- 供电:多组电源域(如 1.2V TX、1.8V FB、1.2V DCPLL),需严格遵循电源时序要求,降低噪声耦合。

- 封装与可靠性 :

- 封装:17mm×17mm FCBGA(球栅阵列),400 引脚,0.8mm 引脚间距,底部无热焊盘(需通过 PCB 布局优化散热)。

- ESD 防护:需遵循静电放电防护规范(如人体放电模型 HBM±2000V),避免装配与使用过程中器件损坏。

3. 典型应用场景

- 5G 小基站 / 宏基站 :作为 RRU(远程射频单元)核心收发器,支持多频段信号发射与接收,DPD/CFR 功能提升 PA 效率,降低基站功耗。

- 有源天线系统(AAS) :适配 mMIMO 架构,多器件同步能力支持多通道信号协同,满足大规模天线阵列的高精度相位与幅度一致性要求。

- 分布式天线系统(DAS) :小型化封装与低功耗特性,适配室内分布式覆盖场景,宽频段支持可兼容多运营商频段。

- 中继器(Repeater) :高动态范围 RX 链路可接收弱信号,TX 链路的功率控制与线性化能力确保中继信号质量。

二、关键性能参数

1. 核心射频性能(典型值,常温环境)

| 性能类别 | 参数 | 规格 | 单位 |

|---|---|---|---|

| 发射链路(TX) | 瞬时带宽(IBW) | 200 | MHz |

| DPD 扩展带宽 | 650 | MHz | |

| DAC 分辨率 / 速率 | 14 位 / 3.3Gsps | - | |

| 增益控制范围 | 39 | dB | |

| LO 泄漏(@2GHz) | -60 | dBm | |

| 接收链路(RX) | 瞬时带宽(IBW) | 200 | MHz |

| ADC 动态范围(DR) | 65 | dB | |

| 噪声系数(NF) | 4.5 | dB | |

| DSA 衰减范围 | 28 | dB | |

| 输入三阶截点(IIP3) | -10 | dBm | |

| 反馈路径(FB) | ADC 分辨率 / 速率 | 14 位 / 3.3Gsps | - |

| 输入带宽 | 600-6000 | MHz | |

| DSA 衰减范围 | 31 | dB | |

| DPD/CFR | DPD 校正带宽 | 650(扩展)/200(瞬时) | MHz |

| CFR 峰值抑制 | 6 | dB |

三、核心功能架构

1. 发射链路(TX)

- 信号流程 :基带 IQ 数据经 JESD204C 接口输入,由 14 位 3.3Gsps IQ DAC 转换为模拟信号,经可编程重建滤波器与 DAC 镜像抑制滤波器处理后,送入 IQ 调制器与 RF 放大器,最终通过 TX 天线端口输出。

- 关键模块 :

- IQ 调制器:实时修正正交失衡(通过 QMC 算法)与 LO 泄漏,保障调制精度。

- RF 放大器:39dB 增益控制范围,支持精细功率调节,适配不同 PA 驱动需求。

- DPD 集成:DPD 引擎根据 FB 路径反馈的 PA 输出信号,生成预失真系数,对 TX 输入信号进行预处理,抵消 PA 非线性失真。

2. 接收链路(RX)

- 信号流程 :RF 信号经 RX 天线端口输入,先通过 28dB DSA 调节衰减(适配不同强度输入信号),再经宽带无源 IQ 解调器下变频至基带,由抗混叠低通滤波器滤除高频噪声,最终送入连续时间 sigma-delta ADC 转换为数字信号,通过 JESD204C 接口输出。

- 关键模块 :

- 功率检测:集成 2 个模拟峰值功率检测器与多个数字功率检测器,辅助外部 / 内部 AGC(自动增益控制),保护器件免受过载损伤。

- QMC 算法:实时监测并修正 I/Q 通道幅度与相位失衡,无需离线校准,确保接收信号保真度。

3. 反馈路径(FB)

- 核心作用 :通过直接 RF 采样采集 PA 输出信号,送入 14 位 3.3Gsps RF ADC 转换为数字信号,用于 TX 链路 QMC 校准、LO 泄漏抵消及 DPD 系数估计。

- 灵活性设计 :2 个独立 NCO 支持快速切换 2 个观测频段,无需重新配置硬件,适配多频段 PA 线性化场景;输入 RF DSA 可调节信号幅度,确保 ADC 工作在最佳动态范围。

4. 时钟与同步

- PLL 配置 :4 个分数 - N RF PLL 生成 TX/RX 所需的 RF LO(600MHz-6GHz),支持 4 种不同频率,可同时适配 2 个工作频段;1 个整数 - N PLL 为 DAC/ADC 提供高精度时钟,保障数据转换器性能。

- 多器件同步 :支持 JESD204B/C Subclass 1 同步,通过 SYSREF(系统参考时钟)与 SYNC(同步信号)引脚,实现多 AFE7728D 之间的时钟相位对齐与数据帧同步,满足 mMIMO 多通道协同需求。

-

AFE8004射频采样收发器技术文档总结2025-10-29 331

-

AFE77xxD 系列射频收发器技术总结2025-10-28 546

-

AFE8092八通道RF收发器技术解析与应用指南2025-09-12 659

-

德州仪器AFE80xx系列RF采样收发器技术解析与应用设计指南2025-09-08 1069

-

德州仪器AFE77xxD系列射频收发器技术解析与应用指南2025-08-14 846

-

ADRV9003窄带/宽带RF收发器技术手册2025-04-19 948

-

AFE8092IABJ 宽带宽多通道收发器的中文资料2021-12-16 1814

-

AFE7900IABJ宽带宽多通道收发器 中文资料2021-12-14 1275

-

集成式RF采样收发器能实现什么功能?2019-09-18 1889

-

新型RF收发器对微微蜂窝基站发展的影响2019-06-27 1686

-

TI推出业内首款集成四通道和双通道射频采样收发器,实现多天线宽带系统2019-03-06 822

-

双通道、降压转换器用于为RF收发器供电2010-02-24 1016

全部0条评论

快来发表一下你的评论吧 !