AFE7954 四通道射频采样 12 GSPS 数模转换器(DAC)技术总结

描述

AFE7954是一款高性能、宽带宽的四通道RF采样DAC。该器件的工作频率高达 12 GHz,可在 L、S、C 和 X 波段频率范围内实现直接射频采样,而无需额外的变频级。这种密度和灵活性的提高使高通道数的多任务系统成为可能。

信号路径支持插值和数字上变频选项,为四个DAC (TX)提供高达1200 MHz的信号带宽,为两个DAC提供高达2400 MHz的信号带宽。DUC 的输出驱动 12GSPS DAC(数模转换器),具有混合模式输出选项,以增强二次奈奎斯特作。DAC输出包括一个可变增益放大器(TX DSA),具有40 dB范围和1 dB模拟步长和0.125 dB数字步长。

*附件:afe7954.pdf

特性

- 四通道射频采样 12GSPS DAC

- 最大射频信号带宽:

- 4TX:1200 MHz 或

- 2TX:2400 兆赫

- 射频频率范围:600 MHz - 12 GHz

- 数字步进衰减器 (DSA):

- TX:40 dB 范围,0.125 dB 步长

- 单频或双频 DUC

- 每个 TX 16 个士官

- 可选的内部PLL/VCO,用于DAC或DAC采样率的外部时钟

- SerDes 数据接口:

- JESD204B和JESD204C兼容

- 8 个 SerDes 接收器,速度高达 29.5 Gbps

- 子类 1 多设备同步

- 封装:17 mm × 17 mm FCBGA,0.8 mm 间距

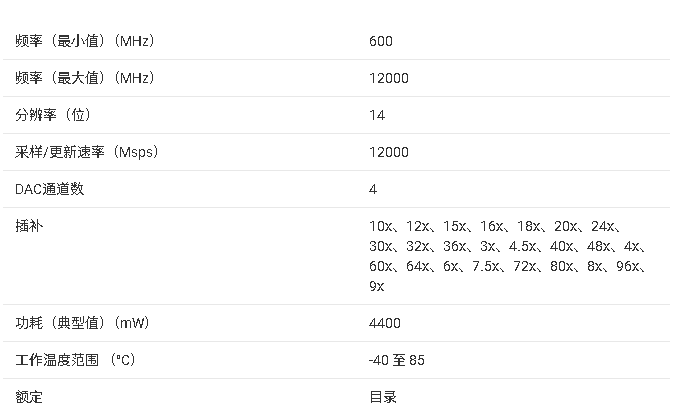

参数

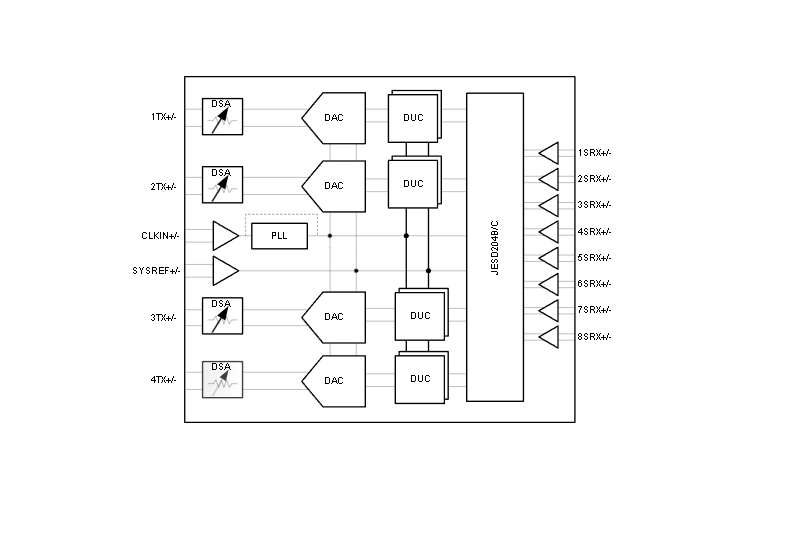

方框图

AFE7954 是德州仪器(Texas Instruments)推出的 高性能四通道射频采样数模转换器(DAC) ,专为超宽频、高带宽射频信号处理设计,集成 4 路发射(TX)通道、灵活的数字上变频(DUC)与时钟锁相环(PLL)模块,支持 600MHz-12GHz 射频频率范围,可直接覆盖 L、S、C、X 等关键频段,满足雷达、制导前端、国防通信及无线测试设备对高动态范围、低噪声与高集成度的严苛需求。以下从核心特性、性能参数、功能架构、应用设计及订购信息等方面展开总结。

一、核心特性与产品定位

1. 基础参数与架构

- 通道与分辨率 :

- 通道配置:4 路独立发射(TX)通道,支持单通道 / 双通道高带宽模式(4TX 时 1200MHz 带宽、2TX 时 2400MHz 带宽),适配多频段同时发射场景(如国防通信多波形传输)。

- 分辨率:14 位 DAC(数模转换器),兼顾信号精度与采样速率,在 12GSPS 最高采样率下仍保持低失真特性,满足复杂射频信号生成需求。

- 频率与带宽 :

- 射频频率范围:600MHz-12GHz,覆盖 Sub-6GHz(5G)、毫米波低段(6-12GHz)及卫星通信频段,支持 “直接射频采样” 架构,无需额外混频器,简化系统设计。

- 采样率:DAC 最高 12GSPS(吉采样 / 秒),支持 1st Nyquist(600MHz-6GHz)与 2nd Nyquist(6-12GHz)双模式,通过交织(Interleave)与混合(Mix Mode)技术扩展频率覆盖。

- 供电与功耗 :

- 供电电压:多组供电域,涵盖 0.9V(数字核心,如 DVDD0P9)、1.2V(模拟电路,如 VDD1P2RX/TX)、1.8V(射频与 GPIO,如 VDD1P8TXDAC),适配不同模块功耗需求。

- 功耗:正常工作模式(4TX 单频段)典型功耗 5011mW,休眠模式低至 1132mW,平衡高性能与低功耗(如雷达间歇工作场景节能需求)。

- 封装与可靠性 :

- 封装:17mm×17mm 400 引脚 FC-BGA(球栅阵列),带散热焊盘,结到板热阻 4.85°C/W,优化高温环境(如密闭制导设备)散热。

- 工业级标准:工作温度 - 40°C 至 + 85°C(环境温度)、结温最高 125°C,ESD 防护(人体放电模型 HBM±1000V、带电设备模型 CDM±150V),满足国防与工业领域可靠性要求。

2. 核心增强功能

- 灵活的增益与衰减控制 :

- 数字步进衰减器(DSA):每路 TX 通道集成 40dB 范围 DSA,支持 1dB 模拟步进与 0.125dB 数字步进,校准后衰减精度(DNL)±0.1dB,可实时调整发射功率,适配不同链路损耗(如雷达目标距离变化)。

- 增益平坦度:600MHz 带宽内增益平坦度 ±1.2dB,20MHz 窄带内 ±0.1dB,确保宽频段内信号幅度一致性,避免频段间功率波动。

- 高动态范围与低失真 :

- 线性度:三阶互调失真(IMD3)低至 - 88dBc(850MHz,-13dBFS 双音输入),杂散抑制比(SFDR)最高 79.4dBc(1.8GHz),减少信号失真,保障射频信号纯度(如雷达波形无杂散干扰)。

- 噪声性能:噪声谱密度(NSD)低至 - 157.6dBFS/Hz(850MHz,0dB 衰减),在宽频率范围内保持低噪声,适配微弱信号放大场景(如国防通信低功率发射)。

- 时钟与同步能力 :

- 集成 PLL/VCO:内置 4 组 VCO(压控振荡器),覆盖 7.2-12.08GHz 频率范围,闭环相位噪声低至 - 146dBc/Hz(11.79848GHz,50MHz 偏移),支持内部 PLL 或外部时钟驱动 DAC,确保时钟信号低抖动。

- 多设备同步:支持 JESD204B/C 接口 Subclass 1 同步,8 路 SerDes 接收器最高 29.5Gbps 速率,可实现多片 AFE7954 时钟与数据同步,适配大规模多通道系统(如相控阵雷达)。

- 数字信号处理 :

- 数字上变频(DUC):每路 TX 通道集成单 / 双频段 DUC,支持 16 个数控振荡器(NCO),可直接将基带信号上变频至射频频段,减少外部变频电路,降低系统复杂度。

- 插值滤波:支持 8×-96× 灵活插值,将低速率基带信号提升至 12GSPS DAC 采样率,适配不同基带数据源(如 FPGA 输出的 500MSPS 信号)。

3. 典型应用场景

- 雷达与制导系统 :支持 600MHz-12GHz 宽频段信号生成,14 位 DAC 与低 IMD3 特性可生成复杂雷达波形(如线性调频 LFM),适配车载雷达、防空雷达等。

- 国防通信 :4 通道独立发射支持多频段同时传输(如 1.8GHz+2.6GHz 双频段通信),1200MHz 带宽可承载高速率数据链,满足战术通信需求。

- 无线测试设备 :直接射频采样架构可模拟多标准射频信号(如 5G NR 100MHz、LTE 20MHz),误差向量幅度(EVM)低至 0.2%(850MHz),满足信号发生器高精度测试需求。

二、关键性能参数

1. 核心电气性能(典型值,TA =25**∘**C, nominal 供电)

| 性能类别 | 参数 | 规格(典型值) | 单位 |

|---|---|---|---|

| DAC 核心 | 分辨率 | 14 位 | bit |

| 最高采样率 | 12 GSPS | GSPS | |

| 输出阻抗 | 50 Ω(默认) | Ω | |

| 射频输出 | 全量程输出功率(850MHz) | 4.2 dBm(-0.5dBFS 输入) | dBm |

| 三阶互调失真(IMD3) | -88 dBc(850MHz,-13dBFS 双音) | dBc | |

| 杂散抑制比(SFDR) | 79.4 dBc(1.8GHz) | dBc | |

| DSA 衰减范围 | 0-40 dB(0.125dB 数字步进) | dB | |

| 噪声性能 | 噪声谱密度(NSD) | -157.6 dBFS/Hz(850MHz,0dB 衰减) | dBFS/Hz |

| 时钟与 PLL | VCO 频率范围 | 7.2-12.08 GHz | GHz |

| 闭环相位噪声 | -146 dBc/Hz(11.79848GHz,50MHz 偏移) | dBc/Hz | |

| SerDes 速率 | 最高 29.5 Gbps | Gbps | |

| 同步与 EVM | JESD204C 同步 subclass | 1(多设备同步) | - |

| 误差向量幅度(EVM) | 0.2%(850MHz,20MHz LTE 信号) | % |

三、核心功能架构

1. 发射(TX)模块

(1)DAC 与信号调理

- DAC 核心特性 :

- 14 位分辨率,支持 “交织模式”(1st Nyquist)与 “混合模式”(2nd Nyquist),12GSPS 采样率下在 12GHz 频段仍保持低失真(如 9.6GHz 时 IMD3=-52dBc),适配毫米波信号生成。

- 输出驱动:内置可变增益放大器(VGA),配合 40dB DSA 实现发射功率精细控制,满足不同距离目标的信号覆盖需求(如雷达近距离低功率、远距离高功率切换)。

- 数字上变频(DUC) :

- 单 / 双频段支持:每路 TX 通道可配置为单频段(如仅 3.5GHz)或双频段(如 1.8GHz+2.6GHz),16 个 NCO 可独立设置频率,实现多波形同时上变频,无需外部混频器。

- 插值滤波:支持 8×-96× 插值,通过半带滤波器与 FIR 滤波器抑制镜像频率,确保插值后信号杂散低于 - 60dBc,简化后端射频滤波设计。

(2)线性度与杂散控制

- 预失真优化 :内置数字预失真(DPD)电路,可补偿 DAC 非线性失真,在高输出功率下(如 4.2dBm@850MHz)仍保持低 IMD3(-66dBc@-7dBFS 双音),提升复杂信号(如 5G NR)的线性度。

- 杂散抑制 :通过优化 DAC 电流源设计与时钟抖动控制,固定杂散(如 fS/4、fS/2)低于 - 48dBFS,确保射频输出信号纯度,避免对邻近频段的干扰(如国防通信中避免杂散泄露)。

2. 时钟与 PLL 模块

(1)PLL/VCO 时钟生成

- 多 VCO 覆盖 :集成 4 组 VCO(VCO1:7.2-8.8GHz、VCO2:8.8-9.7GHz、VCO3:9.7-11.6GHz、VCO4:11.6-12.08GHz),通过分频系数(1/2/3/4/6)适配不同 DAC 采样率(如 12GSPS 需 12GHz VCO 时钟)。

- 相位噪声优化 :PLL 环路滤波器支持软件配置,在 11.79848GHz 频率下,100Hz 偏移相位噪声 - 88dBc/Hz、1MHz 偏移 - 136dBc/Hz,减少时钟噪声对 DAC 输出信号的影响(如避免相位噪声导致雷达测距误差)。

(2)时钟同步与分发

- 外部时钟接口 :支持 491.52MHz 参考时钟输入(REFCLK),可通过 PLL 倍频至 12GHz,也可直接接入外部 12GHz 时钟驱动 DAC,适配不同系统时钟架构。

- JESD204C 同步 :8 路 SerDes 接收器支持 29.5Gbps 速率,Subclass 1 同步模式可实现多片 AFE7954 的时钟与数据对齐,同步误差低于 50ps,满足相控阵雷达波束成形需求。

3. 数字接口与控制

- SPI 配置接口 :支持 SPI 接口配置 DAC 增益、DSA 衰减、PLL 频率等参数,寄存器写入时钟周期最低 25ns,适配系统动态参数调整(如实时切换雷达波形频率)。

- 监控与保护 :每路 TX 通道集成射频过压检测器与峰值功率检测器,可实时监控输出功率,避免过功率损坏外部功率放大器(PA),提升系统可靠性。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

AFE7954:高性能四通道射频采样DAC的卓越之选2026-01-26 321

-

AFE7954四通道射频采样DAC技术解析与应用指南2025-08-21 1300

-

DAC8775四通道数模转换器数据表2024-07-31 624

-

DAC8555四通道、电压输出数模转换器(DAC)数据表2024-07-29 834

-

DAC7664四通道电压输出数模转换器(DAC)数据表2024-07-24 725

-

DAC7564四通道、12位数模转换器(DAC)数据表2024-06-20 593

-

UG-975:评估AD5324 12位四通道电压输出数模转换器(DAC)2021-05-13 1488

-

高性能16位数模转换器AD9164怎么样?2019-10-23 3157

-

ADI发布最快四通道中频数模转换器2014-06-05 3967

全部0条评论

快来发表一下你的评论吧 !