ADC12DJ5200SE 射频采样模数转换器(ADC)技术文档总结

描述

该ADC12DJ5200SE是一款RF采样、千兆采样、模数转换器(ADC),集成了输入巴伦。该ADC12DJ5200SE可配置为双通道 5.2 GSPS ADC 或单通道 10.4 GSPS ADC。2 至 6.3GHz 的 -3dB 输入频率范围支持频率捷变系统的 S 波段和 C 波段的直接射频采样。

该ADC12DJ5200SE采用高速JESD204C输出接口,具有多达16个串行通道,支持高达17.16Gbps的线速。通过JESD204C子类 1 支持确定性延迟和多设备同步。JESD204C接口可以配置为权衡线路速率和通道数。支持 8b/10b 和 64b/66b 数据编码方案。64b/66b 编码支持前向纠错 (FEC),以提高误码率。该接口向后兼容JESD204B接收器。

*附件:adc12dj5200se.pdf

创新的同步功能,包括无噪声孔径延迟调整和 SYSREF 窗口,简化了多通道应用的系统设计。可选的数字下变频器(DDC)可用于提供基带的数字转换并降低接口速率。可编程FIR滤波器允许片内均衡。

特性

- ADC内核:

- 12 位分辨率

- 单通道模式下高达 10.4GSPS

- 双通道模式下高达 5.2GSPS

- 单端50Ω输入:

- 模拟输入范围 (–3dB):2 至 6.3GHz

- 满量程输入功率 (4.5GHz): - 1.25dBm

- 灵活的 VCM:交流耦合,无直流路径到 GND 或电源

- 性能规格:

- 本底噪声(2.3GHz,–20dBFS,INPUTFS = 1.5dBm):

- 双通道模式:–149dBFS/Hz

- 单通道模式:–151.5dBFS/Hz

- ENOB(双通道,FIN = 2.3GHz):8.5 位

- 本底噪声(2.3GHz,–20dBFS,INPUTFS = 1.5dBm):

- 无噪声孔径延迟 (tAD) 调节:

- 精确采样控制:19fs 步长

- 简化同步和交错

- 温度和电压不变延迟

- 易于使用的同步功能:

- 自动 SYSREF 定时校准

- 样品标记的时间戳

- JESD204C串行数据接口:

- 最大通道速率:17.16Gbps

- 支持 64b/66b 和 8b/10b 编码

- 8b/10b 模式JESD204B兼容

- 可选数字下变频器 (DDC):

- 4 倍、8 倍、16 倍和 32 倍复数抽取

- 每个DDC有四个独立的32位NCO

- 峰值射频输入功率:+26.25dBm(+ 27.5dBFS,560倍满量程功率)

- 用于均衡的可编程 FIR 滤波器

- 功耗:4W

- 电源:1.1V、1.9V

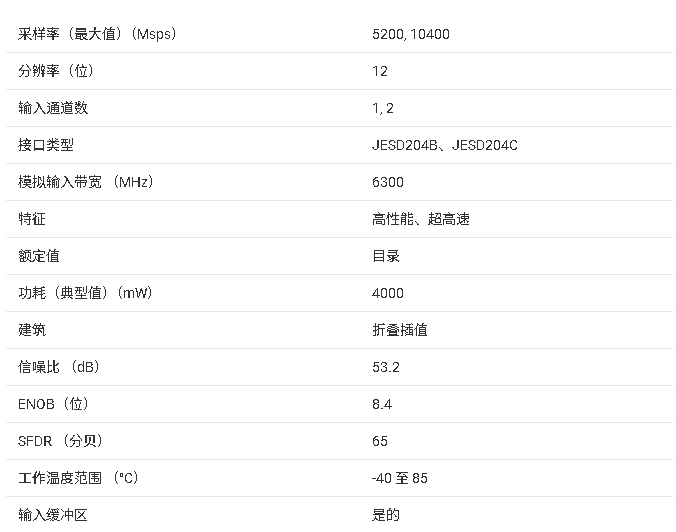

参数

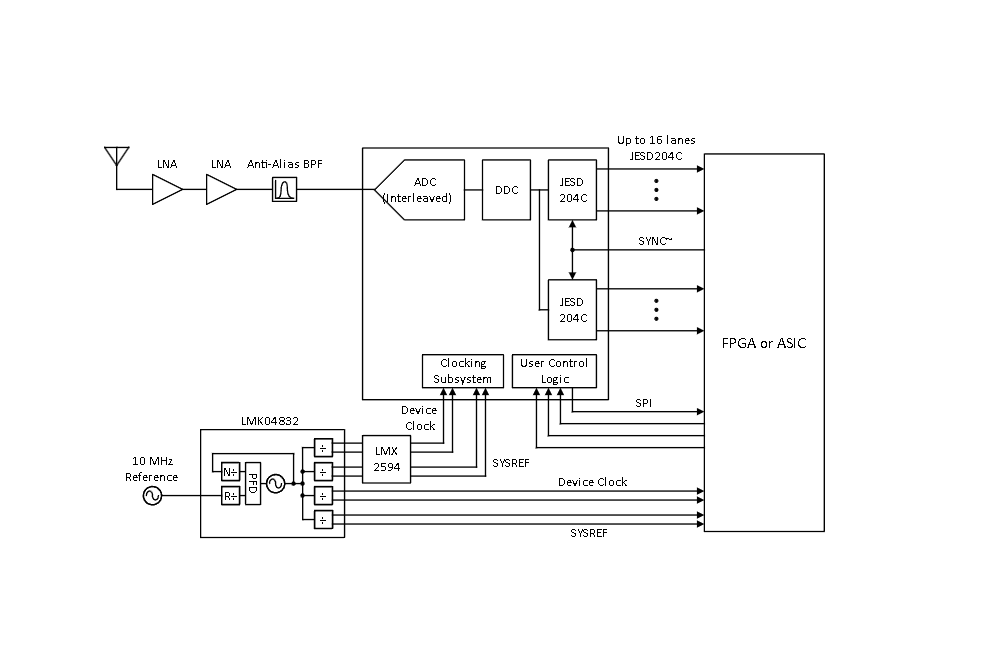

方框图

一、产品概述

ADC12DJ5200SE 是一款 12 位分辨率的 RF 采样 ADC,集成输入平衡 - 不平衡转换器(Balun),支持两种核心工作模式: 单通道模式 (最高 10.4GSPS 采样速率)与 双通道模式 (每通道最高 5.2GSPS 采样速率)。器件采用 144 引脚 FCBGA 封装(尺寸 10mm×10mm),工作温度范围 - 40°C 至 + 85°C,核心优势在于无需传统中频(IF)转换环节,可直接对 2~6.3GHz 的射频信号采样,大幅简化系统架构,同时通过 JESD204C 高速串行接口实现数据高效传输,兼顾性能与集成度。

二、核心特性

1. 采样与射频性能

- 分辨率与速率 :12 位固定分辨率,单通道模式下采样速率最高 10.4GSPS(依赖双沿采样技术),双通道模式下每通道最高 5.2GSPS,满足高带宽信号实时采集需求。

- 输入特性 :单端 50Ω 输入阻抗,-3dB 输入频率范围 2~6.3GHz(覆盖 S 波段与 C 波段);4.5GHz 频率下满量程输入功率为 - 1.25dBm,峰值 RF 输入功率可达 + 26.25dBm(560 倍满量程功率),具备较强的信号过载耐受能力。

- 噪声与失真性能 :在 2.3GHz 输入、-20dBFS 信号强度下,单通道模式噪声基底低至 - 151.5dBFS/Hz,双通道模式为 - 149dBFS/Hz;双通道模式下有效位数(ENOB)达 8.5 位,3 次互调失真(IMD3)、2 次谐波失真(HD2)等关键指标优异,保证信号还原精度。

2. 信号处理与同步

- 数字下变频器(DDC) :可选配 4 倍、8 倍、16 倍、32 倍复数抽取功能,每路 DDC 配备 4 个独立 32 位数控振荡器(NCO),支持信号混频至基带,降低后端数据处理压力;支持快速频率跳变(FFH),NCO 切换 latency 低至 45~68 个采样时钟周期,适配跳频通信、多目标雷达等场景。

- 同步能力 :支持 JESD204C 子类 1(Subclass 1)多设备同步,通过 SYSREF 信号实现确定性延迟;具备无噪声孔径延迟(t_AD)调整功能,步长精度达 19 飞秒(fs),可精准对齐多 ADC 采样时序,且延迟不受温度与电压变化影响;支持自动 SYSREF 时序校准与采样标记时间戳(Timestamp),简化多通道系统同步设计。

- 滤波与均衡 :集成可编程 FIR 滤波器(PFIR),支持单 / 双通道均衡、时变滤波(如 I/Q 校正),可通过寄存器配置 9 抽头系数,补偿信号传输过程中的频率衰减,优化信号完整性。

3. 接口与功耗

- JESD204C 接口 :最高支持 16 路串行通道(Lane),每路最高速率 17.16Gbps,兼容 8b/10b(支持 JESD204B)与 64b/66B 编码(支持前向纠错 FEC,提升误码性能);支持弹性缓冲区(Elastic Buffer)释放点配置,确保多设备间数据传输的时序一致性。

- 控制接口 :配备 SPI 接口用于寄存器配置(如采样模式、DDC 参数),GPIO 接口支持时序同步(如 SYNC 信号)与状态指示;支持测试模式(如 PRBS 序列、时钟图案),便于系统调试。

- 功耗与电源 :典型功耗 4W,需 1.1V(模拟 / 数字)与 1.9V(模拟)两组电源,每组电源需就近并联 0.1μF 去耦电容,保证供电稳定性。

三、工作模式与功能配置

1. 核心工作模式

ADC12DJ5200SE 通过JMODE 寄存器配置工作模式,覆盖单 / 双通道、不同抽取率与编码方式,核心模式差异如下表:

| 模式类型 | 关键参数(示例) | 适用场景 |

|---|---|---|

| 单通道模式 | 10.4GSPS 采样率,8/16 路 JESD204C 通道,8b/10b 或 64b/66B 编码 | 高带宽单信号采集(如雷达) |

| 双通道模式 | 每通道 5.2GSPS 采样率,8/16 路 JESD204C 通道,支持独立信号采集 | 双路并行信号监测(如通信测试) |

| DDC 抽取模式 | 支持 4x/8x/16x/32x 复数抽取,输出 15 位复数数据(含过 range 标记位) | 窄带信号提取(如电子战) |

| 双输入单通道模式 | 双输入分别驱动交错 ADC,采样率 2× 时钟频率,适配前端交错跟踪保持放大器(T&H)输出 | 超高带宽信号扩展采集 |

2. 校准与补偿功能

- 校准模式 :支持 前景校准 (系统启动时执行,ADC 离线,输出中值代码)与 背景校准 (ADC 正常工作时轮换校准核心,无数据中断),可校准增益、偏移与线性误差;额外支持偏移校准(短接输入后写入偏移值)与增益校准(输入已知电压计算增益系数),校准后信号误差显著降低。

- 抖动抑制 :集成抖动(Dither)功能,可通过寄存器调整抖动幅度(小 / 大抖动),在牺牲少量信噪比(SNR)的前提下,优化杂散性能,减少信号失真。

四、电气特性

1. 直流特性

- 电源与电流 :1.1V 模拟电源(VA11)典型电流 845mA,1.9V 模拟电源(VA19)典型电流 934mA,1.1V 数字电源(VD11)典型电流 1170mA;掉电模式下总电流仅 104mA(VA19=44mA、VA11=27mA、VD11=33mA),兼顾正常运行与低功耗需求。

- 偏移与漂移 :未校准偏移误差典型值 ±0.06% FSR,校准后降至 ±0.02% FSR;偏移温度漂移低至 0m% FSR/°C(需 Foreground+FGOS 校准),保证宽温环境下的稳定性。

- 基准电压 :内置带隙基准(BG 引脚输出),典型值 1.1V,温度漂移 - 64μV/°C,可作为外部电路参考。

2. 交流与时序特性

- 带宽与响应 :-1dB 输入带宽低至 3.0GHz(单通道)、3.4GHz(双通道),-3dB 带宽覆盖 2

6.3GHz,保证宽频信号无衰减采集;输入返回损耗优于 - 10dB(210GHz 范围),减少信号反射。 - 时序精度 :孔径延迟(t_AD)典型值 360ps,支持 1.13ps 粗调与 19fs 细调;孔径抖动(t_AJ)低至 50fs(RMS),确保高采样速率下的时序一致性;JESD204C 接口延迟确定性高,支持多设备同步采样。

五、封装与订购信息

1. 封装规格

器件采用 144 引脚 FCBGA 封装(型号 AAV/ZEG),关键参数如下:

- 尺寸:10mm×10mm,最大高度 2.65mm,引脚间距 0.8mm;

- 焊球配置:底部裸露热焊盘,需焊接至 PCB 接地平面优化散热;焊球材质可选无铅(SnAgCu,ABJ 封装)或含铅(SnPb,ALK 封装),适配不同 RoHS 合规需求;

- 热特性:结到环境热阻(RθJA)23.9°C/W,结到板热阻(RθJB)8.4°C/W,需合理设计 PCB 散热路径。

2. 订购型号

ADC12DJ5200SE 主要订购型号及参数如下表,均符合 Moisture Sensitivity Level(MSL)3 级(开封后 168 小时内焊接,峰值回流温度 260°C):

| 订购型号 | 封装类型 | 引脚数 | RoHS 合规 | 焊球材质 | 包装方式 |

|---|---|---|---|---|---|

| ADC12DJ5200SE | FCBGA | 144 | 是 | SnAgCu | JEDEC 托盘(90 片 / 盘) |

| ADC12DJ5200SE | FCBGA | 144 | 否 | SnPb | JEDEC 托盘(90 片 / 盘) |

六、应用场景与设计建议

1. 典型应用

- 通信测试设备 :如 802.11ad、5G 信号发生器 / 分析仪,利用宽频带与高采样率实现多标准信号采集与分析;

- 电子战(EW) :包括信号情报(SIGINT)、电子情报(ELINT),通过高动态范围与快速频率跳变,截获并分析复杂射频信号;

- 卫星通信(SATCOM) :直接采样卫星下行射频信号,减少中频转换环节的信号损耗;

- 软件定义无线电(SDR) :作为 RF 前端核心,支持灵活的频段配置与信号处理,适配多制式通信需求。

2. 设计建议

- 电源设计 :模拟电源(VA11/VA19)与数字电源(VD11)需分开布线,每组电源就近并联 0.1μF 陶瓷电容 + 10μF 钽电容去耦;模拟地(AGND)与数字地(DGND)单点连接,避免串扰。

- 输入与时钟 :模拟输入建议差分布线,串 22Ω 电阻 + 并 2.2nF 电容构成抗混叠滤波;采样时钟(CLK±)需低抖动(建议 < 1ps RMS),AC 耦合以保证最佳共模电压,SYSREF 信号需与 CLK± 时序匹配,可通过自动校准优化同步精度。

- PCB 布局 :采用四层板(内电层为地与电源),射频信号与高速 SerDes 信号分开布线,阻抗控制为 50Ω(射频)与 100Ω(差分 SerDes);热焊盘需大面积连接至接地平面,必要时增加散热过孔。

七、寄存器与编程

1. 核心寄存器(地址与功能)

ADC12DJ5200SE 通过 SPI 接口配置,关键寄存器如下表,覆盖模式控制、信号处理、同步与校准等核心功能:

| 地址 | 寄存器名称 | 核心功能 |

|---|---|---|

| 0x200 | JESD_EN | JESD204C 接口使能(0 = 禁用,1 = 使能),禁用时串行器断电以节能 |

| 0x201 | JMODE | 工作模式选择(如单 / 双通道、编码方式、抽取率,共 71 种预设模式) |

| 0x202 | KM1 | JESD204C 多帧长度配置(K 值 = KM1+1,8B/10B 模式有效) |

| 0x210 | DDC_CFG | DDC 使能与抽取率控制(4x/8x/16x/32x) |

| 0x211-0x212 | OVR_T0/OVR_T1 | 过 range 阈值设置(监测 ADC 信号是否接近饱和,触发保护或增益调整) |

| 0x220-0x25C | FREQA0-PhaseB3 | NCO 频率与相位配置(每路 DDC4 个 NCO,支持频率跳变与相位同步) |

| 0x61 | CAL_EN | 校准使能(0 = 校准复位,1 = 启动校准),需在 JESD_EN 使能前配置 |

| 0x62 | CAL_CFG0 | 校准模式选择(Foreground/Background 校准、偏移校准使能) |

2. SPI 通信协议

- 帧结构 :每次寄存器访问为 24 位帧,含 1 位读写控制(1 = 读,0 = 写)、15 位寄存器地址、8 位数据;支持 流模式 (SCS 保持低电平),地址自动递增 / 递减,加快多寄存器配置效率。

- 操作注意事项 :校准过程中禁止访问 SPI 寄存器,避免校准数据 corruption;修改 JMODE、DDC 参数等关键配置前,需先禁用 JESD204C 接口(JESD_EN=0),配置完成后重新使能。

-

ADC12DJ5200RF 具有双通道 5.2 GSPS 或单通道 10.4 GSPS 的射频采样 12 位 ADC技术手册2025-11-01 1472

-

ADC08DJ5200RF RF采样8位ADC技术手册2025-10-31 707

-

ADC12DJ5200-SP 射频采样模数转换器(ADC)技术文档总结2025-10-29 823

-

ADC12DJ5200-SEP 产品技术总结2025-10-28 1304

-

Texas Instruments ADC08DJ5200RF 8位模数转换器数据手册2025-10-06 1639

-

ADC12DJ5200SE 10.4GSPS单通道或5.2GSPS双通道12位射频采样模数转换器(ADC)数据表2024-07-22 638

-

ADC08DJ5200RF射频采样千兆采样模数转换器(ADC)数据表2024-07-19 504

-

ADC12DJ5200-EP射频采样千兆采样模数转换器(ADC)数据表2024-07-15 536

-

ADC12DJ3200AAV 射频采样模数转换器 TI品牌 特性与应用2023-06-16 4857

全部0条评论

快来发表一下你的评论吧 !