STMicroelectronics AIS25BA MEMS运动传感器深度解析与应用指南

描述

STMicroelectronics AIS25BA MEMS数字输出运动传感器是一款超低噪声、低延迟、高带宽、三轴数字加速度计,设有专用时分多路复用 (TDM) 接口。AIS25BA设计用于满足汽车非安全应用的需求,例如宽带有源噪声控制 (ANC) 和振动监测。AIS25BA具有用户可选的±3.85g至±7.7g满量程范围、传感器数据用TDM接口以及器件配置用I^2^C接口。

数据手册;*附件:STMicroelectronics AIS25BA MEMS数字输出运动传感器数据手册.pdf

STMicroelectronics AIS25BA MEMS数字输出运动传感器采用紧凑型焊盘栅格阵列 (LGA) 封装,可确保在-40°C至+125°C扩展温度范围内工作。该器件符合AEC-Q100汽车应用类标准。

特性

- 符合AEC-Q100标准

- 电源电压:1.71V至2.1V

- 3轴加速度计,具有用户可选的满量程:±3.85g、±7.7g

- 宽扁平直流至2.4kHz频率响应

- 低延迟:266µs(整个读卡链)(2kHz时)

- 超低噪声密度,X轴和Y轴为30µg/√Hz;Z轴为50µg/Hz

- 用于传感器数据的TDM(8kHz、16kHz、24kHz)从接口和用于配置的I^2^C 接口

- 扩展温度范围:-40°C至+125°C

- 内置自检功能

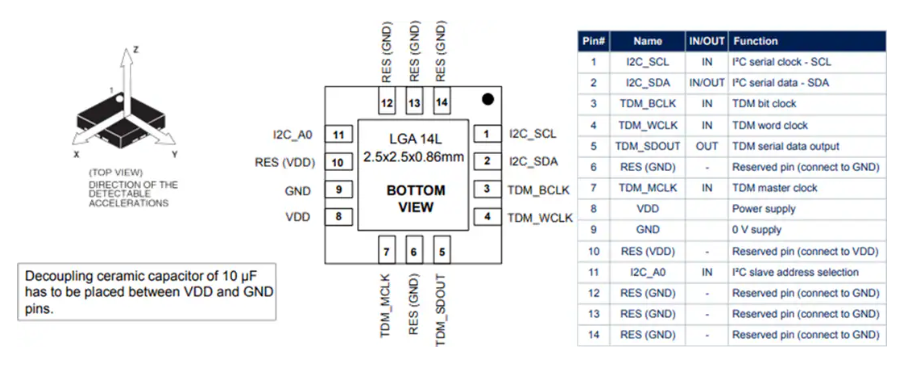

- 2.5mm x 2.5mm x 0.86 mm LGA-14封装

- 高冲击耐受性:10000g

- 无铅、ECOPACK,符合RoHS指令

引脚分配

STMicroelectronics AIS25BA MEMS运动传感器深度解析与应用指南

摘要

AIS25BA是STMicroelectronics推出的汽车级超低噪声3轴数字加速度计,集成了专用TDM接口和I²C配置接口。本文基于数据手册详细解析其关键特性、电气参数、接口协议及实际应用要点。

一、核心特性与产品定位

1.1 突出特性

- 超低噪声密度:X/Y轴典型值30 μg/√Hz,Z轴50 μg/√Hz,适用于高精度振动监测。

- 宽带宽与低延迟:频率响应从直流至2.4 kHz(典型值),全链路延迟仅266 μs @ 2 kHz

- 双接口设计:TDM接口传输传感器数据(支持8/16/24 kHz),I²C接口用于设备配置

- 高鲁棒性:AEC-Q100认证,10000g冲击耐受能力,扩展工作温度范围-40°C至+125°C

1.2 应用场景

- 宽带主动噪声控制:利用宽频带特性实现实时噪声抵消

- 振动监测系统:适用于工业设备状态监控与预测性维护

1.3 物理规格

- 封装:LGA-14 (2.5×2.5×0.86 mm³),符合ECOPACK®环保标准

- 供电范围:1.71 V至2.1 V(典型1.8 V)

二、电气与机械参数深度解析

2.1 关键机械特性

| 参数 | 条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| 测量范围 | 全选择±3.85g / ±7.7g | - | 3.85 / 7.7 | - | g |

| 灵敏度 | @ ±3.85g | - | 0.122 | - | mg/LSB |

| 零g偏移精度 | @ 25°C | -180 | - | +180 | mg |

| 噪声密度 | X/Y轴@2.4kHz | - | 30 | - | μg/√Hz |

| 谐振频率 | MEMS元件 | 5150 | - | - | Hz |

设计要点:

- 灵敏度温度系数(TCSo)仅±0.015 %/°C,保证温漂稳定性

- 非线性度<0.5 %FS,确保高线性输出

2.2 电气特性与功耗管理

| 模式 | 供电电压 | 电流消耗 | 温度范围 |

|---|---|---|---|

| 正常工作 | 1.71-2.1 V | 5.0 mA(三轴使能) | -40至+125 °C |

| 功耗下降 | - | 1 μA | - |

接口特性:

- 输出数据率:支持8/16/24 kHz TDM采样率

- 数字电平:高电平输入>0.7×Vdd,低电平输出<0.2 V

三、TDM接口技术详解

3.1 接口架构

- 时钟信号:BCLK(位时钟)、WCLK(字时钟)、MCLK(主时钟)

- 数据流:SDOUT串行数据输出,支持左对齐16位数据格式

3.2 帧同步机制

- WCLK功能:标识帧起始,支持50%占空比、单时隙宽度或单BCLK宽度

- 采样率配置:

- 手动模式:通过TDM_CTRL_REG(2Eh)寄存器配置

- 自动模式:启用ODR_AUTO_EN,根据MCLK/WCLK比率自动选择8/16/24 kHz

3.3 时隙映射灵活性

支持两种配置模式:

- X/Y/Z轴映射至SLOT0/1/2

- X/Y/Z轴映射至SLOT4/5/6

3.4 四大配置模式

- 配置1:无延迟,数据在BCLK上升沿有效

- 配置2:无延迟,数据在BCLK下降沿有效

- 配置3:延迟一个BCLK周期,上升沿有效

- 配置4:延迟一个BCLK周期,下降沿有效

3.5 时钟同步要求

- BCLK和WCLK必须通过MCLK整数分频获得

- BCLK/WCLK比率必须为整数值,确保ADC与TDM数据率完全同步

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

基于STEVAL-MKI226KA加速度计套件的数据手册技术解析与应用指南2025-10-28 2774

-

STMicroelectronics X-NUCLEO-IKS4A1 运动与环境传感器评估板技术解析2025-10-23 670

-

ROHM(罗姆)传感器_MEMS选型指南2025-04-01 393

-

LIS25BA运动传感器的相关资料2023-09-06 566

-

不同类型MEMS传感器的比较 MEMS传感器的工作原理2023-06-13 10262

-

台信红外标签传感器SBL-R48C-25BA2021-09-05 734

-

MEMS运动传感器原理2020-10-19 6884

-

装配MEMS惯性传感器的实用方法2018-11-12 1991

-

基于ST的MEMS传感器的个人电脑和媒体遥控器空中运动控制2018-10-25 1851

-

基于MEMS传感器小型化的设计指南2017-09-18 986

-

汽车电子MEMS传感器的应用2016-12-07 5339

-

中国传动网:全景扫描MEMS运动传感器2014-04-25 2338

-

ST推出汽车智能电子系统运动传感器AIS226DS2009-11-04 1367

-

AIS326DQ 汽车质量级三轴MEMS加速度传感器2008-10-28 1510

全部0条评论

快来发表一下你的评论吧 !