AFE881H1 低功耗数模转换器(DAC)技术文档总结

描述

16 位 AFE881H1 和 14 位 AFE781H1 (AFEx81H1) 是高度集成、高精度、极低功耗的数模转换器 (DAC),其电压输出专为支持 HART 的传感器-发射器应用而设计。

AFEx81H1 器件包括设计 4 mA 至 20 mA、2 线(环路供电)传感器发射器所需的大部分组件。除了高精度DAC外,这些器件还包括HART认证的FSK调制解调器、10 ppm/°C基准电压源和诊断模数转换器(ADC)。为了满足本质和功能安全问题,需要外部电压到电流转换和功率调节。

*附件:afe881h1.pdf

内部诊断ADC复用到多个内部节点,从而实现自动自我健康检查。如果从诊断ADC、CRC帧错误检查或窗口看门狗定时器检测到任何故障,器件可以选择发出中断,进入与标准NAMUR输出值或用户指定的自定义值相对应的故障安全状态,或两者兼而有之。

这些器件采用低至 1.71 V 的电源供电,最大静态电流为 220 μA。这些器件的额定温度范围为–40°C至+125°C,但工作温度范围为–55°C至+125°C。

特性

- 低静态电流:180 μA(典型值)

- 符合 HART 标准的物理层调制解调器

- 16位或14位单调高性能DAC

- 1.8V 电源:0.15 V 至 1.25 V、0.2 V 至 1.0 V

- 5V 电源:0.3 V 至 2.5 V、0.4 V 至 2.0 V

- 16 位时的 4-LSB INL

- 0.07% FSR(最大)TUE,–40°C 至 +125°C

- 用于高级诊断的 12 位 3.84kSPS ADC

- 集成 1.25V 基准电压源,电流为10 ppm/°C(最大值)

- 内部1.2288MHz振荡器,带时钟输出

- 数字接口

- 串行外设接口 (SPI):DAC 和 HART 的共享总线

- 通用异步接收-发射器 (UART):DAC 和 HART 的共享总线

- 两者:用于 DAC 的 SPI 和用于 HART 的 UART

- 故障检测:CRC位错误检查、窗口看门狗定时器、诊断ADC

- 数字DAC压摆率控制

- 宽工作温度:–55°C 至 +125°C

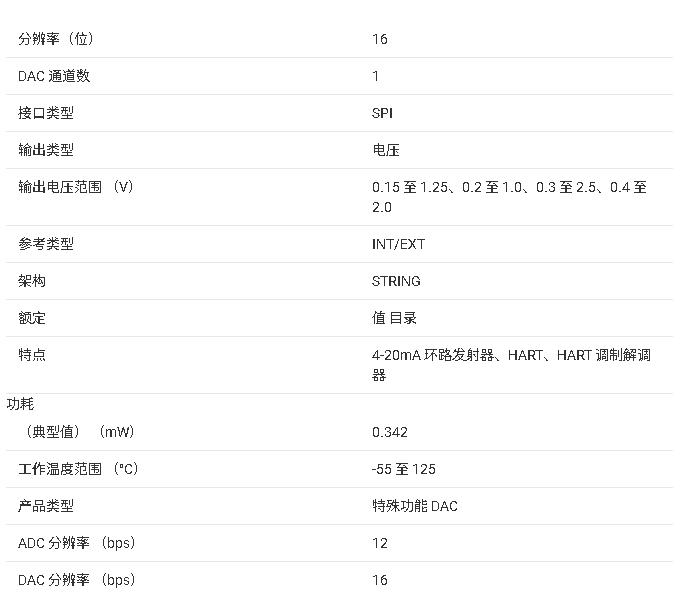

参数

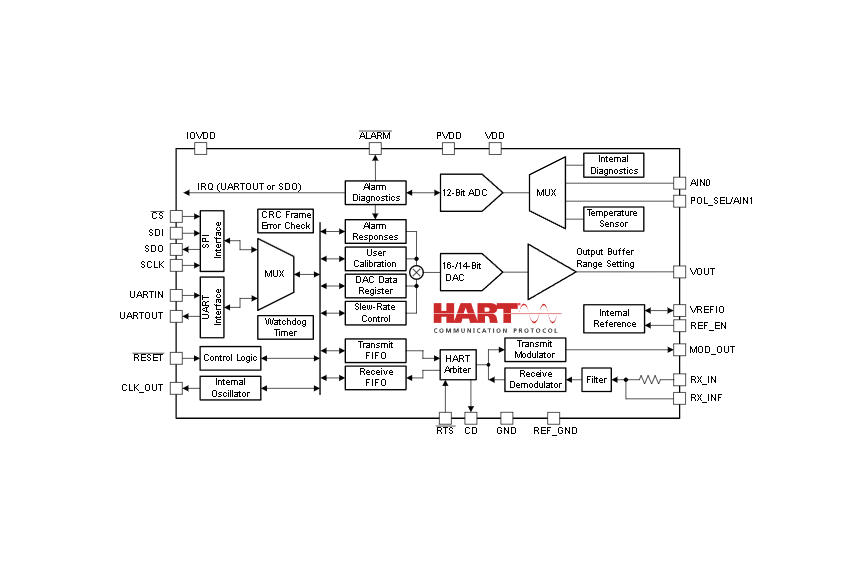

方框图

一、产品概述

AFE781H1(14 位)与 AFE881H1(16 位)是专为回路供电系统设计的低功耗 DAC,采用 4mm×4mm 24 引脚 UQFN(RRU 封装),工作温度覆盖 - 55°C125°C,典型静态电流仅 180μA,支持 1.71V5.5V 宽电源范围(PVDD)。器件集成 HART® 物理层调制解调器、12 位诊断 ADC、1.25V 高精度电压基准(温漂最大 10ppm/°C)及 1.2288MHz 内部振荡器,可减少外部元器件数量,适配工业自动化、智能传感器变送器等场景,满足功能安全系统设计需求(提供配套安全文档)。

二、核心特性

1. 高精度 DAC 性能

(1)静态与动态指标

- 分辨率与线性度 :AFE881H1 为 16 位单调 DAC,积分非线性(INL)最大 ±4LSB;AFE781H1 为 14 位,INL 最大 ±2LSB;两者总未调整误差(TUE)在 - 40°C~125°C 范围内最大 0.07% FSR,确保全温域精度。

- 输出范围 :支持多档电压输出,适配不同电源场景:

- 1.8V 供电(PVDD=1.71V

1.89V):0.15V1.25V(全量程)、0.2V~1.0V(窄量程); - 5V 供电(PVDD=2.7V

5.5V):0.3V2.5V(全量程)、0.4V~2.0V(窄量程);

- 1.8V 供电(PVDD=1.71V

- 动态性能 (典型值,TA=25°C):

- 输出噪声(0.1Hz~10Hz):0.25LSBpp;噪声谱密度(1kHz):180nV/√Hz(1.8V 供电);

- 建立时间:65μs(1/4~3/4 量程,±2LSB 精度);压摆率:30mV/μs;

- 电源抑制比(AC):85dB(50Hz~60Hz 纹波),抗电源噪声能力强。

(2)灵活的输出控制

- 数字步进衰减器(DSA) :无额外 DSA 硬件需求,通过 DAC 增益 / 偏移校准实现输出功率调节,支持线性 / 正弦波可编程摆率控制(步长 1

128 码,时钟速率 2400Hz307.2kHz),避免输出电压突变。 - 故障安全输出 :支持 NAMUR 标准故障输出(如低电平 0.15V/0.3V、高电平 1.25V/2.5V)或用户自定义值,可通过引脚或寄存器配置报警电压极性。

2. 集成 HART® 调制解调器

- 物理层合规 :符合 HART® FSK 协议,支持 1200Hz(标记)/2200Hz(空格)频率偏移,接收灵敏度 80

120mVpp,发射输出电压 400800mVpp(160Ω 负载),频率误差 ±1%(-40°C~125°C)。 - 数据传输 :内置 32×9 位收发 FIFO 缓冲区,支持半双工 / 全双工模式(全双工用于自测试),通过 RTS/CD 引脚实现总线仲裁,避免数据冲突;支持 SPI 或 UART 接口与主机通信,UART 支持 9600/1200 波特率。

3. 诊断与功能安全

(1)12 位诊断 ADC

- 监测能力 :支持 2 路外部模拟输入(AIN0/AIN1,0V~1.25V/2.5V 范围)与 5 路内部节点监测(VREF、PVDD、VDD、ZTAT 电压、DAC 输出 VOUT),转换速率 3.84kSPS,噪声最大 ±4LSB。

- 故障检测 :可配置上下阈值与滞回(0

127LSB),连续 N 次(18 次,可编程)超阈值触发报警,支持温度监测(内置温度传感器,精度 ±5°C),85°C 触发警告、130°C 触发错误。

(2)安全机制

- 故障响应 :支持 CRC 帧错误检测、窗口看门狗定时器(WDT,1200Hz 时钟,超时范围 53ms~5.12s)、OTP 存储器 CRC 校验,故障时可触发中断(ALARM 引脚)、DAC 进入清零状态或高阻模式。

- 功能安全支持 :提供功能安全设计文档,可用于满足 IEC 61508 等标准的安全相关系统,支持故障注入测试(FORCE_FAIL 寄存器)。

4. 低功耗与宽温稳定性

- 功耗优化 :典型静态电流 180μA(PVDD=1.8V,DAC 零刻度),HART® 调制解调器工作电流仅 10μA,ADC 转换电流 10μA,适配回路供电系统低功耗需求;

- 电压基准 :集成 1.25V 基准,初始精度 ±0.16%(25°C),温漂最大 10ppm/°C,输出噪声(0.1Hz~10Hz)7.5μVpp,支持外部基准输入(VREFIO 引脚)。

三、功能架构与工作原理

1. 核心架构

器件采用 “数字控制 - 模拟转换 - 诊断监测” 三段式架构,关键模块如下:

- 数字控制层 :含 SPI/UART 接口(支持 CRC 错误检测)、寄存器配置单元、看门狗定时器、HART® 仲裁器与 FIFO 缓冲区,负责数据收发与系统控制;

- 模拟转换层 :16/14 位电阻串 DAC、输出缓冲放大器、可编程摆率控制器,实现数字信号到模拟电压的转换,支持增益(0.5~1.499985)与偏移(2’s 补码)校准;

- 诊断监测层 :12 位 SAR ADC、模拟多路选择器(MUX)、温度传感器、电压基准,监测内部电源、基准、DAC 输出及外部信号,异常时触发报警。

2. 关键工作模式

- 正常模式 :DAC 根据输入代码输出对应电压,HART® 调制解调器可并行传输数据(FSK 信号叠加于 4mA-20mA 电流回路);

- 清零模式 :通过引脚(CLR_PIN)、寄存器(DAC_CFG.CLR)或报警触发,DAC 输出预设清零代码(DAC_CLR_CODE),范围由 DAC_CFG.CLR_RANGE 配置;

- 低功耗模式 :DAC 输出缓冲器断电(DAC_CFG.PD=1),VOUT 进入高阻状态,静态电流降至最小;

- 自测试模式 :HART® 支持内部全双工(MOD_OUT 内部短接至 RX_INF)或外部全双工(外部短接),验证收发链路;存储器内置自测试(MBIST)检测 FIFO SRAM 有效性。

四、电气特性

1. 电源与电流特性

| 电源参数 | 测试条件 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| PVDD 电流(I_PVDD) | 1.8V 供电,DAC 零刻度,ADC 静态 | 180 | 220 | μA |

| 5V 供电,DAC 零刻度,ADC 静态 | 32 | 45 | μA | |

| VDD 电流(I_VDD) | 1.8V 供电,内部基准使能 | 140 | 170 | μA |

| 基准电流(I_REFIO) | 内部基准使能,无负载 | 52 | 70 | μA |

| HART® 电流(I_HART) | 调制解调器工作 | 10 | - | μA |

2. HART® 调制解调器特性

| 参数 | 测试条件 | 典型值 | 单位 |

|---|---|---|---|

| 接收灵敏度 | 内部滤波器,1200Hz 载波 | 100 | mVpp |

| 发射输出电压 | 160Ω 负载,AC 耦合 | 500 | mVpp |

| 载波检测时间 | 1200Hz 载波输入至 CD 引脚断言 | 3 | 波特 |

| 频率误差 | -40°C~125°C | ±1 | % |

3. 诊断 ADC 特性

| 参数 | 测试条件 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| 分辨率 | - | 12 | - | 位 |

| 积分非线性(INL) | 全量程 | ±1 | ±4 | LSB |

| 偏移误差(OE) | 校准后 | ±1.6 | ±10 | LSB |

| 转换速率 | - | 3.84 | - | kSPS |

| 输入电容 | AIN0/AIN1 引脚 | 6 | - | pF |

五、引脚配置与封装

1. 封装规格

- 物理参数 :4mm×4mm UQFN(RRU 封装),24 引脚,引脚间距 0.8mm,最大高度 0.7mm;底部裸露热焊盘需焊接至 AGND,配合散热过孔优化热性能(结到环境热阻 RθJA=103.1°C/W);

- 可靠性 :符合无铅焊接要求,MSL 等级 2(260°C 峰值回流焊,开封后 1 年存储),引脚镀层为镍钯金(NIPDAU),ESD 防护:人体放电模型(HBM)±2000V,带电器件模型(CDM)±500V。

2. 关键引脚分类

核心引脚按功能分为电源、模拟输入输出、数字控制、HART® 接口四类,关键引脚功能如下:

| 引脚类型 | 关键引脚示例 | 功能描述 |

|---|---|---|

| 电源引脚 | PVDD(17)、VDD(13)、IOVDD(12) | PVDD 为主电源(1.71V |

| 模拟输入输出 | AIN0(15)、AIN1/POL_SEL(16)、VOUT(18) | AIN0/AIN1 为诊断 ADC 输入,POL_SEL 可切换为 ADC 输入或报警电压极性控制;VOUT 为 DAC 输出电压 |

| 数字控制引脚 | CS(10)、SDI(8)、SDO(9)、SCLK(7) | SPI 接口,支持 12.5MHz 时钟速率,SDO 可配置为 IRQ 输出;RESET(6)为硬件复位引脚(低有效) |

| HART® 接口引脚 | RX_IN(21)、RX_INF(22)、MOD_OUT(23)、CD(3)、RTS(4) | RX_IN/RX_INF 为 HART® FSK 输入(RX_INF 适配外部滤波器),MOD_OUT 为 FSK 输出,CD 为载波检测,RTS 为收发控制 |

| 基准引脚 | VREFIO(19)、REF_EN(5)、REF_GND(20) | VREFIO 为基准输入 / 输出(内部基准使能时输出 1.25V),REF_EN 控制基准使能,REF_GND 为基准地 |

六、典型应用与设计建议

1. 典型应用场景

- 4mA-20mA 回路变送器 :DAC 输出电压经电压 - 电流(V-I)转换器(如 OPA333 运放 + NPN 三极管)转换为 4mA-20mA 电流,HART® 信号叠加于电流回路实现双向通信,适配工业过程控制中的温度、压力传感器变送;

- 智能传感器节点 :集成诊断 ADC 监测传感器信号与电源状态,看门狗与 CRC 确保数据可靠性,低功耗特性适配电池或回路供电的远程传感器。

2. 设计建议

(1)电源与基准设计

- 电源 decoupling :PVDD、VDD、IOVDD 引脚就近并 100nF 陶瓷电容 + 1μF 钽电容,VREFIO 引脚并 70nF~130nF 电容(确保基准稳定);

- 宽电压适配 :PVDD<2.7V 时,需将 PVDD 与 VDD 短接,禁用内部 LDO;PVDD≥2.7V 时,内部 LDO 自动生成 1.8V VDD,VDD 引脚需并 1μF~10μF 电容。

(2)HART® 接口设计

- 信号耦合 :RX_IN 引脚通过 2.2μF 电容 AC 耦合 HART® 信号,RX_INF 引脚接 680pF 电容(内部滤波器模式);MOD_OUT 输出通过 1000pF 电容耦合至电流回路,避免直流偏移;

- 总线仲裁 :半双工模式下,通过 RTS 引脚(低电平发射、高电平接收)或 MODEM_CFG.RTS 寄存器控制收发,CD 引脚监测载波存在,避免总线冲突。

(3)PCB 布局

- 分区布局 :模拟区(VOUT、AIN0/AIN1、VREFIO)与数字区(SPI、HART®)严格分离,AGND 与 DGND 单点连接,避免地弹噪声;

- 热设计 :裸露热焊盘与 AGND 平面大面积连接,添加 4~6 个 0.3mm 散热过孔,确保结温不超过 125°C(上限);

- EMC 优化 :时钟信号(CLK_OUT)远离模拟引脚,HART® 信号路径最短,关键模拟引脚添加 RC 滤波(如 AIN0 串 1kΩ 电阻 + 10nF 电容)。

-

AFE781H1技术文档总结2025-10-27 721

-

AFE881H1评估模块技术解析与应用指南2025-09-12 1220

-

Texas Instruments AFEx81H1低功耗数模转换器数据手册2025-08-03 1388

-

AFE881H1评估模块2024-10-30 410

-

使用AFE881H1的超低功耗、低压、2线、4-20mA环路变送器2024-09-06 551

-

DAC5311低功耗、单通道、电压输出数模转换器(DAC)数据表2024-07-30 730

-

DAC60096低功耗12位数模转换器(DAC)数据表2024-07-29 529

-

AFE78201,AFE88201低功耗的数模转换器(DAC)数据表2024-07-15 433

-

DAC34H84低功耗、高动态四通道、16位数模转换器(DAC)数据表2024-06-20 557

-

介绍DAC数模转换器以及DMA的使用2021-08-12 3722

-

数模转换器是什么2021-07-26 3319

-

DAC1122:低功耗、高性能、数模转换器过时数据表2021-05-27 969

-

求一种低功耗数模转换器AD7846的设计方案2021-04-23 1639

全部0条评论

快来发表一下你的评论吧 !