浅谈DDR的逻辑电平标准

描述

来源:群星结局

总所周知,一般我们在对通信芯片互连的时候,要求两者的IO接口电平标准是一样的,而在学习FPGA与DDR互连的时候,查看网上的资料却很少提及这方面,都是直接教你怎么连接,不明所以,所以这里简单做了下笔记。

SSTL逻辑电平

SSTL逻辑电平一般用在DDR SDRAM存储接口上,与DRAM标准协议有关:

SSTL_25 IO标准适用于DDR SDRAM存储接口(2.5V);

SSTL_18 IO标准适用于DDR2 SDRAM存储接口(1.8V);

SSTL_15 IO标准适用于DDR3 SDRAM存储接口(1.5V);

SSTL_135 IO标准适用于DDR3L SDRAM存储接口(1.35V);

SSTL_12 IO标准适用于DDR4 SDRAM存储接口(1.2V);

一般CPU的IO和DDR都会默认兼容SSTL逻辑电平,所以不需要逻辑电平转换。

SSTL电路结构

常见的LVTTL(Low-Voltage TTL)是由TTL发展而来,TTL一般指的是5V逻辑电平,LVTTL则小于3.6V。CMOS和LVCMOS电平同理。

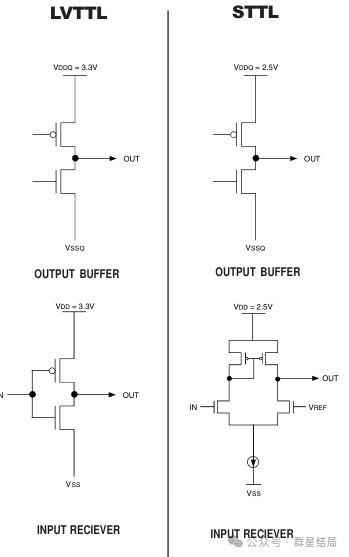

LVTTL和SSTL电路结构如下:

LVTTL的输入和输出都采用CMOS逆变器结构,由一对增强型NMOS和PMOS组成,结构简单,但是由于这种结构在工艺、温度上匹配较差,所以开启阈值电压较大,进而保证可靠的开关。

SSTL的输出端和LVTTL类似,最大不同是输入端采用差分电路,输入信号与Vref参考电压比较,使得在输入电压波动小的情况下也能实现较大的输出,再给到后面的电路。

SSTL_15

这里以DDR3使用的SSTL_15为例,Xilinx的7系列FPGA的IO支持各种电平标准,其中就包括DDR3的SSTL_15,SSTL_15又分为SSTL_15和SSTL_15_R,区别在于驱动电流大小。

| SSTL_15 | SSTL_15_R | |

|---|---|---|

| Available I/O Bank Type | HR、HP | HR |

| Drive strength | full-strength | weaker-strength |

对于单片DDR3,使用SSTL_15_R有助于减小信号过冲和提高信号完整性,多片DDR3还是建议使用SSTL_15。

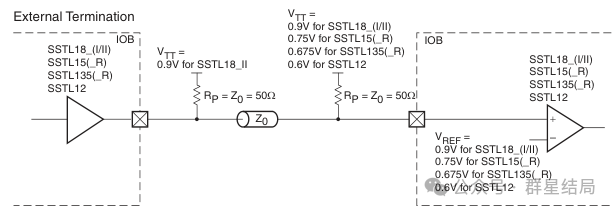

端接要求

对于HR BANK上的单端单向信号,因为内部没有DCI功能(数字阻抗控制功能,DCI可以控制输出驱动阻抗或者添加并行端接在驱动器或者接收器,精确匹配传输线阻抗,保证信号传输完整性,只有HP有这个功能),需要使用外部并联端接匹配。对于SSTL_15,只需要在接收端加上拉电阻。

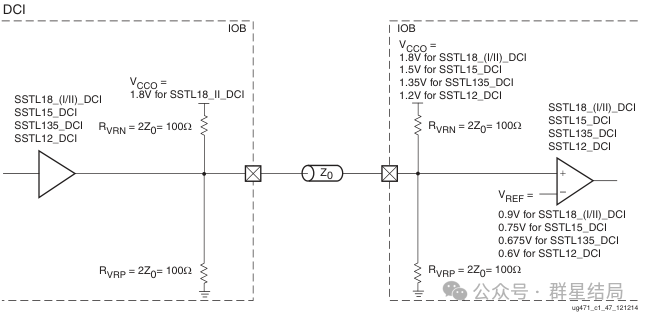

对于HP BANK上的单端单向信号,因为内部有DCI功能,不需要使用外部并联终端匹配。

以上是单端单向信号,对应DDR3上就是地址总线、命令和控制线。

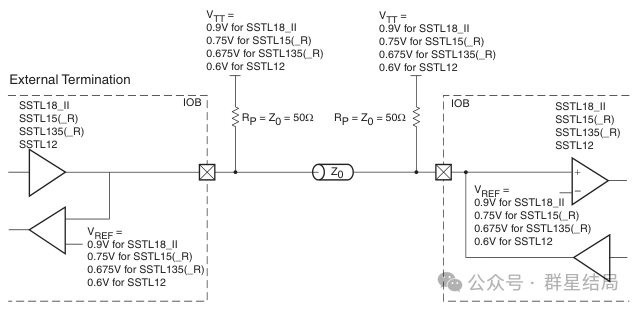

同理,对于HR BANK上单端双向信号,需要在两端都加上并联端接:

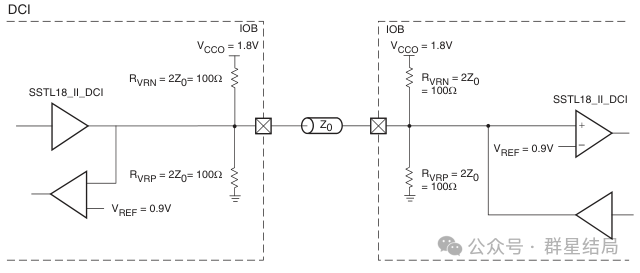

对于HP BANK上单端双向信号:

以上是单端双向信号,对应DDR3上就是数据总线。

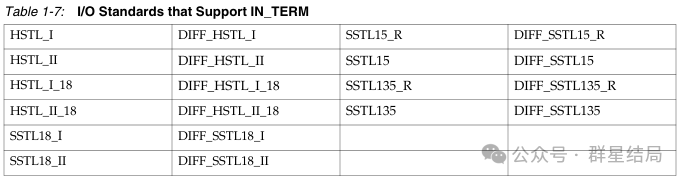

对于常见的A7系列,因为基本上都是HR BANK,所以没有DCI功能,那么为什么大部分原理图,DDR3的数据总线都没有在FPGA一侧增加并联端接呢?这是因为HR BANK为IO增加了可选的IN_TERM属性,可以为IO增加戴维南等效并联端接,该选项的目标等效电阻值可以为40Ω、50Ω和60Ω;缺点是不能进行校准,会受到温度和电压变化的影响,而DCI就能校准外部电阻,克服这些问题。

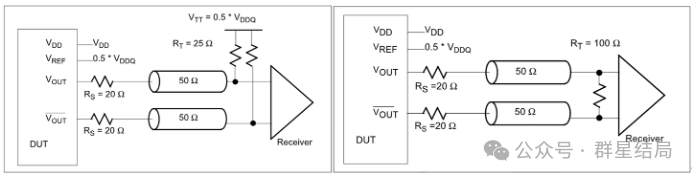

对于HR BANK上差分单向信号,有两种端接方式,一种是在各自单端线路上加并联端接,另一种是在差分线路之间加并联端接:

对于HP BANK上差分单向信号则可以使用DCI功能。

以上差分单向信号就对应DDR3的时钟线。

-

TTL电平标准的介绍与解析2025-01-16 4194

-

逻辑电平输出是什么意思2024-09-20 2677

-

逻辑电平--差分信号(PECL、LVDS、CML)电平匹配2022-11-10 18212

-

信号逻辑电平的标准详细说明2021-01-08 1822

-

信号逻辑电平标准的详细说明2021-01-05 1926

-

信号逻辑电平标准详解2018-03-10 14249

-

逻辑电平设计规范2017-01-22 993

-

快点PCB原创∣详解信号逻辑电平标准2016-09-09 2991

-

DDR SRAM与HSTL电平标准2011-06-03 2615

-

什么是DDR传输标准2009-12-24 820

-

常见逻辑电平标准详细介绍2009-11-28 4139

-

逻辑电平转换说明2009-10-24 9182

-

DDR传输标准2009-04-26 2044

-

逻辑电平详细介绍2009-04-12 12189

全部0条评论

快来发表一下你的评论吧 !