DAC53001技术文档总结

描述

12位DAC63001和DAC63002以及10位DAC53001和DAC53002(统称为DACx300x)是一个引脚兼容的超低功耗、单通道和双通道、缓冲电压输出和电流输出智能数模转换器(DAC)系列。DACx300x 器件支持 Hi-Z 掉电模式和断电条件下的 Hi-Z 输出。DAC输出提供力检测选项,用作可编程比较器和电流吸收器。多功能 GPIO、功能生成和 NVM 使这些智能 DAC 能够实现无处理器应用和设计重用。这些设备会自动检测 I^2^C、PMBus 和 SPI 接口,并包含内部基准电压源。

这些智能DAC的功能集与微型封装和超低功耗相结合,是陆地移动无线电、脉搏血氧仪、笔记本电脑和其他电池供电应用等应用的绝佳选择,用于偏置、校准和波形生成。

*附件:dac53001.pdf

特性

- 具有灵活配置的可编程电压或电流输出:

- 电压输出:

- 1 LSB INL 和 DNL(10 位)

- 1 倍、1.5 倍、2 倍、3 倍和 4 倍的收益

- 电流输出:

- 1 LSB INL 和 DNL(8 位)

- 单极性和双极性输出范围选项,范围为 25 μA 至 250 μA

- 电压输出:

- 35μA/通道 I

DD在电压输出模式下 - 适用于所有通道的可编程比较器模式

- VDD关闭时的高阻抗输出

- 高阻抗和电阻下拉掉电模式

- 50MHz SPI 兼容接口

- 自动检测 I^2^C、PMBus™ 或 SPI 接口

- 1.62伏伏

IH的带 VDD= 5.5 伏

- 1.62伏伏

- 通用输入/输出 (GPIO) 可配置为多种功能

- 预定义波形生成:正弦波、余弦波、三角波、锯齿波

- 用户可编程非易失性存储器 (NVM)

- 内部、外部或电源作为参考

- 工作范围广:

- 电源:1.8 V 至 5.5 V

- 温度:–40°C 至 +125°C

- 微型封装:16引脚WQFN(3 mm × 3 mm)

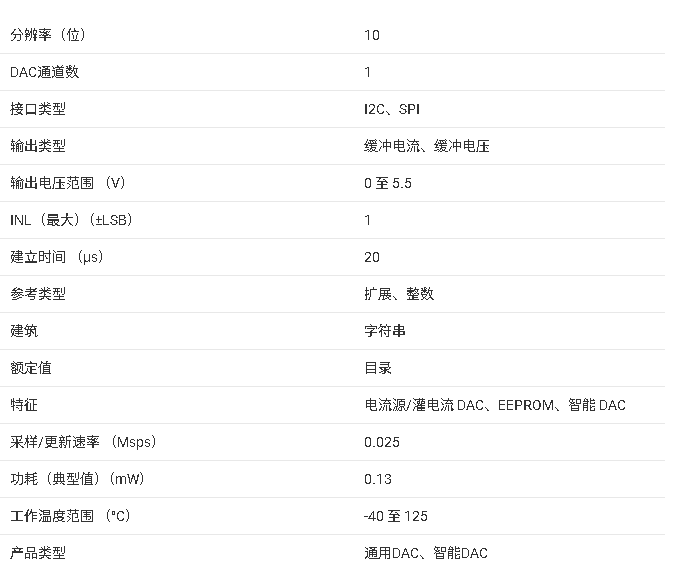

参数

方框图

一、产品概述

DACx300x 是引脚兼容的超低功耗智能 DAC 家族,包含 4 个型号,核心差异体现在分辨率与通道数,均采用 3mm×3mm 16 引脚 WQFN(RTE 封装),工作温度覆盖 - 40°C~125°C,结温上限 150°C。器件集成非易失性存储器(NVM)、内部基准源及自动检测的 I²C/SPI/PMBus 接口,支持断电高阻输出、可编程比较器模式及波形生成,单通道电压输出模式功耗低至 35μA,适配空间受限、低功耗要求高的场景。

| 型号 | 分辨率 | 通道数 | 核心特点 |

|---|---|---|---|

| DAC53001 | 10 位 | 单通道 | 电压 / 电流输出,支持比较器模式 |

| DAC53002 | 10 位 | 双通道 | 双路独立配置,共享 NVM 与基准源 |

| DAC63001 | 12 位 | 单通道 | 更高线性度,适配高精度校准场景 |

| DAC63002 | 12 位 | 双通道 | 双路高精度输出,支持同步波形生成 |

二、核心特性

1. 高精度模拟输出性能

(1)电压输出模式

- 静态指标 (典型值,TA=25°C,VDD=5.5V):

- 线性度:10 位型号 INL/DNL±1LSB,12 位型号 INL±4LSB、DNL±1LSB;

- 增益 / 偏移误差:增益误差 ±0.5% FSR,偏移误差 ±0.75% FSR,温度系数分别为 ±0.0008% FSR/°C、±0.0003% FSR/°C;

- 满量程范围:支持 1x/1.5x/2x/3x/4x 增益(内部基准 1.21V 时,最大输出 4.84V),外部基准或电源作为基准时增益固定 1x,输出范围 0~VDD。

- 动态指标 :

- 建立时间:20μs(1/4~3/4 量程,settling 到 10% FSR),增益 4x 时 25μs;

- 噪声性能:0.1Hz~10Hz 频段噪声电压 50μVpp(1x 增益)、90μVpp(4x 增益),1kHz 噪声密度 0.35μV/√Hz(1x 增益);

- 电源抑制比(PSRR):DC 模式 0.25mV/V,AC 模式 - 68dB(50/60Hz 干扰)。

(2)电流输出模式

- 静态指标 (典型值,TA=25°C,输出范围 ±250μA):

- 分辨率:8 位(所有型号),INL/DNL±1LSB;

- 输出范围:支持单极性(0

25μA/50μA/125μA/250μA 及负向范围)、双极性(±25μA±250μA),偏移误差 ±1.5% FSR,增益误差 ±1.3% FSR; - 输出阻抗:60MΩ( midscale,负载电压 VDD/2),输出 compliance 电压≥400mV(除 25μA 范围为 200mV 外)。

- 动态指标 :

- 建立时间:60μs(1/4~3/4 量程,settling 到 1LSB);

- 噪声性能:0.1Hz~10Hz 频段噪声电流 150nApp,1kHz 噪声密度 1nA/√Hz。

2. 灵活的接口与控制功能

(1)自动检测多接口

- 接口类型 :上电后自动识别 I²C/SPI/PMBus,识别后锁定协议直至下一次上电;

- I²C:支持标准模式(100kbps)、快速模式(400kbps)、快速模式 +(1Mbps),A0 引脚可配置 4 个从机地址;

- SPI:默认 3 线模式(SCLK/SDI/SYNC),GPIO 可配置为 SDO 实现 4 线读回,写速率最高 50MHz,读速率最高 2.5MHz;

- PMBus:兼容电源管理命令(如 Turn On/Off、Margin High/Low),支持组命令与通信故障检测(CML 标志)。

- GPIO 多功能配置 :可配置为 LDAC(加载 DAC 数据)、PD(掉电控制)、RESET(硬件复位)、STATUS(状态输出)等,支持边缘 / 电平触发,实现无处理器场景下的输出控制。

(2)非易失性存储器(NVM)

- 存储内容 :用户可将寄存器配置(如输出模式、增益、掉电状态)写入 NVM,上电后自动加载,支持 20000 次擦写(-40°C~85°C)、1000 次擦写(125°C),数据 retention 50 年(25°C);

- 故障 Dump :触发故障时自动保存比较器状态、DAC 数据至 NVM,便于事后诊断,存储格式为 2 行 32 位数据(含状态位与 DAC 代码)。

3. 扩展功能模式

(1)可编程比较器模式

- 工作原理 :每个通道 FBx 引脚作为比较器输入,OUTx 引脚作为输出,支持推挽 / 开漏输出,可配置反相、滞回及窗口比较;

- 滞回模式:通过 DAC-X-MARGIN-HIGH/LOW 寄存器设置阈值,支持锁存比较器(复位需 RST-CMP-FLAG-X 位);

- 窗口模式:检测输入是否在两个阈值之间,输出结果可 latch 并映射到 GPIO,响应时间 10μs(10%~90% 输出)。

- 静态指标 :偏移误差 ±5mV(全温域),125°C 下 10 年漂移 4mV,输入电压范围 0~VDD(FBx 高阻禁用时)。

(2)波形生成

- 内置波形 :支持正弦波、三角波、锯齿波(含反向锯齿波),每通道独立配置;

- 正弦波:24 个预编程点 / 周期,频率由 SLEW-RATE 决定(如 SLEW-RATE=4μs / 步时,频率≈10.4kHz),支持 0°/90°/120°/240° 相位选择;

- 三角波 / 锯齿波:由 MARGIN-HIGH/LOW 设定幅值范围,频率由步长(1

32LSB)与步长时间(4μs5.1ms)决定,支持线性 / 对数斜率。

- PWM 生成 :三角波 / 锯齿波与 FBx 输入比较,可生成占空比可调的 PWM 信号,适配电机控制、LED 调光场景。

4. 低功耗与可靠性设计

- 功耗控制 :

- 正常模式:电压输出 35μA / 通道,电流输出 18μA / 通道(单极性 25μA 范围)、200μA / 通道(双极性 250μA 范围);

- 掉电模式:睡眠模式 28μA(内部基准关)、深度睡眠模式 3μA(仅 GPIO 唤醒),断电时输出高阻,漏电流≤500nA(VOUT≤5.5V)。

- ESD 防护 :人体放电模型(HBM)±2000V,带电器件模型(CDM)±500V,符合工业级防护标准;

- 电源序列 :VDD 支持 1.7V~5.5V 宽范围,外部基准需在 VDD 之后上电,避免反向电压损坏器件。

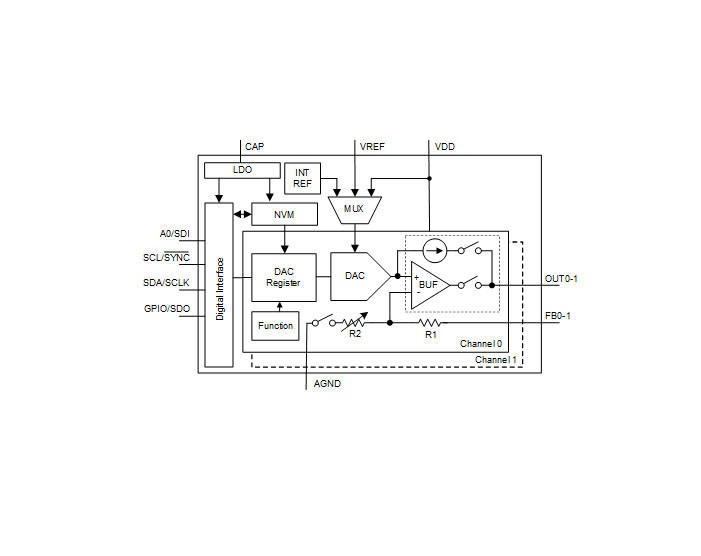

三、功能架构与工作原理

1. 核心架构

器件采用 “数字控制 - 模拟输出 - 扩展功能” 三层架构,关键模块如下:

- 数字控制层 :含 SPI/I²C/PMBus 接口处理、NVM 控制器、GPIO 状态机及寄存器映射,负责指令解析与配置存储;

- 模拟输出层 :每通道含 DAC 梯形网络、电压缓冲器(电压输出)/ 压流转换器(电流输出),支持内部(1.21V)、外部或电源作为基准;

- 扩展功能层 :集成比较器、波形生成器及掉电控制逻辑,比较器复用 FBx/OUTx 引脚,波形生成通过数字斜坡与 DAC 结合实现。

2. 关键工作模式

- 电压输出模式 :FBx 与 OUTx 短接构成闭环,选择基准与增益后,输出电压由 DAC 代码决定(如内部基准 1.21V、增益 4x 时,12 位满量程输出 4.84V);

- 电流输出模式 :FBx 悬空以最小化漏电流,输出电流由 8 位 DAC 代码与范围配置决定(如 ±250μA 范围时,代码 0 对应 - 250μA,255 对应 + 250μA);

- 比较器模式 :FBx 输入外部信号,与 DAC 设定阈值比较,OUTx 输出逻辑电平,支持滞回以抗干扰;

- 波形生成模式 :通过 FUNC-CONFIG-X 寄存器配置波形类型、步长与步长时间,DAC 自动更新代码生成连续波形。

四、电气特性

1. 电源与电流特性

| 电源参数 | 测试条件 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| VDD 电流(IDD) | 电压输出,全量程,数字引脚静态 | 35 | 50 | μA / 通道 |

| 电流输出,±25μA 范围,midscale | 18 | 24 | μA / 通道 | |

| 电流输出,±250μA 范围,满量程 | 167 | 200 | μA / 通道 | |

| 睡眠模式电流 | 内部基准关,外部基准 5.5V | - | 28 | μA |

| 深度睡眠模式电流 | GPIO 唤醒,所有模块关 | 1.5 | 3 | μA |

2. 基准与噪声特性

| 参数 | 测试条件 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|

| 内部基准初始精度 | TA=25°C | 1.212 | - | V |

| 内部基准温漂 | -40°C~125°C | - | 50 | ppm/°C |

| 外部基准输入阻抗 | VREF=5.5V | 192 | - | kΩ/ 通道 |

| 电压输出噪声(0.1Hz~10Hz) | 1x 增益,midscale | 50 | - | μVpp |

| 电流输出噪声(0.1Hz~10Hz) | ±250μA 范围,midscale | 150 | - | nApp |

3. 时序特性(SPI 写操作)

| 参数 | 测试条件 | 最小值 | 典型值 | 最大值 | 单位 |

|---|---|---|---|---|---|

| SCLK 频率 | 写模式 | - | - | 50 | MHz |

| SDI 建立时间(tSDIS) | 相对于 SCLK 下降沿 | 8 | - | - | ns |

| SDI 保持时间(tSDIH) | 相对于 SCLK 下降沿 | 8 | - | - | ns |

| SYNC 低电平时间 | 至少 24 个 SCLK 周期 | 50 | - | - | ns |

五、引脚配置与封装

1. 封装规格

- 物理参数 :3mm×3mm WQFN(RTE 封装),16 引脚,引脚间距 0.5mm,最大高度 0.8mm;底部裸露热焊盘(面积约 2mm×2mm)需焊接至 AGND,配合 2~4 个 0.3mm 散热过孔,结到环境热阻(RθJA)49°C/W,结到板热阻(RθJB)24.1°C/W;

- 可靠性 :符合无铅焊接要求,MSL 等级 1(260°C 峰值回流焊,无限期存储),引脚镀层为镍钯金(NIPDAU),兼容 RoHS。

2. 关键引脚分类

核心引脚按功能分为模拟输入输出、电源、数字控制及基准四类,关键引脚功能如下:

| 引脚类型 | 关键引脚示例 | 功能描述 |

|---|---|---|

| 模拟输入输出 | OUT0/OUT1(2/11)、FB0/FB1(1/12) | OUTx 为 DAC 模拟输出(电压 / 电流),FBx 为反馈 / 比较器输入(电压模式短接 OUTx,电流模式悬空) |

| 电源引脚 | VDD(15)、AGND(14)、CAP(13) | VDD 为主电源(1.7V~5.5V),AGND 为模拟地(热焊盘接 AGND),CAP 为内部 LDO 旁路电容(1.5μF) |

| 数字控制引脚 | SCL/SYNC(6)、SDA/SCLK(8)、A0/SDI(7)、GPIO/SDO(5) | SCL/SYNC 为 I²C 时钟 / SPI 片选,SDA/SCLK 为 I²C 数据 / SPI 时钟,A0/SDI 为 I²C 地址 / SPI 数据,GPIO/SDO 为多功能 GPIO/ SPI 读回 |

| 基准引脚 | VREF(16) | 外部基准输入(1.7V~VDD),未使用时需上拉至 VDD,配合 0.1μF 旁路电容 |

六、典型应用与设计建议

1. 典型应用场景

- 电源电压调节(Margining) :通过 DAC 输出控制 DC/DC 转换器反馈端,实现 ±10% 电压调节(如 3.3V 电源调节至 2.97V~3.63V),利用 Hi-Z 掉电模式避免电源扰动;

- 脉搏血氧仪 :电流输出模式提供 25μA~250μA 可编程激励电流,驱动 LED 光源,配合比较器检测光电流阈值;

- 波形发生器 :生成正弦波(如 10kHz)或三角波,作为测试设备激励信号,通过 NVM 保存波形参数,上电自动启动。

2. 设计建议

(1)电源与基准设计

- 电源 decoupling :VDD 引脚就近并 0.1μF 陶瓷电容(高频)+1μF 钽电容(低频),CAP 引脚并 1.5μF 陶瓷电容(推荐 X5R/X7R 材质),VREF 引脚并 0.1μF 电容(外部基准时);

- 基准选择 :高精度场景用内部基准(1.21V,温漂 50ppm/°C),宽输出范围场景用 VDD 作为基准(需保证 VDD 纹波≤10mV),外部基准需确保电压≤VDD 且后于 VDD 上电。

(2)模拟输出设计

- 电压模式 :OUTx 与 FBx 短接(推荐 0Ω 电阻),负载电阻≥5kΩ,电容负载≤200pF(如需更大负载,需外部缓冲);

- 电流模式 :FBx 悬空,负载电压≤VDD-0.4V(确保输出 compliance),避免 OUTx 短路至 AGND/VDD(短路电流最大 60mA,需限流)。

(3)PCB 布局

- 分区布局 :模拟区(OUTx、FBx、VREF)与数字区(SPI/I²C 引脚)分离,AGND 与 DGND 单点连接,避免地弹噪声;

- 热设计 :裸露热焊盘与 AGND 平面完全覆盖焊接,添加 2~4 个 0.3mm 散热过孔,确保结温不超过 125°C(长期使用);

- EMC 优化 :时钟信号(SCLK)远离模拟引脚,长度匹配误差≤5mm,关键模拟引脚(VREF、OUTx)添加 RC 滤波(如 1kΩ 电阻 + 10nF 电容)。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

DAC38RF80 系列技术文档核心总结2025-11-07 827

-

DACx300x 系列技术文档总结2025-10-30 786

-

DAC53204-Q1 与 DAC63204-Q1 技术文档总结2025-10-29 851

-

DAC39RFS10-SEP产品技术文档总结2025-10-27 907

-

DAC60516 ADC 产品文档总结2025-10-23 853

-

RT-Thread文档_DAC 设备2023-02-22 661

-

DSP教程---ADC和DAC2021-09-16 1476

-

PWM DAC文档2016-05-03 709

-

BLE技术总结文档2015-10-29 824

全部0条评论

快来发表一下你的评论吧 !