芯片制造过程中的布线技术

描述

文章来源:学习那些事

原文作者:小陈婆婆

从铝到铜,再到钌与铑,半导体布线技术的每一次革新,都是芯片性能跃升的关键引擎。随着制程进入2nm时代,传统铜布线正面临电阻与可靠性的极限挑战,而镶嵌(大马士革)工艺的持续演进与新材料的融合,为超高密度互连和三维集成打开了新局面。本文将带你了解布线技术的最新突破——从低k介质到ALD沉积、从铜的延展到钌的崛起,窥见未来芯片互连的“立体革命”。

布线技术

在半导体制造中,布线技术的革新始终是推动芯片性能提升的关键驱动力。传统铝布线因电阻较高、电迁移现象显著,在高度集成化需求下逐渐暴露出信号延迟与可靠性瓶颈——当布线宽度缩至纳米级时,铝原子在高密度电子流驱动下易发生迁移,导致局部变薄或断裂,甚至引发微小突起,严重威胁器件稳定性。

为突破这一限制,铜因其更低的电阻率与优异的耐迁移特性,成为替代铝的理想材料,但铜难以通过传统干法刻蚀加工的难题催生了镶嵌工艺(大马士革工艺)的诞生。

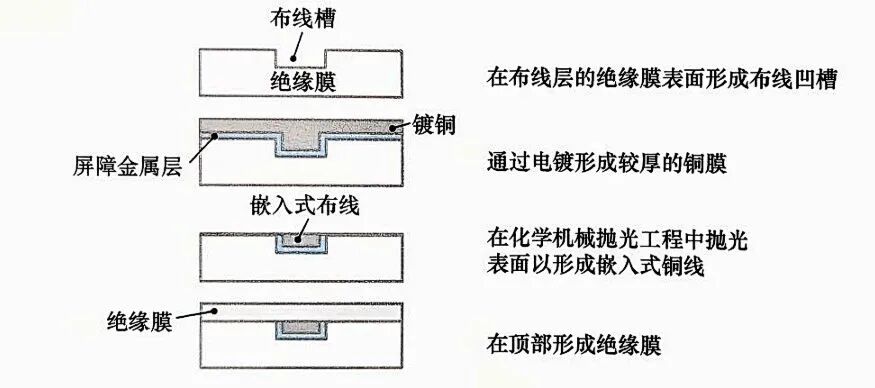

图 大马士革工艺

该工艺通过在绝缘膜表面预先刻蚀出布线凹槽,利用电镀技术沉积铜膜并填充凹槽,最终通过化学机械抛光(CMP)实现表面平面化,形成嵌入式铜布线结构。

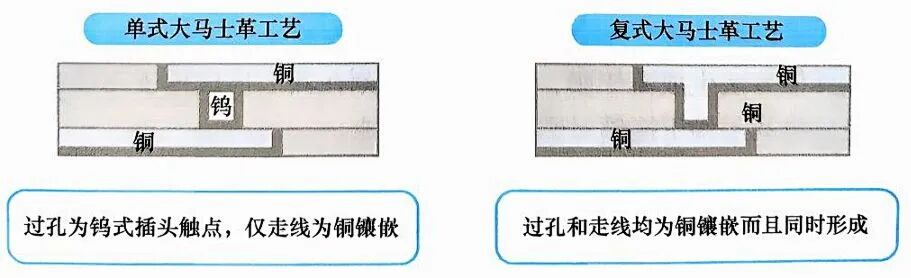

图 大马士革工艺的布线结构

铜的易电镀特性与凹槽填充工艺的结合,有效解决了铜刻蚀难题,同时通过CMP的精确控制确保了布线层的平整度与均匀性。

近年来,镶嵌工艺的演进聚焦于材料创新与工艺优化。IBM在2024年IEDM会议上提出,采用先进低k电介质(ALK)材料可显著提升铜布线的可靠性——该材料兼具高机械强度与抗等离子体损伤特性,能在缩小阻挡层厚度的同时维持介电击穿电压,有效降低线路电阻。

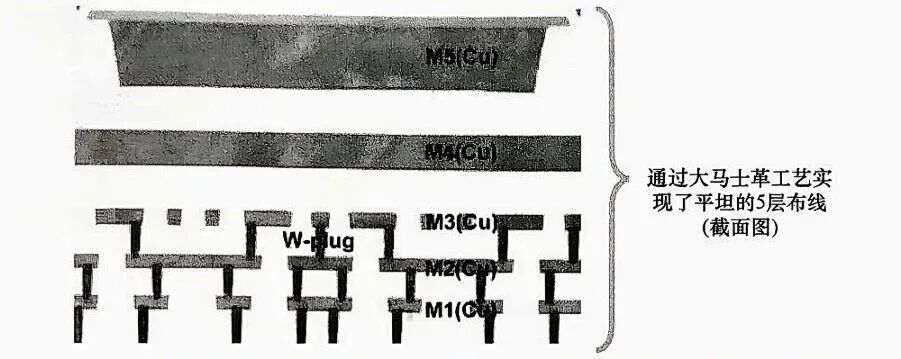

图 结合单式大马士革工艺和复式大马士革工艺的五层铜线的的嵌入式布线示例

例如,24nm间距的ALK布线通过优化阻挡层/衬里结构,实现了电迁移寿命的显著延长,较传统SiCOH材料提升超30%。此外,铑(Rh)与钌(Ru)等新型金属材料的引入为后铜时代提供了新思路:铑因低表面散射与低氧化倾向,可实现更薄的阻挡层甚至无障碍线结构,尽管成本较高,但通过回收工艺可将其控制在合理范围;钌则通过气隙集成技术,在顶通孔结构中降低电容约23%,同时提升电迁移性能,其18nm间距下的双级互连结构在1800小时测试中未出现故障,可靠性远超同尺寸铜布线。

在三维集成领域,镶嵌工艺与先进封装技术深度融合。台积电、长电科技等厂商通过CoWoS、FCBGA等封装技术扩大镶嵌工艺的应用场景,实现多层布线的立体堆叠,满足高性能计算与AI芯片对高密度互连的需求。例如,应用材料公司推出的增强版Black Diamond低介电材料结合钌-钴二元金属衬垫技术,可将衬垫厚度减少33%,在3nm节点实现25%的电阻降低,同时提升机械强度以支持芯片三维堆叠。化学机械抛光技术亦同步升级,通过智能化控制系统与绿色环保抛光液的开发,在保证亚纳米级表面粗糙度的同时,减少重金属污染并降低运营成本,适应7nm及以下制程对精度与环保的双重需求。

当前,镶嵌工艺正朝着更高精度、更强适应性与智能化方向发展。随着2nm及以下节点的推进,钌、铑等新型材料与气隙集成、原子层沉积(ALD)等工艺的结合,将进一步解决铜布线在超小尺寸下的电阻与可靠性挑战。同时,三维集成中镶嵌工艺与Chiplet技术的协同,正推动半导体产业从“制程竞赛”向立体集成创新模式转型。

-

【「大话芯片制造」阅读体验】+ 芯片制造过程和生产工艺2024-12-30 3374

-

芯片制造过程中的两种刻蚀方法2024-12-06 3934

-

新思科技发布1.6纳米背面布线技术,助力万亿晶体管芯片发展2024-09-30 1051

-

通过建立故障模型模拟芯片制造过程中的物理缺陷2023-06-09 2566

-

介绍RTL设计引入的后端实现过程中的布线问题2022-04-11 6128

-

芯片制造过程图解 CMP是什么意思2021-12-08 15593

-

影响制造过程中的PCB设计步骤2020-10-27 3140

-

测试技术助力芯片制造过程中质量和良率提升2019-12-05 3564

-

应当如何减少布线过程中的错误带来的损失呢?2016-08-25 2455

-

PCB设计过程中布线效率的提升方法2012-09-10 3847

-

RF设计过程中的PCB布线技巧2012-08-01 4840

-

电路板设计过程中采用差分信号线布线的优势和布线技巧2009-09-06 1622

全部0条评论

快来发表一下你的评论吧 !