ADC32RF5x 系列技术文档总结

描述

ADC32RF5x 是一款单核 14 位、2.6 GSPS 至 3 GSPS、双通道模数转换器 (ADC),支持输入频率高达 3 GHz 的射频采样。该设计最大限度地提高了信噪比 (SNR),并提供 -155 dBFS/Hz 的噪声频谱密度。使用额外的内部 ADC 和片上信号平均,噪声密度提高到 -161 dBFS/Hz。

每个ADC通道都可以使用支持相位相干跳频的48位NCO连接到四频数字下变频器(DDC)。使用GPIO引脚进行NCO频率控制,可以在不到1 μs的时间内实现跳频。

*附件:adc32rf55.pdf

该ADC32RF54和ADC32RF55支持具有子类 1 确定性延迟的 JESD204B 串行数据接口,数据速率高达 13 Gbps。

高能效ADC架构在3 Gsps时功耗为2.1 W/ch,并以较低的采样率提供功率扩展。

特性

- 14位、双通道2.6至3GSPS ADC

- 噪声频谱密度:

- NSD = -155.6 dBFS/Hz(无平均值)

- NSD = -158.1 dBFS/Hz(2x 平均)

- NSD = -160.4 dBFS/Hz(4 个平均值)

- 单核(非交错)ADC架构

- 孔径抖动:50 fs

- 低近距离残余相位噪声:

- 10 kHz 偏移时为 -127 dBc/Hz

- 频谱性能(f IN = 1 GHz,-4 dBFS):

- 2 倍内部平均

- 信噪比:62.3 dBFS

- SFDR HD2,3:63 dBc

- SFDR 最差杂散:85 dBFS

- 频谱性能(f IN = 1.8 GHz,-4 dBFS):

- 2 倍内部平均

- 信噪比:63 dBFS

- SFDR HD2,3:68 dBc

- SFDR 最差杂散:86 dBFS

- 输入满量程:1.1 至 1.35 Vpp(2 至 3.5 dBm)

- 代码错误率 (CER):10 -15

- 全功率输入带宽 (-3 dB):2.75 GHz

- JESD204B串行数据接口

- 最大通道速率:13 Gbps

- 支持子类 1 确定性延迟

- 数字下变频器

- 每个ADC通道最多4个DDC

- 复输出:4 倍至 128 倍抽取

- 48 位 NCO 相位相干跳频

- 快速跳频:< 1 us

- 功耗:2.6 W/通道(2x AVG)

- 电源:1.8 V、1.2 V

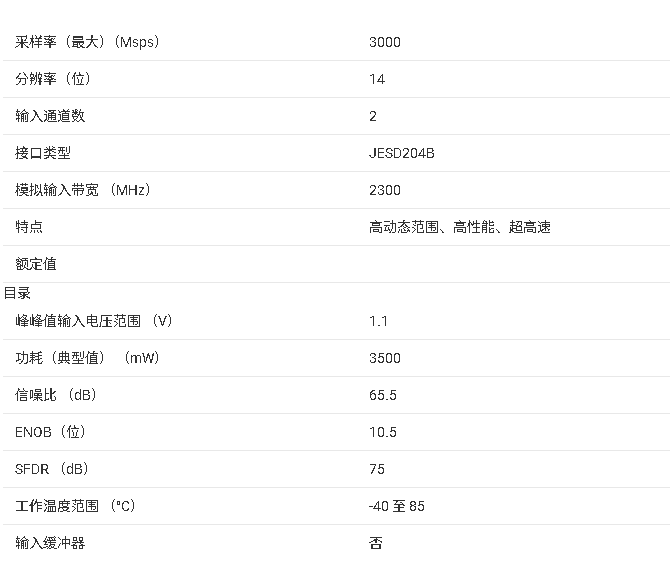

参数

方框图

一、产品概述与型号差异

ADC32RF5x 系列是专为射频采样设计的高性能双通道 ADC,通过单核心(非交错)架构、内部信号平均、可编程 DDC 等技术,平衡高采样率、低噪声与灵活信号处理能力。两款型号仅采样速率不同,其他功能与封装完全兼容,便于根据系统带宽需求选型。

1. 型号核心差异

| 型号 | 最高采样速率 | 核心应用场景 | 关键性能差异(典型值,TA=25℃) |

|---|---|---|---|

| ADC32RF54 | 2.6 GSPS | 中高频段信号采集(如 L 波段) | 1GHz 输入时 SNR 62.3 dBFS,噪声谱密度(NSD)-155.6 dBFS/Hz |

| ADC32RF55 | 3.0 GSPS | 超高频段信号采集(如 S 波段) | 1.8GHz 输入时 SNR 63 dBFS,NSD-158.1 dBFS(2x 平均) |

2. 基础参数总览

| 类别 | 关键指标 | 说明 |

|---|---|---|

| 封装规格 | 9mm×9mm 64 引脚 VQFN(RTD 封装) | 无铅封装,0.9mm 最大高度,底部热焊盘(需接地),适配高密度射频布局 |

| 工作温度 | -40℃~+85℃ | 满足工业级宽温环境需求 |

| 供电范围 | AVDD18:1.75V | 四组独立供电,CLKVDD 需低噪声电源,避免影响时钟相位噪声 |

| 静态功耗 | 2.6 GSPS(2x 平均):5.25W;3.0 GSPS(4x 平均):7.1W | 功耗随采样率与平均模式线性增加,支持关断未用通道降功耗 |

| 核心集成 | 14 位 ADC 核心 ×8(用于平均)、48 位 NCO、JESD204B 接口、内部校准模块 | 减少外围器件,简化射频采样系统设计 |

二、核心功能与性能参数

1. 高速射频采样模块

作为核心功能,ADC32RF5x 支持直接射频采样(输入频率最高 3GHz),通过内部多 ADC 平均技术优化噪声性能,适配不同精度需求:

(1)性能参数

- 分辨率与精度 :

- 14 位分辨率,微分非线性(DNL)±0.85 LSB,积分非线性(INL)±3.5 LSB;

- 噪声特性:无平均时 NSD-155.6 dBFS/Hz,2x 平均时 - 158.1 dBFS/Hz,4x 平均时 - 160.4 dBFS/Hz;

- 孔径抖动:典型 50 fs,近距残余相位噪声 - 127 dBc/Hz(10kHz 偏移),保障高频采样精度。

- 输入特性 :

- 全功率带宽(-3dB):2.75 GHz(1x/2x 平均)、2.1 GHz(4x 平均);

- 输入范围:1.1

1.35 Vpp(差分),对应 23.5 dBm 功率; - 输入阻抗:默认 100Ω 差分(可通过 SPI 配置为 50Ω),支持 AC/DC 耦合。

- 动态性能 :

- 信噪比(SNR):1GHz 输入、2x 平均时 62.3 dBFS,1.8GHz 输入时 63 dBFS;

- 无杂散动态范围(SFDR):1GHz 输入时 85 dBFS,二阶谐波(HD2)63 dBc,三阶谐波(HD3)68 dBc;

- 建立时间:65 ns(1/4~3/4 量程,±2 LSB),支持快速信号跳变捕获。

(2)关键功能

- 多模式平均 :支持 1x(无平均)、2x、4x 内部 ADC 平均,通过多核心并行采样降低噪声(每 2x 平均噪声改善~3 dB),4x 平均时需将输入信号分至 INx1/INx2 引脚;

- 模拟抖动抑制 :可选模拟带外抖动(带宽~20MHz,幅度 ±1024 码),降低低阶谐波失真,1GHz 输入时 SFDR 提升至 89 dBFS;

- 过范围检测 :支持 GPIO 引脚快速指示(延迟~6 时钟周期)或 JESD 数据流嵌入(替换 LSB),过范围标志可通过 SPI 清零,适配故障安全设计。

2. 数字下变频器(DDC)模块

每个 ADC 通道集成 4 个可编程 DDC,支持复杂信号下变频与抽取,减少后端处理器数据带宽压力:

(1)性能参数

- 抽取范围 :4x~128x 复杂抽取,支持单频段(1 个 DDC)、双频段(2 个 DDC)、四频段(4 个 DDC)模式;

- NCO 精度 :48 位相位累加器,频率分辨率 ±0.001 Hz(3GSPS 采样时),支持相位相干跳频,跳频时间 < 1μs;

- 滤波特性 :复杂抽取模式下通带带宽~80%,阻带抑制≥85 dB;实抽取模式下通带带宽~40%,无频率偏移。

(2)关键功能

- 灵活频段配置 :单频段模式支持 4x 抽取(带宽 750MHz@3GSPS),四频段模式支持 128x 抽取(带宽 23.4MHz@3GSPS),适配宽窄带信号并行处理;

- 相位相干跳频 :通过 SYSREF 信号同步 NCO 相位,多次跳频后相位连续,无相位突变导致的杂散;

- 动态模式切换 :支持单频段与四频段模式动态切换(无需重启 JESD 接口),切换时保持 SerDes 速率与 lanes 数不变,适配多带宽场景。

3. JESD204B 高速接口模块

集成 JESD204B 串行数据接口,支持高速数据传输与确定性延迟,适配 FPGA / 处理器后端处理:

(1)性能参数

- 传输速率 :最高 13 Gbps/lane,支持 8 lanes 并行,总带宽 104 Gbps(3GSPS 时);

- 延迟特性 :子类 1 确定性延迟,抽取 4x 时延迟 456 时钟周期,支持多器件同步;

- 信号完整性 :输出摆幅 700 mVpp(差分),随机抖动(RJ)0.6 ps RMS(12.8 Gbps),确定性抖动(DJ)14.7 ps pp。

(2)关键功能

- 多帧配置 :支持 LMFS(L=M=F=S)灵活配置,如 8-2-8-20(8 lanes、2 转换器、8 字节 / 帧、20 帧 / 多帧),适配不同数据压缩需求;

- 初始 lane 对齐(ILA) :自动发送 K28.5 逗号字符实现码组同步,支持 4 个多帧的 ILA 序列,保障多 lane 数据对齐;

- 测试模式 :支持 PRBS(2^7-1 至 2^31-1)、 Ramp、交替码型输出,简化接口调试,无需接入实际模拟信号。

4. 校准与同步模块

(1)Foreground 校准

- 校准对象 :补偿 ADC 增益 / 偏移误差、温度漂移,支持单通道 / 双通道同时校准;

- 校准方式 :通过 SPI 触发或 GPIO1 引脚触发,校准时间~23 ms×3GSPS / 实际采样率,校准后 INL 改善至 ±2 LSB;

- 后台校准 :支持连续校准模式,切换备用 ADC 核心时输出幅度波动 < 0.05 dB,相位变化 < 0.01°,无数据丢失。

(2)系统同步(SYSREF)

- 同步功能 :外部 SYSREF 信号(差分输入,100Ω 端接)用于复位 NCO、DDC 与 JESD 接口,实现多 ADC 相位同步;

- 捕获窗口 :内置 ±50 ps SYSREF 捕获窗口监测,避免时钟滑移导致的同步误差,支持 AC/DC 耦合配置;

- 多器件同步 :SYSREF 频率需为内部多帧时钟(LMFC)的子谐波,支持 16 个 SYSREF 脉冲后自动停止捕获,适配大规模多芯片系统。

三、功能架构与典型应用

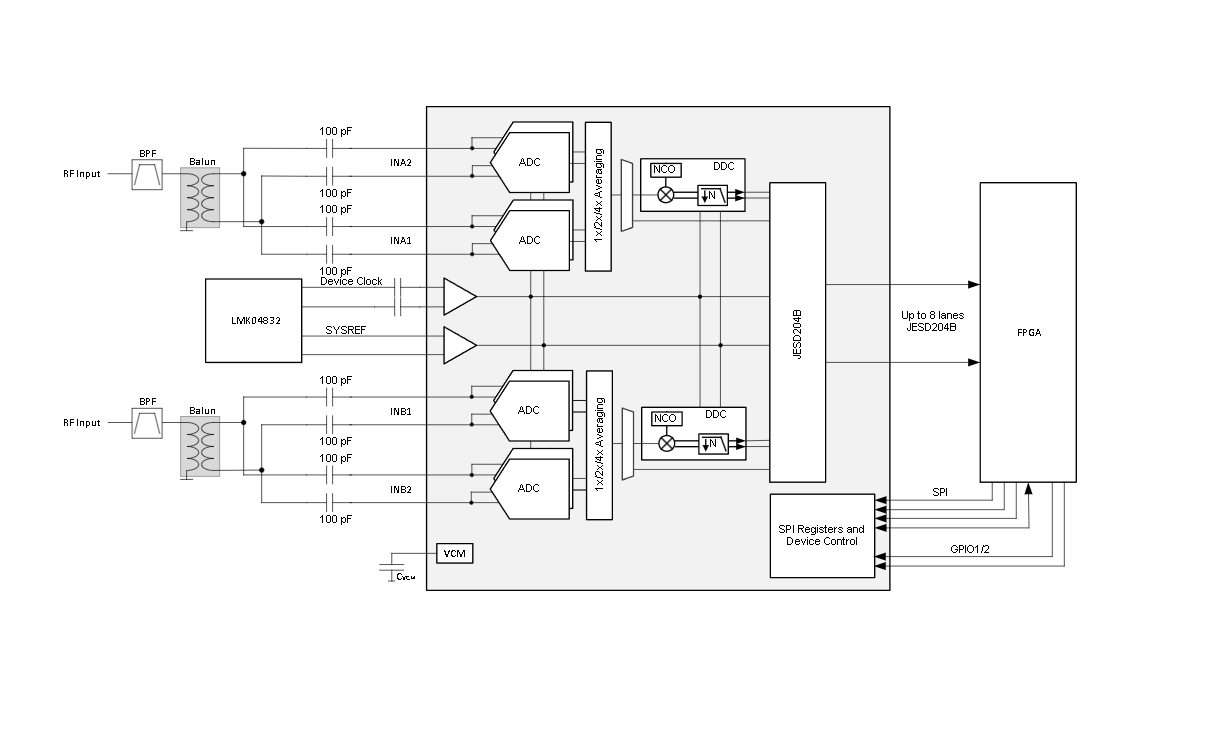

1. 核心架构

采用 “模拟采样 - 数字处理 - 高速传输” 三层架构,模块协同实现高可靠性射频采样:

- 模拟采样层 :双通道独立 ADC 核心(每通道含 4 个内部 ADC 用于平均),支持 100Ω/50Ω 输入端接,模拟抖动抑制;

- 数字处理层 :每通道 4 个 DDC(含 48 位 NCO)、抽取滤波器、过范围检测逻辑,实现信号下变频与带宽压缩;

- 高速传输层 :JESD204B 接口(8 lanes)、SerDes 输出 MUX(支持 lane 重排序)、测试模式生成器,保障数据高速传输与调试。

2. 典型应用场景:宽带射频采样接收机

(1)应用原理

ADC32RF55 直接采样 3GHz 以下射频信号,通过 2x 内部平均降低噪声(NSD-158.1 dBFS/Hz),DDC 将信号下变频至中频(如 75MHz)并 16x 抽取,数据通过 JESD204B 接口传输至 FPGA(如 Xilinx UltraScale+)进行后续信号处理:

- 核心电路 :射频信号经 Balun 变压器(如 Marki BAL-0009SMG)转换为差分信号,AC 耦合至 INx1 引脚;采样时钟由低噪声时钟源(如 LMK04832)提供,SYSREF 信号同步多 ADC;

- 关键参数 :3GSPS 采样、4x 抽取时,有效带宽 750MHz,SNR 65 dBFS,满足相控阵雷达多通道信号采集需求。

(2)设计要点

- 电源设计 :AVDD18/AVDD12/CLKVDD/DVDD 需独立供电,CLKVDD 采用低噪声 LDO(如 TPS7A8400),各电源引脚就近并 0.1μF 陶瓷电容 + 10μF 钽电容,抑制射频噪声;

- 布局建议 :模拟输入(INx1/INx2)与时钟(CLKP/M)采用 100Ω 差分布线,长度匹配误差 < 5 mil;数字信号(JESD lanes)与模拟信号分区隔离,模拟地与数字地单点连接;

- 同步设计 :SYSREF 信号与采样时钟边缘对齐,使用 50Ω 阻抗匹配,布线长度短于 10cm,避免同步延迟导致的相位偏差。

四、电气特性与设计建议

1. 关键电气特性(典型值,TA=25℃,VDD=1.8V/1.2V)

| 参数类别 | 指标(ADC32RF55,3GSPS,2x 平均) | 指标(ADC32RF54,2.6GSPS,1x 平均) |

|---|---|---|

| 静态精度 | INL±3.5 LSB,DNL±0.85 LSB,增益误差 ±0.2 dB | INL±3.2 LSB,DNL±0.8 LSB,增益误差 ±0.3 dB |

| 动态特性 | SNR 63 dBFS(1.8GHz 输入),SFDR 86 dBFS | SNR 62.3 dBFS(1GHz 输入),SFDR 85 dBFS |

| 电源抑制比 | AC -68 dB(50Hz/60Hz),DC 0.25 mV/V | AC -65 dB(50Hz/60Hz),DC 0.3 mV/V |

| 功耗 | AVDD18 电流 370mA,DVDD 电流 2440mA,总功耗 5.25W | AVDD18 电流 230mA,DVDD 电流 1550mA,总功耗 3.4W |

2. 设计建议

(1)电源与时钟设计

- 电源隔离 :AVDD12/CLKVDD 与 DVDD 不可共地,避免数字开关噪声耦合至模拟电路;推荐采用 “开关电源 + LDO” 两级供电,开关电源(如 LMS3635)提供高效率,LDO 抑制开关噪声;

- 时钟优化 :采样时钟幅度需 > 1 Vpp(差分),使用带通滤波器(如 Mini-Circuits TCM2-43X+)滤除时钟杂散,时钟线与模拟输入线间距 > 2mm,减少串扰。

(2)PCB 布局

- 分区设计 :将模拟区(INx1/INx2、CLKP/M、VREF)、数字区(JESD lanes、SPI)、电源区(LDO、滤波电容)严格分区,模拟区铺铜厚度≥2oz,降低阻抗;

- 热设计 :底部热焊盘通过 4 个过孔连接至大面积接地铜皮,结到环境热阻 RθJA=20.1℃/W,确保满负荷时结温 < 105℃;

- 射频防护 :模拟输入引脚附近预留 50Ω/100Ω 匹配电阻位置,INx2 引脚未使用时需接地,避免噪声耦合。

(3)校准与同步配置

- 上电校准 :上电后需执行 Foreground 校准(SPI 写入 0x20 页 0x45 寄存器),校准前确保 SYSREF 信号稳定,校准后 INL 改善至 ±2 LSB;

- SYSREF 配置 :通过 0x02 页 0x236 寄存器启用 SYSREF 计数,AC 耦合时需配置 0xB4 寄存器启用内部偏置,确保同步窗口内无信号跳变;

- JESD 调试 :初期可启用 Ramp 测试模式(0x04 页 0x2E 寄存器),验证 lane 对齐与数据传输,无误后切换至正常采样模式。

-

ADC12D1000RF 12 位高采样率 RF 采样 ADC 技术文档总结2025-11-18 994

-

ADC32RF8x 系列产品核心信息总结2025-11-10 705

-

ADC32RF42 技术文档核心总结2025-11-07 777

-

ADC3562 技术文档总结2025-10-30 598

-

ADC354x 系列技术文档总结2025-10-29 1294

-

ADC32RF54双通道 14 位高速 RF 采样 ADC 技术总结2025-10-28 995

-

ADC34RF55 技术文档总结2025-10-27 893

-

高性能射频采样ADC:ADC32RF5x系列技术解析2025-08-15 1418

-

ADC32RF5x双通道14位2.6至3GSPS射频采样数据转换器数据表2024-07-15 560

全部0条评论

快来发表一下你的评论吧 !