DAC82001 16 位低毛刺单通道电压输出 DAC 技术文档总结

描述

16位DAC82001是一款高精度、低功耗、单通道数模转换器(DAC),具有无缓冲电压输出。

该DAC82001采用3.3V和5V电源,提供1LSB DNL和2LSB INL的线性度。高精度与微型封装相结合,使该器件成为增益和失调校准、电压设定点生成和电源控制等应用的绝佳选择。该DAC82001集成了上电复位 (POR) 电路。POR电路确保DAC输出根据RSTSEL引脚的状态以零刻度或中量程上电,并保持该刻度,直到将有效代码写入器件。RESET引脚拉低后,所有内部寄存器均异步复位。

*附件:dac82001.pdf

该DAC82001使用多功能三线串行外设接口 (SPI),工作时钟速率高达 50 MHz。

特性

- 16 位性能:1-LSB DNL 和 2-LSB INL

- 低毛刺能量:0.5 nV-s

- 快速建立:1 μs

- 宽电源:2.7 V 至 5.5 V

- 宽基准电压源范围:2.0 V 至 V

DD - 低功耗:5.0 V 时为 250 μA

- 高达 50 MHz 的 3 线串行外设接口 (SPI)

- 重置为零比例或中比例

- 1.62伏伏

IH的带 VDD= 5.5 伏 - 温度范围:–40°C 至 +85°C

- 封装:微型 10 引脚 WSON

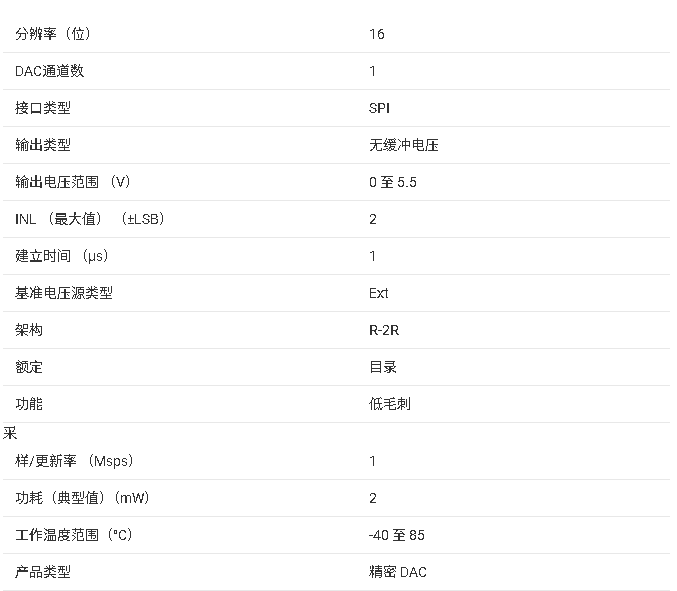

参数

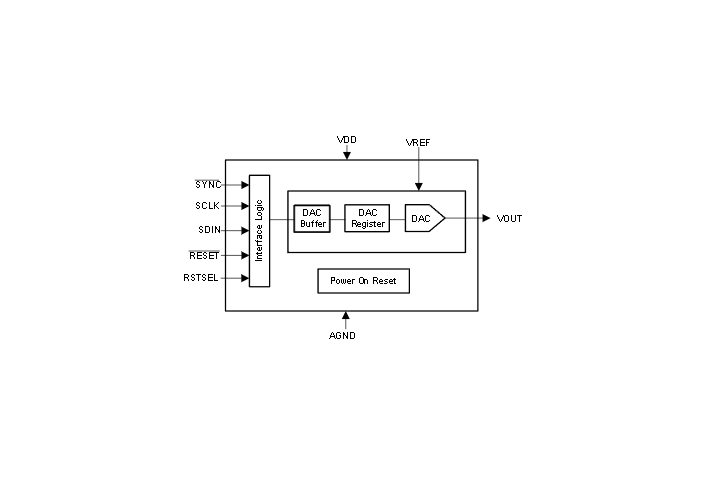

方框图

一、产品核心定位与基础参数

DAC82001 以 “高线性度 + 低毛刺 + 小封装” 为核心优势,通过分段 R-2R 架构与优化电源管理,平衡精度与系统适配性,适配 2.7V~5.5V 宽供电场景。

1. 核心基础参数总览

| 类别 | 关键指标 | 说明 |

|---|---|---|

| 核心规格 | 分辨率 / 通道数 / 输出类型 | 16 位,单通道,无缓冲电压输出(需外部运放缓冲时需额外配置) |

| 供电与功耗 | 供电范围 / 静态电流 | 2.7V~5.5V 单电源;5V 时静态电流 250μA(典型值),功耗低至 1.25mW |

| 封装与温域 | 封装类型 / 尺寸 / 工作温度 | 10 引脚 WSON(2.5mm×2.5mm),超小尺寸适配高密度布局;-40℃~+85℃宽温 |

| 参考电压 | 输入范围 / 阻抗 | 2.0V~VDD(与供电电压匹配),输入阻抗 5kΩ,输入电容 75pF |

| 数字接口 | 接口类型 / 最高速率 | 3 线 SPI(SYNC/SCLK/SDIN),最高 50MHz 时钟,24 位移位寄存器帧格式 |

二、核心性能参数

1. 静态性能(TA=-40+85℃,VDD=2.7V5.5V)

(1)线性度与精度

- 积分非线性(INL) :±2 LSB(最大值),典型值 ±0.6 LSB,保障全量程输出线性;

- 微分非线性(DNL) :±1 LSB(最大值),典型值 ±0.5 LSB,无失码,避免输出台阶失真;

- 总未调整误差(TUE) :±0.06% FSR(最大值),典型值 0.04% FSR,减少系统级校准需求;

- 零码 / 增益误差 :零码误差 ±2.6 LSB,温度系数 ±0.02 ppm/℃;增益误差 ±20 LSB,温度系数 ±0.1 ppm/℃,全温域精度稳定性高。

(2)输出特性

- 输出范围 :0

VREF(与参考电压匹配,如 VREF=5V 时输出 05V),输出阻抗 6.25 kΩ(典型值); - 电源抑制比(PSRR) :DC 模式 5 μV/V(典型值),AC 模式 - 72 dB(10kHz 时),减少供电噪声对输出的影响;

- 输出噪声 :0.1Hz~10Hz 低频噪声 0.1 μVPP(典型值),10kHz 噪声密度 10 nV/√Hz,保障微弱信号输出纯净度。

2. 动态性能(关键指标决定瞬态输出质量)

DAC82001 的动态性能在测试测量、波形生成场景中至关重要,核心指标如下:

| 动态特性 | 关键指标 | 说明 |

|---|---|---|

| 建立时间 | 至 1/2 LSB 精度(CL=10pF) | 1 μs(典型值),快速响应数字码值变化,适配高频波形生成(如 200 kSPS 更新率) |

| 毛刺能量 | ±1 LSB 跳变(大进位附近) | 0.5 nV・s(典型值),大幅减少码值切换时的输出扰动,适配精密电压设定 |

| 无杂散动态范围(SFDR) | 1kHz 正弦波输出(40kHz 低通滤波) | -96 dB(典型值),含 7 次谐波以内杂散,波形失真小 |

| 总谐波失真(THD) | 1kHz 正弦波输出(40kHz 低通滤波) | -91 dB(典型值),保障模拟输出波形纯度,适配超声扫描等信号生成场景 |

| 上电 / 掉电毛刺 | 负载 CL=10pF | 上电毛刺幅度 0.8V(典型值),掉电无明显过冲,避免系统上电冲击 |

3. 复位与初始化功能

器件支持硬件复位与 上电复位(POR) ,灵活适配系统启动与故障恢复场景:

| 复位模式 | 触发方式 / 输出状态 | 关键特性 |

|---|---|---|

| 上电复位(POR) | VDD 低于 0.7V 并维持 1ms 以上触发,无需外部信号 | 输出状态由 RSTSEL 引脚决定:RSTSEL 接 AGND 时输出 0 刻度(0V),接 VDD 时输出中刻度(VREF/2) |

| 硬件复位 | RESET 引脚拉低(低电平有效),异步触发 | 复位后所有内部寄存器初始化,输出状态同 POR;复位引脚需先拉高再进行 SPI 通信,需等待 250μs 稳定时间 |

| 软件复位 | 向 TRIGGER 寄存器(0x5h)写入 0x1010 指令 | 等效 POR 效果,无需硬件引脚操作,适配软件控制场景(如远程系统校准) |

三、关键功能模块详解

1. DAC 架构与传输函数

器件采用 分段 R-2R 架构 ,兼顾精度与动态性能,核心架构与数据处理流程如下:

(1)架构设计

- 分段结构 :16 位数据分为 “4 位 MSB+12 位 LSB”,MSB 解码为 15 路匹配电阻开关(E1

E15),LSB 驱动 12 位 R-2R 梯形网络(S0S11),减少电阻失配导致的线性误差; - 传输函数 :输出电压由数字码值与参考电压共同决定,公式为:VOUT =216**−1DAC**_DATA ×VREF

其中,DAC_DATA 为 065535 的 16 位二进制码值(直二进制格式),VREF 为外部参考电压(2.0VVDD)。

(2)寄存器与输出更新模式

器件内置 4 个核心寄存器,支持异步更新与 同步更新 ,适配不同时序需求:

| 寄存器名称 | 地址 / 功能 | 关键配置 |

|---|---|---|

| NOOP 寄存器 | 0x0h | 空操作指令,写入后无寄存器变化,用于 SPI 通信测试 |

| SYNC 寄存器 | 0x2h | 配置输出更新模式:DAC_SYNC_EN=0(默认,异步更新,写缓冲后立即更新输出);DAC_SYNC_EN=1(同步更新,需 LDAC 触发) |

| TRIGGER 寄存器 | 0x5h | 含 LDAC 触发位(同步更新时触发输出)与软件复位位(0x1010 指令触发 POR) |

| DAC 寄存器 | 0x8h | 16 位数据寄存器,复位时默认 0x0000(RSTSEL=AGND)或 0x8000(RSTSEL=VDD) |

2. 数字接口与通信协议

3 线 SPI 接口是器件与控制器(如 MCU/FPGA)的核心交互通道,需严格遵循时序要求以保障数据传输正确性:

(1)SPI 帧格式与时序

- 帧结构 :24 位数据帧(Bit23

Bit0),Bit23 为写使能位(固定为 0,仅支持写操作),Bit22Bit16 为寄存器地址,Bit15~Bit0 为 16 位 DAC 数据(MSB 对齐); - 关键时序参数 :SCLK 高电平时间≥9ns、低电平时间≥9ns;SDIN 建立时间≥5ns、保持时间≥10ns;SYNC 拉低到 SCLK 下降沿 setup 时间≥13ns,确保数据稳定锁存;

- 中断处理 :若 SYNC 在 24 个 SCLK 下降沿前拉高,视为无效写操作,移位寄存器复位,避免错误数据写入。

(2)接口防护与配置

- 数字输入引脚(SYNC/SCLK/SDIN)支持 1.62V 高电平(VDD=5.5V 时),输入电流 ±5μA,引脚电容 10pF,兼容 3.3V/5V 逻辑电平;

- 建议在 SYNC/SCLK 引脚配置下拉电阻(如 10kΩ),避免悬空时噪声干扰;SDIN 引脚需确保数据在 SCLK 下降沿稳定输入。

四、典型应用场景与设计建议

1. 核心应用场景

DAC82001 的核心价值在于 “高线性度 + 低毛刺”,典型应用包括:

- 任意波形发生器(AWG) :1μs 建立时间 + 96dB SFDR,支持 200kSPS 更新率,适配测试测量设备的正弦波、三角波生成;

- 双极性模拟输出 :通过外部运放(如 OPA210)将 0~VREF 单极性输出转换为 ±10V 双极性,适配 PLC 模拟输出模块;

- 精密电压设定 :0.06% FSR 总未调整误差,用于半导体测试中的精准偏置电压生成,或电池测试的充放电电压控制;

- 超声扫描仪时间增益补偿(TGC) :低噪声与高线性度,保障超声信号放大过程中的增益校准精度。

典型应用电路示例(双极性输出)

- 电路结构 :DAC82001 输出(0~2.5V)经 OPA210 运放构成差分放大电路,配合 8.25kΩ/33.2kΩ 电阻网络,将单极性信号转换为 ±10V 双极性输出;

- 关键器件 :参考电压采用 REF5025(2.5V 低噪声基准,漂移 ±5ppm/℃),运放供电 ±15V 避免输出钳位,VREF 引脚并联 100pF 电容抑制高频噪声;

- 性能指标 :输出噪声 < 3nV/√Hz(100Hz~1MHz),压摆率 2.5V/μs,满足快速电压切换需求。

2. 关键设计建议

(1)电源与参考电压设计

- 电源滤波 :VDD 引脚就近并联 0.1μF 陶瓷电容(X7R/NP0 dielectric)+1μF 钽电容,抑制高频噪声;若使用开关电源,需在电源入口增加 LC 滤波(如 10μH 电感 + 10μF 电容);

- 参考电压配置 :VREF 需小于 VDD,建议使用低噪声基准(如 REF50xx 系列),并在 VREF 引脚并联 100nF+47pF 电容(前者抑制低频噪声,后者优化动态响应)。

(2)PCB 布局与输出缓冲

- 布局分区 :模拟区(VOUT/VREF/AGND)与数字区(SYNC/SCLK/SDIN)严格分离,AGND 与数字地单点连接,避免串扰;VOUT 引脚布线短而直,减少寄生电容(建议 < 10pF);

- 输出缓冲 :因器件无内置输出缓冲,VOUT 阻抗较高(6.25kΩ),需外部运放缓冲时,优先选择低噪声、高带宽型号(如 OPA328,适合 AWG 场景;OPA210,适合双极性输出场景),运放输入失调电压需 < 10μV 以避免精度损失。

(3)复位与校准设计

- 复位配置 :RSTSEL 引脚根据需求接 AGND(上电零刻度)或 VDD(上电中刻度),建议通过 0Ω 电阻跳帽可配置,适配不同系统初始化需求;

- 系统校准 :若需更高精度,可在系统上电后通过软件写入校准码值(如测量 VOUT 实际值后调整 DAC_DATA),或利用外部 ADC 监测输出并闭环校准。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

MAX5308/MAX5309:低功耗、低毛刺的八通道10位电压输出DAC2026-04-17 598

-

深入解析SGM5351 - 16:16位超低毛刺电压输出DAC2026-03-12 256

-

DAC82002 16 位低毛刺双通道电压输出 DAC 技术文档总结2025-10-29 1160

-

DAC8501单通道、16位缓冲电压输出数模转换器(DAC)数据表2024-07-24 831

-

DAC5571低功耗、单通道、8位缓冲电压输出DAC数据表2024-07-19 720

-

DAC8551-Q1汽车类16位、超低毛刺脉冲、电压输出DAC数据表2024-07-16 629

-

DAC82002 16位、低毛刺脉冲、双通道电压输出、非缓冲DAC数据表2024-07-15 445

-

AD5423:单通道16位电流/电压输出DAC,支持HART连接2021-05-23 1381

-

UG-1554:使用HART连接评估AD5423单通道16位电流或电压输出DAC2021-05-18 811

-

UG-442:评估AD5422单通道、16位、电流源和电压输出DAC、HART连接2021-05-10 1127

-

16通道、16位/12位电压输出DAC2021-04-29 1323

-

UG-1268:评估采用动态电源控制和HART连接的AD5758单通道16位电流和电压输出DAC2021-04-26 829

-

AD5758:单通道16位电流和电压输出DAC,支持动态电源控制和HART连接数据表2021-04-23 1166

全部0条评论

快来发表一下你的评论吧 !