通过25 Gbps串行多通道收发器PCB设计工程实例

电子说

描述

摘要: 高速串行收发信道设计问题在5G通信以及数据中心的设计中越来越受到重视。通过25 Gbps串行多通道收发器PCB设计工程实例,从而分析工程实现过程中遇到的过孔设计、阻抗匹配以及通道串扰等信号完整性问题,采用Cadence Sigrity全波三维电磁仿真的方法和链路仿真方法,有针对性地在工程实现的不同阶段为问题的解决提供不同的策略方法,提升了设计与仿真优化的效率,缩短了从设计到量产的时间。

0 引言

随着高速串行解串(SERDES)收发器的速率不断提高,小型化以及高集成度的要求提高,使用三维电磁全波仿真工具对电气互联的信号完整性的设计变得尤为重要[1-3]。图1中为典型的SERDES走线。与单一传输线的结构不同,如图中所示,在芯片与PCB的连接处,连接器与PCB的连接处,全波电磁仿真工具可以提供精确的模型以及场分布的计算,从而帮助通道信号完整性的设计。

信号完整性设计分为两个阶段:布线前与完成布线后。通过三维模型仿真能力可以在布线前对比不同方案的仿真结果指导布线;在完成布线后,通过对布线的三维电磁建模,评估设计方案的性能指标。本文通过25 Gbps SERDES设计的工程实例,分析芯片与PCB的连接处的设计要点,在布线前、后的设计过程中,通过应用三维电磁仿真以及通道仿真确保满足设计需求。

1 高速SERDES的介绍

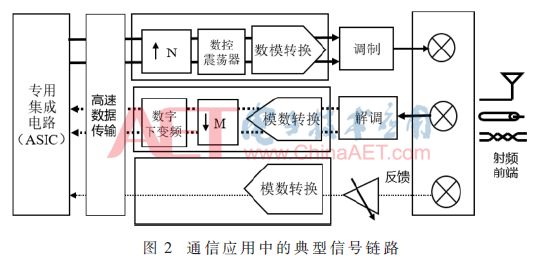

在典型的数据通信应用中,信号链路通常由数字基带模块、数模/模数转换模块以及射频前端模块组成。而高速串行收发模块作为信号通路连接数字基带与转换器模块[4-6]。随着对链路中数据吞吐量的需求的不断提升,宽带和高速数据转换器应用,需要不断地提升串行收发模块的数据速率。通信应用中的典型信号链路如图2所示。

为保证数据在链路收发过程中的误码率低于或等于10-15,电子器件工程联合会(JEDEC)发布了JESD204标准[7-8]。该标准被广泛应用在无线通信、雷达系统、软件定义无线电、便携设备以及医疗设备中。2018年发布的C类标准(JESD204C)将链路的最大速率由B类标准(JESD204B)的12.5 Gbps扩展到32 Gbps。在单位时间内恒定的数据量的情况下,传输速率的提升意味着更少的互联通道,从而减小了系统实现所需的空间,节约了成本,同时也便于系统的小型化设计。

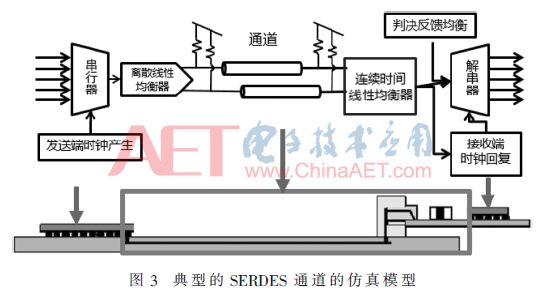

在SERDES仿真中,需要通道模型、收发端芯片模型。随着数据速率的提升,则需要更多的参数模型,例如抖动、串扰以及电源噪声。数据速率的提升也带动了SERDES的发展。为了支持更高的数据速率,SERDES集成了均衡技术,例如离散时间均衡、连续时间均衡、判决反馈均衡以及不同种类的时钟恢复电路,如图3所示。

在JESD204C的标准中,定义了JESD204C的面向对象模型(JCOM)作为EDA工具辅助SERDES通道的仿真。JCOM集成了均衡、时钟恢复、抖动、串扰、电源噪声等参数,具有精确、自定义芯片模型(Custom Device Models)、知识产权(IP)保护等特点[9]。JCOM的仿真结果以品质因数的形式给出。

2 高速SERDES的仿真

2.1 布线前仿真

对于球状矩阵排列(BGA)封装的高速SERDES的扇出,在布线之前,为了提升芯片上通道之间的隔离度,使用了新的扇出方式,需要电磁仿真验证新的SERDES 通道布线方法。

对于SERDES通道在PCB上的走线,有两种可选的方式:

(1)使用带背钻的过孔,从PCB的第一层到PCB的第三层,之后在PCB第三层走一小段距离之后,再使用背钻过孔,回到PCB第一层。

(2)使用通孔从PCB第一层到PCB的底层。

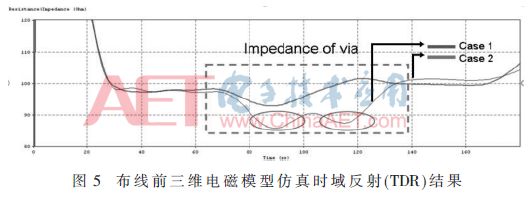

对两种方案进行建模分析,如图4所示。通过对比两种方案的的阻抗连续性图,如图5所示,可知方案二的阻抗连续性优于方案一的阻抗连续性,因此第二种方案是优选的。通过对比两种方案的模型可知,背钻(back drilling)后会留下过孔残桩(stub),如图6所示,从而恶化阻抗的连续性。

2.2 布线后仿真

在完成布线后,选用了18层100 mil厚的PCB。在走线的过程中,遇到了以下的问题:

(1)由于BGA扇出位置空间有限,使用“地-信号-信号-地”的方式的过孔从PCB的顶层到底层扇出的过程中,地过孔的相对位置必须被折弯,如图7所示,这就需要通过仿真来确定过孔参数,从而得到差分100 Ω的过孔。

(2)弯折的过孔会导致并排扇出的SERDES通道之间的串扰增大。

(3)设计中的差分过孔的参数为5 mil的直径,但加工中对于100 mil厚的PCB,至少使用6 mil的过孔。使用6 mil的过孔会导致SERDES通道走线阻抗不匹配,从而也会增大通道之间的串扰问题。

为了评估通道的性能,使用三维全波电磁仿真工具对通道进行建模,在抽取多通道的S参数之后,使用SERDES通道仿真方法,比如JCOM仿真等方法衡量通道信号质量。

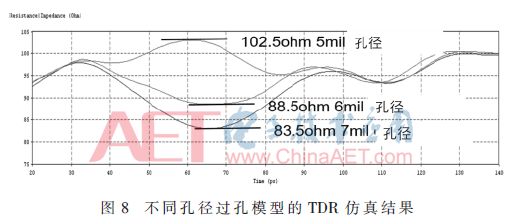

2.2.1 过孔的三维建模与仿真

为了设计扇出位置的差分100 Ω过孔,将过孔进行三维建模,并且优化过孔参数,仿真结果如图8所示。根据仿真结果可知,5 mil的过孔孔径为优选值,但对于100 mil厚的PCB,最小可选孔径为6 mil,因此6 mil孔径为最终的设计值。然而6 mil的孔径会带来11.5 Ω的阻抗失配,因此需要通道仿真验证过孔的失配SERDES性能的影响。

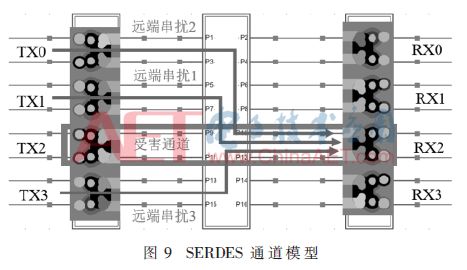

2.2.2 SERDES通道的建模与仿真

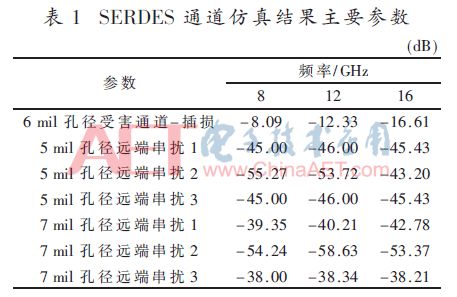

为了验证过孔的阻抗不连续以及多通道之间串扰对通道性能的影响,对SERDES通道进行建模,如图9所示。通道由3部分组成:发射端和接收端的扇出过孔以及PCB走线。考虑到过孔孔径的加工误差,最终结果将包括5 mil、6 mil和7 mil的孔径的仿真结果,如表1所示。

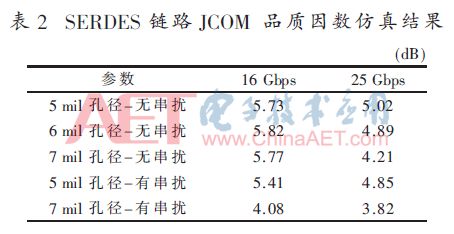

在完成通道仿真后,结合SERDES芯片JCOM模型进行链路的仿真。发送端具有3阶离散线性均衡(FFE);接收端具有最大9 dB连续时间线性均衡(CTLE)以及3阶判据反馈均衡(DFE),仿真结果如表2所示。

在JESD204的C类标准中,如果JCOM的仿真结果的品质因数超过2 dB,则认为通道符合设计规范的要求。根据表2中的结果可知,在7 mil孔径及有串扰的情况下,通道品质因数为3.82 dB,高于设计规范的要求,因此可以认为通道的设计满足在25 Gbps速率下10-15链路误码率的要求。

3 结论

通过25 Gbps的SERDES链路设计的实例,介绍了如何应用三维电磁仿真工具以及链路仿真工具,在SERDES通道设计的不同阶段提供设计指导。

在布线前,通过对设计方案进行三维电磁建模,选择使用从顶层到底层的过孔作为扇出方案。在完成布线后,对通道进行三维电磁建模,找到过孔设计的最优值,但是最优值无法工程实现。采用工程可实现的优选值,又无法直接衡量其应用的风险。通过JCOM的链路仿真,验证优选值可以满足JESD204C的规范要求。

-

#硬声创作季 PCB设计快速入门课程:8.3 多通道层次电路PCB设计Mr_haohao 2022-09-07

-

PCB设计与应用:多通道层次原理图设计方法#PCB学习硬声知识 2022-11-10

-

PCB设计与应用:多通道层次电路PCB设计#PCB学习硬声知识 2022-11-10

-

求助FPGA高速串行收发器,输出12.5Gbps的信号要用什么电平 ...2014-11-10 0

-

PCB设计工程师福利来咯~2015-03-31 0

-

Cyclone IV 收发器体系结构2017-11-14 0

-

Cadence新Allegro平台为PCB设计工程师树立全新典范2018-08-28 0

-

如何实现高性能的PCB设计工程2019-07-29 1034

-

25-Gbps收发器使FPGA解决方案的性能提高了两倍多2019-12-19 757

-

Altera在FPGA中演示25-Gbps收发器性能,功能上优于竞争ASSP产品2021-01-04 1079

-

112Gbps GTM收发器的PCB通道设计指南2023-09-13 239

-

TIDA-010132-适用于雷达和电子战应用的多通道射频收发器 PCB layout 设计2024-05-11 198

-

DS25BR400四通道2.5 Gbps CML收发器数据表2024-07-04 120

-

TLK6002双通道0.47Gbps至6.25Gbps多速率收发器数据表2024-07-09 107

-

TLK10002 10Gbps双通道多速率收发器数据表2024-07-09 111

全部0条评论

快来发表一下你的评论吧 !