ADC3581 技术文档总结

描述

ADC358x 是一款低噪声、超低功耗 18 位 65 MSPS 高速 ADC 系列。它专为低噪声性能而设计,可提供 -160 dBFS/Hz 的噪声频谱密度以及出色的线性度和动态范围。ADC358x 提供非常好的直流精度以及 IF 采样支持,使其适用于广泛的应用。高速控制环路受益于低至1个时钟周期的短延迟。ADC在65 Msps时仅消耗119 mW,其功耗在较低采样率下可很好地扩展。

*附件:adc3581.pdf

ADC358x 使用串行 LVDS (SLVDS) 接口输出数据,从而最大限度地减少数字互连的数量。该设备支持单通道和双通道选项。ADC358x 是一个引脚对引脚兼容系列,具有不同的速度等级。它采用 40 引脚 QFN 封装 (5 x 5 mm),支持 -40 至 +105⁰C 的扩展工业温度范围。

特性

- 18 位 10/25/65 MSPS ADC

- 本底噪声:-160 dBFS/Hz

- 超低功耗,优化功率缩放:77 mW (10 MSPS) 至 119 mW (65 MSPS)

- 延迟:1个时钟周期(1线SLVDS)

- 指定的 18 位,无缺失代码

- INL/DNL:±7/ ±0.7 LSB(典型值)

- 参考:外部或内部

- 输入带宽:900 MHz (3dB)

- 工业温度范围:-40 至 +105°C

- 片上数字滤波器(可选)

- 抽取 2、4、8、16、32

- 32 位 NCO

- 串行LVDS数字接口(2线、1线和1/2线)

- 小尺寸:40-WQFN (5x5 mm) 封装

- 光谱性能 (f

在= 1 MHz):- 信噪比:84.5 dBFS

- SFDR:95 dBc HD2、HD3

- SFDR:100 dBFS 最差支线

- 光谱性能 (f

在= 20 兆赫):- 信噪比:83.5 dBFS

- SFDR:90 dBc HD2、HD3

- SFDR:95 dBFS 最差支线

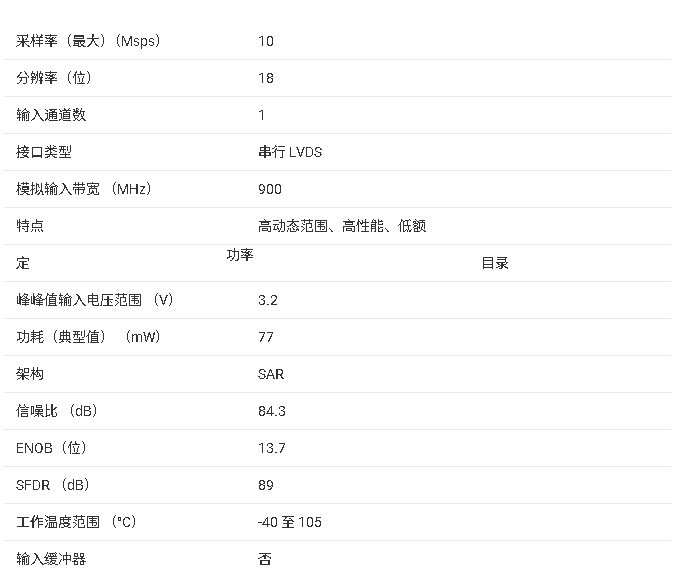

参数

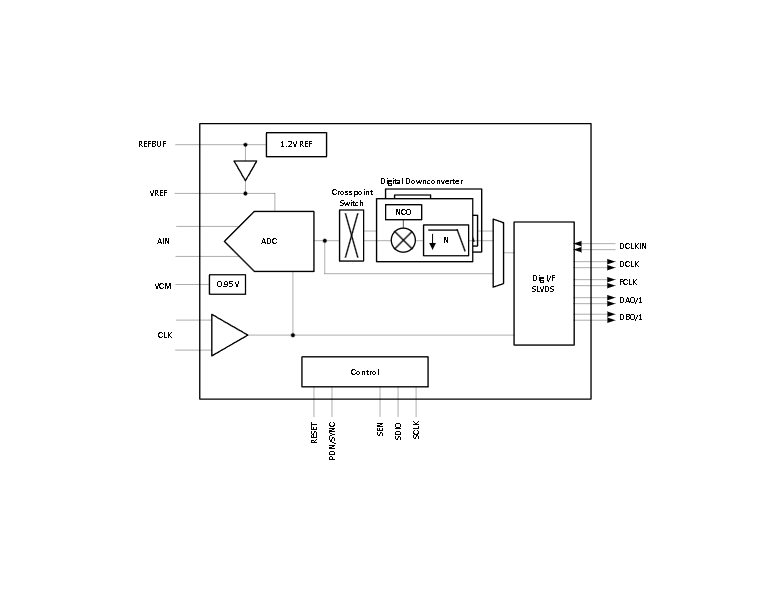

方框图

一、产品定位与核心属性

ADC3581 是德州仪器 ADC358x 系列中的 18 位高速模数转换器(ADC),专为高精度、低噪声场景设计,采样速率固定为 10 MSPS,采用 40 引脚 WQFN(5mm×5mm)封装,支持 - 40°C 至 + 105°C 工业级温度范围。其核心优势在于 18 位高分辨率与低噪声特性(噪声基底 - 151.5 dBFS/Hz)的结合,同时兼顾低功耗(1 线 SLVDS 接口下典型功耗 77 mW),适用于高速数据采集、工业监测、精密仪器仪表等对信号精度要求严苛的场景,且与同系列 ADC3582(25 MSPS)、ADC3583(65 MSPS)引脚兼容,便于方案灵活选型。

二、关键性能参数

1. 精度与线性度

- 分辨率与完整性 :18 位无缺失码,确保全量程信号转换无遗漏,支持 14/16/18/20 位输出分辨率调整(14/16 位时截断 LSB,20 位时补 0)。

- 线性误差 :微分非线性(DNL)典型值 ±0.7 LSB、最大值 ±0.9 LSB,积分非线性(INL)典型值 ±7 LSB、最大值 ±16 LSB,有效降低信号失真。

- 直流特性 :偏移误差(VOS_ERR)典型值 ±10 LSB、最大值 ±410 LSB,偏移漂移(VOS_DRIFT)-0.01 LSB/°C;增益误差(GAIN_ERR)外接 1.6V 参考时典型值 0.44% FSR,内置参考时 - 1.2% FSR,增益漂移(GAIN_DRIFT)外接参考时 0.9 ppm/°C,温漂特性优异,保障宽温环境下精度稳定。

2. 动态性能(典型值,外接 1.6V 参考,-1 dBFS 差分输入)

- 信噪比(SNR) :1.1 MHz 输入时 84.6 dBFS,4.9 MHz 输入时 83.9 dBFS(最大值),9.9 MHz 输入时 82.9 dBFS,高频场景下仍保持高信号纯净度。

- 无杂散动态范围(SFDR) :1.1 MHz 输入时 87 dBc,4.9 MHz 输入时 89 dBc(最大值),9.9 MHz 输入时 87 dBc,有效抑制杂散干扰。

- 总谐波失真(THD) :1.1 MHz 输入时 86 dBc,4.9 MHz 输入时 90 dBc(最大值),9.9 MHz 输入时 89 dBc,低失真特性适配高精度信号采集。

- 噪声谱密度(NSD) :1.1 MHz 输入、-20 dBFS 时 - 151.5 dBFS/Hz,为微弱信号检测提供基础。

3. 功耗与接口特性

- 功耗 :模拟电源电流(I_AVDD)典型值 18 mA、最大值 27 mA;1 线 SLVDS 接口下 I/O 电源电流(I_IOVDD)典型值 25 mA、最大值 43 mA,1/2 摆幅模式下可降至 19 mA,2 线模式下 29 mA,功耗灵活可控。

- 延迟 :1 线 / 1/2 线 SLVDS 接口仅 1 个时钟周期,适配高速控制环路。

- 输入带宽 :3 dB 带宽 900 MHz,支持中频(IF)采样,无需额外降频电路。

三、硬件设计关键信息

1. 引脚功能与配置

- 模拟输入 :AINP(引脚 12,正端)、AINM(引脚 13,负端)为差分输入,共模电压(VCM,引脚 8)固定 0.95 V(典型值),输入阻抗 8 kΩ(100 kHz 时)、电容 7 pF(100 kHz 时),满量程输入 3.2 Vpp(差分),需匹配驱动电路输出范围。

- 电源引脚 :AVDD(引脚 5、15、36)为模拟 1.8 V 电源,IOVDD(引脚 21、30)为数字接口 1.8 V 电源,需独立供电避免数字噪声耦合至模拟电路;GND(含底部散热焊盘)与 IOGND(引脚 26)需单点连接,降低接地噪声。

- 控制与通信引脚 :

- PDN/SYNC(引脚 1):高有效,可配置为电源关断或同步功能,内置 21 kΩ 下拉电阻。

- RESET(引脚 9):硬件复位,高有效,内置 21 kΩ 下拉电阻。

- SPI 接口:SEN(引脚 16,片选,低有效,内置 21 kΩ 上拉至 AVDD)、SCLK(引脚 35,时钟,内置 21 kΩ 下拉)、SDIO(引脚 10,数据 I/O,内置 21 kΩ 下拉),支持 20 MHz 最高时钟频率,24 位数据读写(16 位地址 + 8 位数据)。

2. 参考电压与时钟设计

- 参考电压选项 :

- 外接 1.6 V 参考:直接接入 VREF(引脚 2),需搭配 10 μF+0.1 μF 旁路电容,负载电流约 1 mA。

- 外接 1.2 V 参考:接入 REFBUF(引脚 4),通过内部增益缓冲生成 1.6 V 参考,负载电流 < 100 μA,需在 REFBUF 与 REFGND(引脚 3)间加 10 μF+0.1 μF 旁路电容。

- 内置参考:生成 1.6 V 参考,输出阻抗 8 Ω,额外消耗 3 mA 模拟电流,适合对成本敏感、精度要求中等的场景。

- 时钟输入 :支持差分(CLKP 引脚 6、CLKM 引脚 7)与单端输入,差分模式可 AC 耦合(内部自偏置),单端模式需 DC 耦合至 0.9 V 中心电压,且未使用端需 AC 接地;时钟占空比推荐 40%-60%,高摆率时钟可降低孔径抖动(典型值 180 fs)。

3. 数字接口与数据处理

- SLVDS 接口 :支持 2 线、1 线、1/2 线模式,1 线模式下数据速率 180 MBPS(10 MSPS 时),2 线模式下 90 MBPS/lane,需外部输入 DCLKIN 时钟(差分,V_ID 200-650 mVpp),且与采样时钟频率锁定。

- 数字下变频器(DDC) :可选 2/4/8/16/32 倍抽取,支持实抽取(低通滤波)与复抽取(含 32 位 NCO,频率可调范围 - FS/2 至 FS/2),复抽取时可通过 DB0/1 接口实现双频段输出,抽取后延迟增加 21-23 个输出时钟周期(依抽取倍数而定)。

四、功能模块与配置

1. 模拟前端优化

- 自动调零(Auto-Zero) :默认启用,可通过 SPI 寄存器(0x11,D0)关闭,有效降低 1/f 闪烁噪声,提升低频信号采集精度,4M 点 FFT 测试显示启用后低频段噪声抑制显著。

- 采样干扰滤波器 :推荐根据输入频率选择:DC-30 MHz 场景用 33 Ω 电阻 + 180 nH 电感 + 100 pF 电容;30-70 MHz 场景用 33 Ω 电阻 + 120 nH 电感 + 100 pF+82 pF 电容,吸收采样开关产生的毛刺。

2. 数字功能配置

- 输出格式化 :支持 14/16/18/20 位输出分辨率,通过输出位映射器(0x39-0x60、0x61-0x88 寄存器)调整位序;数据格式可通过 SPI 寄存器(0x8F、0x92)配置为二进制补码(默认)或偏移二进制。

- 测试模式 :支持斜坡(RAMP)、自定义固定模式,通过 0x14-0x16 寄存器配置,用于数字接口连通性测试,斜坡步长需匹配 ADC 原生分辨率(18 位对应 00001)。

- 电源管理 :支持全局电源关断(功耗低至 5 mW,内置参考)与局部模块关断(如时钟缓冲、参考放大器),通过 0x08、0x09、0x0D 寄存器配置,平衡功耗与唤醒时间。

3. SPI 寄存器关键配置

- 接口配置 :0x07 寄存器选择输出接口映射(18 位 1 线 SLVDS 对应默认配置),0x13 寄存器加载 E-Fuse 配置(需等待 1 ms),0x19 寄存器设置 FCLK 源与分频(复抽取时 FCLK_SRC=1)。

- 抽取配置 :0x24 寄存器使能 DDC(D1=1)与数字通路(D2=1),0x25 寄存器设置抽取倍数(如 8 倍复抽取对应 0x30),0x2A-0x2D、0x31-0x34 寄存器配置 NCO 频率。

- 增益与相位 :0x26 寄存器设置 mixer 增益(复抽取推荐 6 dB 补偿混合损耗),0x27、0x2E 寄存器调整 I/Q 输出顺序与延迟。

五、应用设计与布局建议

1. 典型应用电路

以精密工业监测系统为例,前端采用 THS4541 全差分放大器(支持 DC-70 MHz,3.3 V/-1 V 供电时输出摆幅 6.8 Vpp),搭配 DC-30 MHz 采样干扰滤波器,ADC 配置外接 1.6 V 参考(VREF 引脚接 REF5016),数据通过 1 线 SLVDS 传输至 FPGA,时钟采用差分晶振(如 Si5351,抖动 < 100 fs),确保动态性能达标。

2. 电源设计

- 推荐架构 :采用 “开关电源 + LDO” 组合,如 TPS62821(开关电源,效率 90%+)+TPS7A4701(LDO,噪声 < 10 μVrms),AVDD 与 IOVDD 独立供电,电源路径上串联铁氧体磁珠(如 BLM18PG102SN1)抑制高频噪声。

- 旁路电容 :AVDD、IOVDD 引脚旁就近放置 10 μF(钽电容)+0.1 μF(陶瓷电容),VREF 引脚旁放置 10 μF+0.1 μF 陶瓷电容,减少电压纹波。

3. 布局 Guidelines

- 模拟信号 :AINP/AINM、CLKP/CLKM 采用 100 Ω 差分布线,长度匹配(误差 <50 mil),避免过孔;与数字信号(如 DA0/1、DB0/1)间距> 200 mil,减少串扰。

- 参考电压 :VREF、REFBUF 引脚旁路电容直接焊接在顶层,无过孔,REFGND 与模拟地单点连接。

- 散热 :底部散热焊盘(GND PAD)需通过过孔连接至内层地平面,确保结温(T_J)不超过 105°C(推荐结温 < 85°C 以延长寿命)。

-

ADC3561/3562/3563 技术文档总结2025-10-30 1000

-

ADC354x 系列技术文档总结2025-10-29 1240

-

ADC3683-SP 技术文档总结2025-10-27 911

-

ADC3669 产品技术文档总结2025-10-24 998

-

ADC3568/ADC3569 ADC 产品文档总结2025-10-23 956

-

3581A/C Wave Analyzer操作和维修手册2018-11-13 872

-

UCC3581 微功耗电压模式 PWM2018-11-02 305

-

BLE技术总结文档2015-10-29 813

全部0条评论

快来发表一下你的评论吧 !