ADS117L11 技术文档总结

描述

该ADS117L11是一款 16 位 Δσ 模数转换器 (ADC),使用宽带滤波器的数据速率高达 400 kSPS,使用低延迟滤波器的数据速率高达 1067 kSPS。该器件将交流性能和直流精度完美结合,功耗低(高速模式下为 18.6 mW)。

该器件集成了输入和基准缓冲器,以减少信号负载。低漂移调制器可实现出色的直流精度和低带内噪声,从而实现出色的交流性能。功率可扩展架构提供两种速度模式来优化数据速率、分辨率和功耗。

*附件:ads117l11.pdf

数字滤波器可配置为宽带或低延迟作,优化交流性能或直流信号的数据吞吐量,所有这些都在一个器件中完成。

串行接口具有菊花链功能,可减少隔离栅上的SPI I/O。输入和输出数据以及寄存器设置通过循环冗余校验 (CRC) 功能进行验证,以提高运行可靠性。

小型 3 mm × 3 mm WQFN 封装专为空间有限的应用而设计。该器件完全符合–40°C至+125°C温度范围的额定工作。

特性

- 可编程数据速率:

- 高达 400 kSPS(宽带滤波器)

- 高达 1.067 MSPS(低延迟滤波器)

- 可选数字滤波器:

- 宽带或低延迟

- 交流精度与直流精度:

- 动态范围:97.5 dB (200 kSPS),典型值

- THD:–110 dB,典型值

- INL:0.5 LSB,典型值

- 失调漂移:50 nV/°C,典型值

- 增益漂移:0.6 ppm/°C,典型值

- 电源可扩展架构:

- 高速模式:400 kSPS,18.6 mW

- 低速模式:50 kSPS,3.3 mW

- 输入和基准预充电缓冲器

- 内部或外部时钟

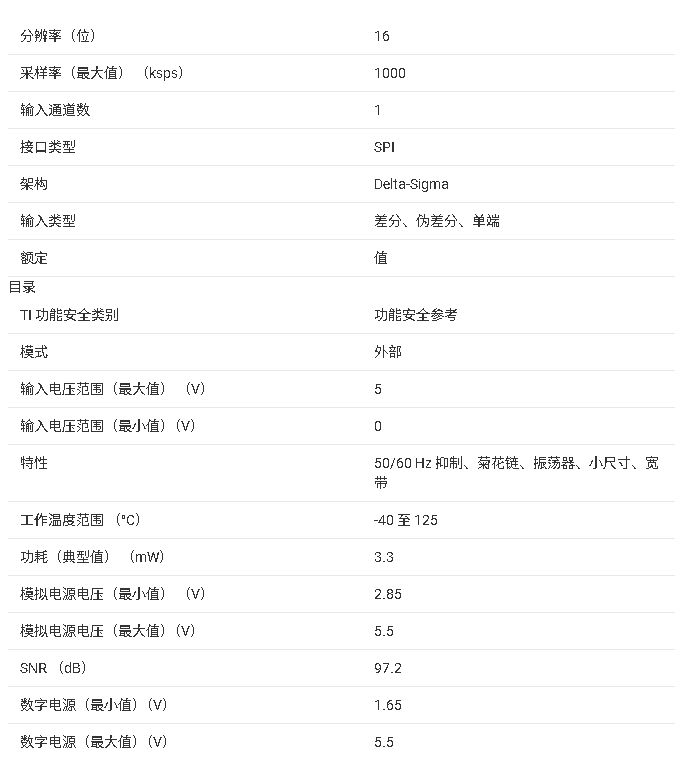

参数

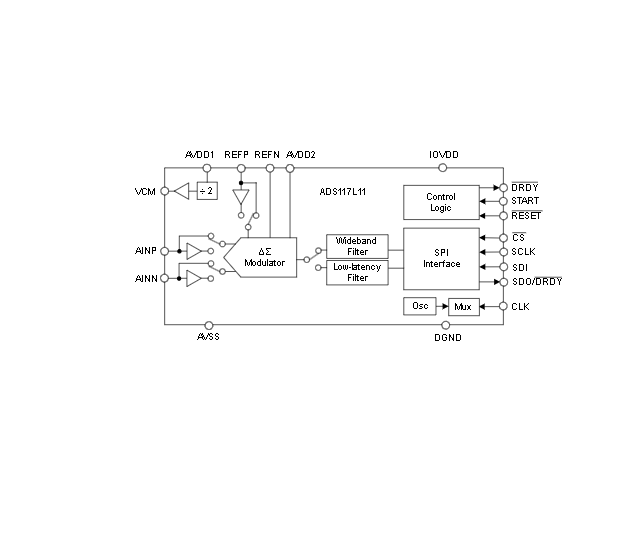

方框图

一、产品定位与核心属性

ADS117L11 是德州仪器推出的 16 位高精度 ΔΣ 模数转换器(ADC) ,采用 3mm×3mm 20 引脚 WQFN 封装,支持 - 40°C 至 + 125°C 宽温工作范围,专为高精度信号采集场景设计,如测试测量(数据采集、振动仪器、声学设备)、工厂自动化(模拟输入模块)、医疗(脉搏血氧仪)及电网基础设施(电力质量分析仪)。其核心优势在于 功率可缩放架构 (高速模式 400 kSPS/18.6 mW,低速模式 50 kSPS/3.3 mW)、优异的动态性能(动态范围 97.5 dB、THD -110 dBc)与直流精度(INL 0.5 LSB、偏移漂移 50 nV/°C),同时集成输入与基准预充电缓冲器,简化前端驱动设计,适配多场景高精度信号采集需求。

二、关键性能参数

1. 精度与线性度

- 分辨率与完整性 :16 位无缺失码,支持 1x(±V_REF)/2x(±2V_REF)输入量程切换,可通过配置实现双极性(2's 补码)或单极性(二进制)数据输出,适配不同信号类型。

- 线性误差 :积分非线性(INL)典型值 0.5 LSB,微分非线性(DNL)未明确最大值(需结合应用场景评估),确保全量程信号转换线性度。

- 直流特性 :25°C 时偏移误差 ±30 μV(最大值 ±250 μV),偏移漂移典型值 50 nV/°C(最大值 200 nV/°C);增益误差 ±200 ppm FSR(最大值 ±2000 ppm FSR),增益漂移典型值 0.6 ppm/°C(最大值 2 ppm/°C),温漂特性优异,宽温环境下精度稳定。

- 抗干扰能力 :直流共模抑制比(CMRR)110-120 dB,10 kHz 时 115 dB;电源抑制比(PSRR)AVDD1/AVDD2/IOVDD 直流均为 95-100 dB,有效抑制共模干扰与电源噪声。

2. 动态性能(典型值,AVDD1=5V,V_REF=4.096V,1x 量程)

| 参数 | 测试条件 | 典型值 | 单位 |

|---|---|---|---|

| 信噪比(SNR) | 高速模式,宽带滤波器,f_IN=1kHz,OSR=64 | 97.5 | dBFS |

| 总谐波失真(THD) | 高速模式,f_IN=1kHz,-0.2 dBFS 输入 | -110 | dBc |

| 无杂散动态范围(SFDR) | 高速模式,f_IN=1kHz | 110 | dBc |

| 噪声谱密度(NSD) | 高速模式,宽带滤波器,OSR=32 | 10.6 | μVrms |

| 正常模式抑制比(NMRR) | f_IN=50/60Hz,对应采样率 | 100 | dB |

3. 功耗与速率特性

- 功率可缩放 :高速模式(f_CLK=25.6 MHz)功耗 18.6 mW(400 kSPS),低速模式(f_CLK=3.2 MHz)功耗 3.3 mW(50 kSPS),支持空闲、待机、掉电模式,待机功耗 60 μA,掉电功耗 5 μA,适配低功耗场景。

- 采样速率 :宽带滤波器最高 400 kSPS(高速模式)/50 kSPS(低速模式);低延迟滤波器(sinc4/sinc3)最高 1.067 MSPS(高速模式)/133 kSPS(低速模式),速率与功耗灵活平衡。

- 输入特性 :输入阻抗 8 kΩ(100 kHz),输入电容 7 pF(100 kHz),支持差分输入,共模电压(VCM 引脚)输出 0.95 V((AVDD1+AVSS)/2),可直接驱动外部全差分放大器。

三、硬件设计关键信息

1. 引脚功能与配置

- 模拟输入 :单通道差分输入(AINP/AINN),支持 AC/DC 耦合,1x 量程时满量程输入 ±V_REF,2x 量程时 ±2V_REF;集成输入预充电缓冲器(CONFIG1 寄存器控制使能),降低前端驱动带宽需求。

- 基准电压 :差分基准输入(REFP/REFN),支持低基准范围(0.5-2.75V)与高基准范围(1V 至 AVDD1-AVSS),集成 REFP 预充电缓冲器(CONFIG1 寄存器控制),减少基准采样电流(典型值 ±2 μA)。

- 电源引脚 :

- 模拟电源:AVDD1(引脚 20,4.5-5.5V 高速模式 / 2.85-5.5V 低速模式)、AVDD2(引脚 19,1.74-5.5V)、AVSS(引脚 17,地),需独立供电避免噪声耦合。

- 数字电源:IOVDD(引脚 13,1.65-5.5V),为 SPI 接口与数字核心供电。

- regulators 输出:CAPA(引脚 18,模拟 LDO 输出,需外接 1μF 电容)、CAPD(引脚 15,数字 LDO 输出,需外接 1μF 电容),保障内部电路稳定。

- 控制与通信引脚 :

- SPI 接口:CS(引脚 7,片选低有效)、SCLK(引脚 9,时钟)、SDI(引脚 8,数据输入)、SDO/DRDY(引脚 10,数据输出 / 数据就绪),支持 3 线 / 4 线模式、菊花链连接,集成 CRC 校验(SPI 通信与寄存器映射)。

- 同步 / 复位:START(引脚 16,转换启动)、RESET(引脚 6,硬件复位低有效,内置 20 kΩ 上拉)、DRDY(引脚 11,数据就绪低有效)。

2. 时钟与基准设计

- 时钟选项 :支持内部振荡器(高速模式 25.6 MHz±0.8%,低速模式 3.2 MHz±0.9%)或外部时钟(高速模式 0.5-26.2 MHz,低速模式 0.5-3.28 MHz),外部时钟可通过 CLK_DIV 寄存器分频(÷8)适配低速模式,时钟抖动需控制(如 200 kHz 信号需 < 20 ps rms)以避免 SNR 劣化。

- 基准配置 :推荐外接高精度基准(如 REF6041 4.096V),REFP/REFN 引脚需就近放置 1μF+0.1μF 旁路电容;低基准范围(如 2.5V)适配 2x 量程,高基准范围(如 4.096V)仅支持 1x 量程,需通过 CONFIG1 寄存器的 REF_RNG 位匹配基准电压。

3. 数字接口与数据处理

- SPI 通信 :兼容 SPI 模式 1(CPOL=0,CPHA=1),支持全双工操作,帧长度 16/24/32 位(含 STATUS 头 / CRC 字节),菊花链模式可减少多 ADC 系统的 SPI 引脚占用,最大级联数量受 SCLK 频率与数据率限制(如 20 MHz SCLK、100 kSPS 数据率时最多 6 片)。

- 数据格式 :双极性输出为 16 位 2's 补码(范围 - 8000h 至 7FFFh),单极性为 16 位二进制(范围 0000h 至 FFFFh),可通过 CONFIG4 寄存器的 BIP_UNI 位切换,数据读取支持同步 / 启动 - 停止 / 单触发三种控制模式。

四、功能模块与配置

1. 模拟前端优化

- 输入缓冲器 :AINP/AINN 预充电缓冲器(CONFIG1 寄存器 AINP_BUF/AINN_BUF 位),使能后输入电流降至 ±0.4 μA(低速模式),减少前端驱动负载,适配高阻抗传感器(如应变片)直接连接;禁用时输入电流 95 μA/V(高速模式),需前端驱动具备足够带宽。

- 输入多路选择(MUX) :支持正常极性、反相极性、偏移测试(输入短接至共模电压)、共模测试(输入短接后接 AINP)四种模式,可通过 MUX 寄存器配置,用于系统校准与性能验证。

- 扩展量程 :CONFIG2 寄存器 EXT_RNG 位使能后,输入量程扩展 25%(如 1x 量程变为 ±1.25V_REF),提供信号余量,但 SNR 在输入超 110% 满量程时会因调制器饱和劣化。

2. 数字滤波器配置

- 宽带滤波器 :多抽头 FIR 结构,支持 OSR 32-4096 可调,-0.1 dB 带宽 0.4×f_DATA,-3 dB 带宽 0.437×f_DATA,群延迟 34/f_DATA,适合 AC 信号采集(如振动、声学),高速模式 OSR=32 时数据率 400 kSPS,噪声 10.6 μVrms。

- 低延迟滤波器 :含 sinc4、sinc4+sinc1、sinc3、sinc3+sinc1 四种配置, latency 最短 4.38 μs(高速模式 sinc4,OSR=12),适合 DC 信号快速采集(如医疗监护),sinc3 模式支持 50/60 Hz 工频抑制(NMRR 100 dB)。

- 过采样与噪声 :OSR 可调(32-4096),噪声随 OSR 增加降低(如高速模式 OSR=4096 时噪声 0.92 μVrms),量化噪声与热噪声共同决定 SNR,多数速率下量化噪声占主导(SNR≈98 dB)。

3. 校准与电源管理

- 校准功能 :支持 24 位偏移(OFFSET2/1/0 寄存器)与增益(GAIN2/1/0 寄存器)校准,偏移校准通过减去校准值实现,增益校准通过乘以归一化系数(GAIN/400000h)实现,需存储校准系数至外部非易失性存储器,上电后重新配置。

- 电源模式 :

- 正常模式:全功能工作,高速 / 低速模式可通过 SPEED_MODE 位切换。

- 待机模式:转换停止时自动进入,功耗降至 60 μA,重启需额外 24 个时钟周期。

- 掉电模式:CONFIG2 寄存器 PWDN 位使能,仅保留 SPI 与数字 LDO,功耗 5 μA,唤醒需清除 PWDN 位或复位。

五、应用设计与布局建议

1. 典型应用电路

以高精度数据采集系统为例,前端采用 THS4551 全差分放大器(135 MHz GBW,50 ns settling 时间),搭配 4 阶抗混叠滤波器(无源 RC + 有源 MFB 结构),实现 12.8 MHz(高速模式调制器频率)处 90 dB 衰减;ADC 配置为高速模式、1x 量程、宽带滤波器(OSR=32),基准采用 REF6041 4.096V(噪声 10 μVrms),数据通过 SPI 传输至 FPGA,时钟采用低抖动晶振(如 Si5351,抖动 < 100 fs),保障双通道同步采样精度。

2. 电源与滤波设计

- 电源架构 :AVDD1 推荐 “开关电源(如 TPS62821)+3Ω 串联电阻 + 1μF+0.1μF 旁路电容”,AVDD2/IOVDD 直接并联 1μF+0.1μF 电容,CAPA/CAPD 引脚分别外接 1μF 电容至 AVSS/DGND,减少电源纹波与 LDO 噪声。

- 抗混叠滤波 :模拟输入串联 22Ω 电阻 + 2.2 nF 电容(截止频率≈3.6 MHz),REFP/REFN 引脚并联 1μF+0.1μF 电容,抑制高频噪声耦合,适配 ΔΣ ADC 的噪声整形特性。

3. 布局 Guidelines

- 信号分区 :模拟信号(AINP/AINN、REFP/REFN、CLK)与数字信号(SPI、DRDY)分开布线,模拟区域远离功率器件(如 MOSFET),数字走线避免穿越模拟地平面。

- 差分布线 :AINP/AINN、REFP/REFN、CLK 采用 100Ω 差分布线,长度匹配误差≤50 mil,减少相位偏移;模拟输入线最短路径布线,避免过孔,降低寄生电感。

- 散热设计 :底部热焊盘(Thermal Pad)需通过过孔连接至内层地平面,结合 PCB 散热设计(如铜皮面积≥10 mm²),确保结温(T_J)不超过 125°C(推荐 < 100°C 以延长寿命)。

-

ADS7067 技术文档总结2025-10-30 720

-

ADS127L21 技术文档总结2025-10-29 367

-

ADS9817 技术文档总结2025-10-27 442

-

ADS127L21B 产品技术文档总结2025-10-24 481

-

ADS127L14/ADS127L18 ADC 产品文档总结2025-10-23 616

-

ADS117L14/ADS117L18 核心信息总结2025-10-22 460

-

ADS127L11和ADS127L01相比主要突出的特点有哪些?2024-11-25 514

-

THP210和ADS127L11性能2024-08-27 488

-

ADS117L11 400 kSPS、宽带宽、16位、Δ-ΣADC数据表2024-07-16 405

-

理解和运用ADS127L11EVM GUI中的Histogram Analysis2022-10-28 659

全部0条评论

快来发表一下你的评论吧 !