AFE7903 技术文档总结

描述

AFE7903是一款高性能、宽带宽的多通道收发器,集成了两个射频采样发射器链和两个射频采样接收器链。该器件的工作频率高达 7.4GHz,可在 HF、VHF、UHF、L、S 和 C 波段频率范围内实现直接射频采样,而无需额外的变频级。这种密度和灵活性的提高使高通道数的多任务系统成为可能。

TX信号路径支持插值和数字上变频选项,可提供高达400MHz的信号带宽。DUC 的输出驱动 12GSPS DAC(数模转换器),具有混合模式输出选项,以增强二次奈奎斯特作。DAC输出包括一个可变增益放大器(TX DSA),具有40dB范围和1dB模拟步长和0.125dB数字步长。

*附件:afe7903.pdf

每个接收器链包括一个 25dB 范围的 DSA(数字步进衰减器),然后是一个 3GSPS ADC(模数转换器)。每个接收器通道都有一个模拟峰值功率检测器和各种数字功率检测器,以辅助外部或内部自主自动增益控制器,以及用于器件可靠性保护的射频过载检测器。灵活的抽取选项可优化两个接收器高达 400MHz 的数据带宽。

该器件包含一个SYSREF时序检测器,允许相对于器件时钟优化SYSREF输入时序。

特性

- 双射频采样 12GSPS 发射 DAC

- 双射频采样3GSPS接收ADC

- 每个 TX 或 RX 的最大信号带宽:400MHz

- 射频频率范围:5MHz - 7.4GHz

- 数字步进衰减器 (DSA):

- TX:40dB范围,0.125dB步长

- 接收:25dB 范围,0.5dB 步长

- 用于 TX 和 RX 的单频或双频 DUC/DDC

- 每个 TX/RX 16 个 NCO

- 可选内部PLL/VCO,用于DAC/ADC时钟或DAC或ADC采样率的外部时钟

- Sysref 对准检测器

- SerDes 数据接口:

- JESD204B和JESD204C兼容

- 8 个高达 29.5Gbps 的 SerDes 收发器

- 子类 1 多设备同步

- 封装:17mm × 17mm FCBGA,0.8mm 间距

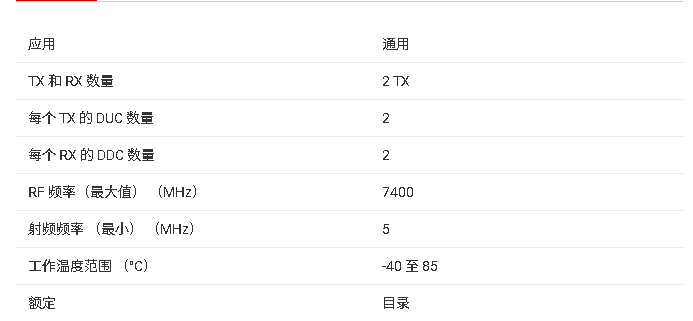

参数

方框图

一、产品核心定位

AFE7903 是德州仪器(TI)推出的 高集成度 2 发 2 收(2T2R)射频采样模拟前端(AFE) ,专为宽频段、高带宽射频信号处理设计,覆盖 5MHz 至 7.4GHz 超宽射频范围,无需额外频率转换模块即可直接采样 HF、VHF、UHF、L、S 及 C 频段信号。其核心优势在于 高采样速率 (发射 DAC 达 12GSPS、接收 ADC 达 3GSPS)、400MHz 超大瞬时带宽(IBW) 与 灵活的信号处理能力 ,采用 17mm×17mm 400 引脚 FC-BGA 封装,满足雷达、国防通信、无线测试等对高带宽、高精度射频信号处理的需求,工作温度范围 - 40°C 至 85°C(环境温度),结温最高 110°C。

二、关键特性

1. 高性能收发通道

(1)发射通道(TX)

- 高采样与带宽 :集成 2 路 12GSPS 射频采样 DAC,支持 1st/2nd 奈奎斯特区输出,不同 DAC 速率下覆盖频率范围灵活 —— 如 DAC=12GSPS(1st 奈奎斯特)时输出 5-6000MHz,DAC=9GSPS(2nd 奈奎斯特)时可延伸至 7400MHz;每通道最大信号带宽 400MHz,支持高速信号传输。

- 数字步进衰减器(DSA) :衰减范围 40dB,模拟步进 1dB、数字步进 0.125dB,衰减精度高(0-40dB 范围内微分非线性 DNL±0.2dB),且相位精度优异(30MHz-4900MHz 频段内 ±1°),适配不同功率需求场景。

- 低失真与高动态 :3 阶交调失真(IMD3)典型值低至 - 47dBc(5MHz 输入)、-79dBc(2600MHz 输入);无杂散动态范围(SFDR)最高 62dBc(850MHz 输入),2 次谐波失真(HD2)低至 - 72dBc(5MHz 输入),有效抑制信号失真。

(2)接收通道(RX)

- 高采样与灵敏度 :集成 2 路 3GSPS 射频采样 ADC,14 位分辨率,支持灵活抽取(最高 24 倍),优化后数据带宽可达 400MHz;最小满量程输入功率(PFS_CW,min)低至 - 2.9dBm(830MHz 输入),适配微弱信号检测。

- 数字步进衰减器(DSA) :衰减范围 25dB,步进 0.5dB,校准后衰减精度 ±0.1dB,增益平坦度优异(80MHz 带宽内 0.2dB、400MHz 带宽内 1.1dB),减少信号幅度波动。

- 低噪声与高动态 :噪声谱密度(NSD)低至 - 156.6dBFS/Hz(410MHz 输入),噪声系数(NF)最小 19.1dB(830MHz 输入);3 阶交调失真(IMD3)低至 - 82dBc(30MHz 输入),无杂散动态范围(SFDR)最高 100dBFS(30MHz 输入),确保微弱信号检测精度。

2. 灵活的时钟与同步

- 时钟方案 :支持内部 PLL/VCO 或外部时钟驱动 DAC/ADC,内部 PLL 参考时钟频率最高 491.52MHz,VCO 覆盖 7.2-11.7965GHz 频段,闭环相位噪声低至 - 113dBc/Hz(600kHz 偏移,11.79848GHz 输出),确保时钟稳定性。

- 同步能力 :集成 SYSREF 时序检测器,优化 SYSREF 与器件时钟的时序对齐;支持 JESD204B/C 协议 SerDes 接口(8 路收发器,最高速率 29.5Gbps),子类 1(Subclass 1)多器件同步,适配多通道协同工作场景。

3. 高可靠性与适应性

- 电气防护 :ESD 防护符合人体放电模型(HBM)1000V、带电器件模型(CDM)1500V;绝对最大额定值覆盖宽电源范围(如 DVDD0P9 为 - 0.3-1.2V,VDD1P8 系列为 - 0.5-2.1V),避免电压波动损坏器件。

- 热性能 :FC-BGA 封装热阻优异,结到环境热阻(RθJA)16.2°C/W,结到顶部外壳热阻(RθJC (top))0.42°C/W,配合热焊盘设计,有效散热,确保高功率下稳定工作。

三、典型应用场景

- 雷达系统 :覆盖 5MHz-7.4GHz 宽频段,3GSPS ADC 与 12GSPS DAC 支持高速目标探测与信号生成,400MHz 带宽可同时处理多目标信号;低相位噪声(-128dBc/Hz@100kHz 偏移)确保测距、测速精度。

- 国防通信与导引头前端 :适配战术通信的宽频段需求,无需额外混频模块,直接采样处理射频信号;高动态范围(SFDR 最高 100dBFS)可抵御复杂电磁环境干扰,保障信号传输可靠性。

- 无线通信测试设备 :400MHz 瞬时带宽支持多标准信号(如 LTE 20MHz、NR 100MHz)生成与分析,ACPR(邻道功率比)低至 - 72dBc(2600MHz LTE 信号),满足无线设备性能测试要求。

- 卫星与射频监测 :7.4GHz 最高频率覆盖 C 频段卫星信号,高采样速率与低失真特性,可精准捕获、分析宽 band 射频信号,适配监测与接收场景。

四、器件信息与订购参数

1. 基础器件信息

| 型号 | 通道配置 | 射频范围 | 发射 DAC 速率 | 接收 ADC 速率 | 封装类型 | 主体尺寸 | 工作温度(环境) | 结温(工作) |

|---|---|---|---|---|---|---|---|---|

| AFE7903 | 2T2R | 5MHz-7.4GHz | 最高 12GSPS | 最高 3GSPS | 400 引脚 FC-BGA(ALH) | 17mm×17mm | -40°C 至 85°C | 最高 110°C |

2. 订购选项详情

| 可订购器件 | 状态 | 封装类型 | 每盘数量(SPQ) | 环保标准 | 湿度敏感等级(MSL) | 引脚镀层 |

|---|---|---|---|---|---|---|

| AFE7903ALH | 现役(Active) | 17mm×17mm FC-BGA | 240(JEDEC 托盘) | RoHS 合规 | 3 级(260°C-168 小时) | 咨询 TI |

| AFE7903ALH.B | 现役(Active) | 17mm×17mm FC-BGA | 240(JEDEC 托盘) | - | 咨询 TI | 咨询 TI |

五、核心电气特性

1. 电源与电流

- 多电压域供电 :需搭配 0.9V(DVDD0P9/VDDT0P9)、1.2V(VDD1P2RX/TXCLK 等)、1.8V(VDD1P8RX/TX 等)多组电源,推荐工作电压精度高(如 0.9V 域为 0.9-0.95V)。

- 功耗优化 :不同工作模式下功耗差异明显 —— 如 2T2R TDD 模式(50% 占空比)功耗约 2166mW,休眠模式(SLEEP 引脚拉高)功耗仅 596mW,适配低功耗需求场景。

2. 射频关键参数(典型值,TA=25°C)

| 参数 | 测试条件 | 发射通道(TX) | 接收通道(RX) |

|---|---|---|---|

| 输出功率 | DAC=6GSPS,-0.1dBFS | 6.5dBm(30MHz)、2.3dBm(2600MHz) | - |

| 输入功率 | ADC=1500MSPS,DSA=0dB | - | -2.9dBm(830MHz)、0.1dBm(4910MHz) |

| 噪声谱密度(NSD) | 20MHz 偏移 | -154dBFS/Hz(30MHz,0dB 衰减) | -156.6dBFS/Hz(410MHz,3dB 衰减) |

| 3 阶交调失真(IMD3) | 双音输入,-7dBFS each | -47dBc(5MHz)、-79dBc(2600MHz) | -82dBc(30MHz)、-74dBc(2610MHz) |

六、核心功能模块

1. 信号处理模块

- 数字上 / 下变频器(DUC/DDC) :发射端支持单 / 双频段 DUC,内置 16 个数控振荡器(NCO),可实现信号插值(最高 48 倍)与频率搬移;接收端搭配 DDC,支持灵活抽取(最高 24 倍),优化数据带宽,减少后端处理压力。

- ΔΣ 调制与解调 :DAC 采用开关电容 ΔΣ 调制架构,将数字信号转换为 1 位比特流,通过射频采样直接输出;ADC 采用全差分架构,配合斩波稳定技术降低 1/f 噪声,提升微弱信号检测能力。

2. 隔离与传输

- 射频隔离 :发射与接收通道间隔离度高(2TXOUT 至 4TXOUT 隔离 - 83.2dBc@4900MHz),避免通道间串扰;输入 / 输出端阻抗匹配至 100Ω,输出回波损耗(S22)≤-12dB,确保信号传输效率。

- JESD204B/C 接口 :8 路 SerDes 收发器最高速率 29.5Gbps,支持 8b/10b 编码,子类 1 同步可实现多器件时钟对齐,延迟可控(发射通道 latency 典型 152-176 个接口时钟周期)。

3. 故障诊断与保护

- 实时监测 :接收通道集成模拟峰值功率检测器与数字功率检测器,辅助自动增益控制(AGC);射频过流检测器可保护器件免受过载损坏,温度传感器实时监测结温,过高时触发热关断。

- 错误检测 :内置 32 位校验和(Checksum)功能,检测 SPI 配置错误;错误标志寄存器记录过压、过流、电源异常等状态,便于系统故障诊断。

七、设计与应用指导

1. 硬件设计建议

- 电源设计 :不同电压域需独立供电,靠近引脚并联 0.1μF 陶瓷电容 + 1μF 钽电容滤波,减少电源噪声;高压域(如 TX DAC)需采用低压差稳压器(LDO),确保电压稳定。

- 射频接口 :TX/RX 射频引脚需匹配 100Ω 阻抗,布线短且远离数字电路;建议串联 10Ω 限流电阻与 1nF 隔直电容,避免直流偏置影响器件,同时抑制高频噪声。

- 时钟设计 :外部时钟源需低抖动(如≤100fs),CLKIN 布线采用 50Ω 阻抗匹配,多器件同步时共享 CLKIN,确保时序一致性;SYSREF 信号需与 CLKIN 严格对齐,建立时间与保持时间均≥50ps。

2. 布局与 EMC 优化

- 分区布局 :将高压射频区(TX/RX 引脚)、数字信号区(JESD204 接口)、电源区分开布线,射频路径远离数字时钟线,避免串扰;FC-BGA 底部热焊盘通过 4-6 个过孔连接至接地平面,增强散热。

- EMC 抑制 :电源路径串联磁珠(如 100Ω@100MHz)抑制高频噪声;数字接口串联 22Ω 匹配电阻,减少信号反射;AGND 与 DGND 单点连接,避免接地环路。

-

AFE5807 超声模拟前端技术文档总结2025-11-18 1105

-

AFE5828 技术文档核心内容总结2025-11-07 644

-

AFE4460 技术文档总结2025-10-30 694

-

AFE80xx 系列技术文档总结2025-10-29 911

-

AFE78101/AFE88101 技术文档总结2025-10-27 879

-

AFE8192技术文档完整总结2025-10-21 669

-

EVAL-AD7903 EVAL-AD7903评估板2021-07-12 374

-

EVAL-ADE7903 EVAL-ADE7903评估板2021-07-09 279

全部0条评论

快来发表一下你的评论吧 !