采用SOPC为的思路的指纹识别模块设计

处理器/DSP

描述

引言

未来的系统发展趋势是实现可编程片上系统(SOPC),将CPU、接口电路都融合到一块芯片当中。我们采用 Altera公司的 Cyclone系列器件中的 EP1C6Q240C8型号FPGA,它内部可嵌入 Nios II软核,通过用 VHDL语言设计指纹读取接口 UART加上模块需要的 IP核,使用 Quartus II软件中的SOPC Builder在 FPGA内部构建 Nios II系统,再通过管脚配置,与外围电路相连,在Nios II IDE环境中实现外围器件程序设计和指纹识别算法设计。构建一个以 Nios II为处理核心的 SOPC系统,使系统变得更加小巧、灵活。同时也实现了指纹芯片的前端设计,这也是这个课题的研究目的之一,再通过ASIC集成设计电路技术做成超大规模集成电路—指纹识别芯片。这样扩大了指纹技术的适用范围和应用市场领域,例如指纹汽车锁、指纹枪械、指纹掌上电脑、手机等嵌入式应用的广阔领域。

模块整体硬件设计

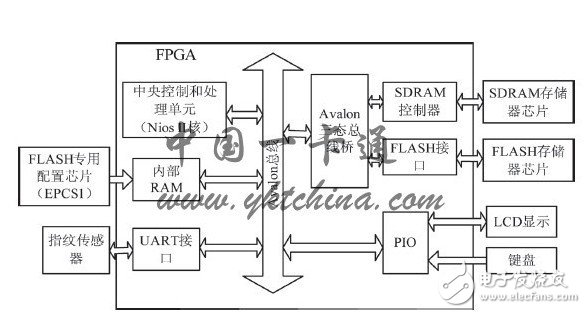

指纹识别模块的硬件设计采用 SOPC的设计思路[1],在FPGA内部实现指纹读取 UART接口、FLASH存储器接口、SDRAM控制器、PIO控制的键盘和 LCD显示接口。这个充分利用 FPGA的 IP核优势,利用 SOPCBuilder将这些接口、控制器和 PIO集成到 FPGA内部。各部分之间是通过 Avalon总线相连,形成以 Nios II处理器为核心的 SOPC系统,再通过 TCL脚本语言进行管脚配置,把 FPGA内部的输入输出信号配置到 FPGA的 IO管脚上,实现与外围器件指纹传感器、SDRAM存储器芯片、FLASH存储器芯片、键盘和 LCD显示连接。使用FPGA内部的Nios II 处理器进行控制,保证模块功能得以实现。整个识别模块的硬件框图如图1。

整个模块各个器件的功能是:FLASH专用配置芯片的作用是存储程序,每次上电时,为整个系统配置程序。因为FPGA是基于RAM结构的,所以在每次掉电时,程序会丢失。指纹读取接口 UART是要连接指纹传感器,进行指纹图像的正确读取。FLASH存储器用来保存指纹模板数据,保证指纹模板掉电后数据不丢失。SDRAM存储器为输入指纹数据的随机存储和正在匹配的指纹模板数据的存储。PIO控制,就是直接用FPGA管脚控制键盘和LCD显示。模块中有1个4×4的按键,功能:录入指纹健、删除指纹健、确认健、复位健、删除输入字符健、关机健、 0~9字符健。LCD显示匹配结果和各个功能的完成情况。中央控制和处理单元 NiosII处理器主要负责整个系统的协调工作、对外围器件的操作和指纹算法的处理。

图1

Altera的Cyclone EP1C6Q240C8型号FPGA,它的LE数目是5980,内部有 2个PLL,能内嵌 3种类型的 Nios II 处理器。且和别的 FPGA相比,能满足模块功能并且价格相对比较低廉。故设计中选用这款芯片。

利用 SOPC Builder构建 Nios II硬件系统

利用 SOPC Builder 组件在加入整个系统正常运行必须的标准性 Nios II 处理器和 RAM 存储器(onchip_memory)。这是整个指纹识别模块的核心处理单元。标准性的 NiosII 处理器占用 FPGA1200LE 资源,做到了性能和面积之间平衡,而且在性能上也能满足本系统设计要求,也为以后添加或修改功能做好准备。RAM 存储器选择的数据宽度是32bits,存储容量4K byte。用来存储程序中数据和数据缓存。

为了使 Nios II 软核与外部存储器之间进行通信,必须在Avalon 总线和连接外部存储器的总线之间加入 Avalon 三态总线桥[2]。可从添加 SOPC Builder 组件菜单中直接添加,如图 2 所示:

图2 Analon 三态总线桥

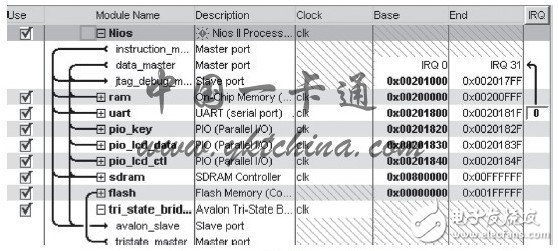

利用 SOPC Builder 最大的优势就是利用丰富的 IP 核资源。在 SOPC Builder 图形界面中添加 SDRAM 控制器 IP 核、FLASH 存储器接口 IP 核、P IOIP 核。SDRAM 控制器数据总线采用 16 位,Banks 选择 4 个,FLASH 存储器接口采用地址总线20,数据总线是16,按键选择 16 个PIO,液晶的控制端口选择 3 个PIO,数据端口选择 8 个PIO,这些数据的选择根据选择的外围器件而定。利用 IP 核即节省了开发时间又增加了系统的稳定性。

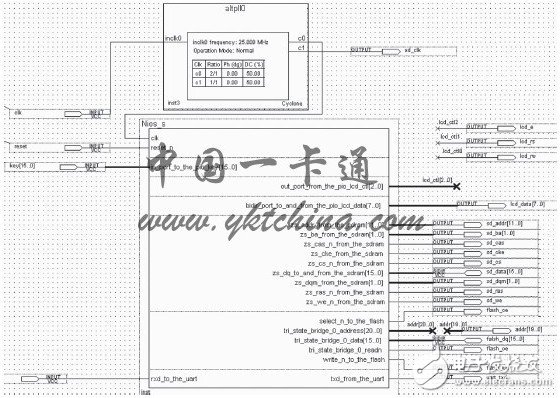

SOPC Builder 有自定义逻辑功能。把设计的指纹读取接口UART,通过组件编译器,创建 UART 组件[3],在 Avalon Components 下的 User Logic 中找到UART,把这个 UART 组件加到 SOPC 系统中。在 SOPC Builder 中添加的 Nios II 处理器、存储器、各种接口都是通过 Avalon 总线连接到一起的,在 Nios II 处理器协调下使各模块互相协调工作。Avalon 总线总线提供一个通道,使数据可以在各个模块之间高速的流动。对于总线竞争的问题,借助于 Avalon 总线所支持的主从外设访问方式可以得到有效的解决。本设计中,将通道中数据的流动分成主动和被动两个响应方式。在主动响应方式下,数据的流动由由各部件主动提出,在被动响应方式下,各部件只能响应其他部件的请求。SOPC Builder 通过 Auto-Assign Base Addresses 让系统自动分配基地址。通过 Auto-Assign IRQs 让系统自动分配中断。指纹识别模块的硬件整体配置图如图 3 所示。

图3 指纹识别模块的硬件整体配置图

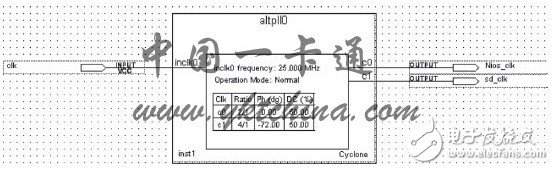

当在 SOPC Builder 中配置硬件完成后,运行Generate, 生成Nios II 系统。设计的FPGA 内部的PLL 系统时钟电路。当在处理指纹算法时,利用 FPGA 内部PLL(锁相环)的作用, 使处理速度加快。为了提高 SDRAM 存储器的存储速度,也需要提高系统时钟。利用 Quartus II 中的宏功能模块设计 PLL 内部接口如图4, clk 为 PLL 的输入时钟25MHz。Ratio 为倍频 / 分频系数,C0 是 Nios II 的时钟输入,倍频系数为2,所以Nios II 的时钟输入是50MHz,C1 是SDRAM 时钟输入,倍频系数是4,所以 SDRAM 的时钟输入频率是100MHz。

图4 利用宏模块设计的 PLL 内部接口

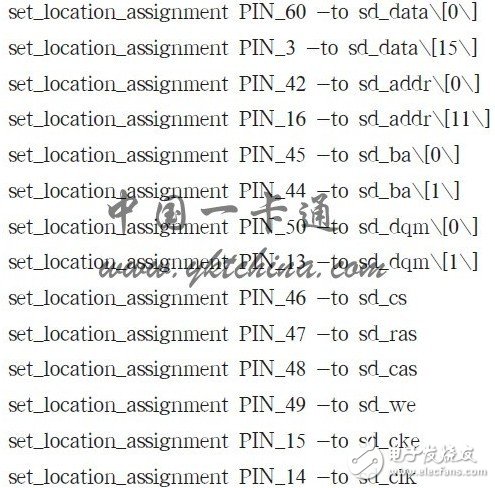

整个 SOPC 设计之后的 FPGA 内部 Nios II 系统如图5 所示,采用 TCL 脚本对 FPGA 进行管脚分配,下面是一段SDRAM 的 TCL 脚本 [4] 程序。实现与外部器件的连接。

图 5 FPGA 内部的 Nios II 系统图

结论

使用基于Nios II 处理器的SOPC 解决方案可大大缩短开发时间,拓展系统开发的灵活性,SOPC 已经成为现实。随着Nios II 核嵌入式处理器性能的不断提升以及其开发工具和 IP 核库的的不断完善,其用途将更加广泛。相信在不远的将来, 电子产品设计工程师将能够充分体会到 Nios II 处理器系统给他们设计带来的便捷。而且为我们自主研发指纹识别芯片提供了一种方法。

-

CW32模块使用 指纹识别传感器2024-09-18 1477

-

怎样去使用指纹识别模块呢2022-02-17 1404

-

ATK-AS608指纹识别模块的相关资料推荐2022-01-26 1733

-

求一种使用挂锁的指纹识别模块方案2022-01-10 1575

-

基于STC89C52单片机的指纹识别设计资料分享2021-11-10 1379

-

求一种指纹识别方案2021-07-21 2044

-

指纹识别模块原理是什么2020-06-08 10059

-

指纹识别技术原理及发展2018-11-12 4043

-

基于FPC1011C的指纹识别模块2018-11-05 3826

-

指纹识别模块厂家详解,指纹识别模块价格介绍2017-10-27 8333

-

DSP上的指纹识别模块的实现2017-02-08 849

-

指纹识别算法2016-08-23 4418

-

Proteus里有指纹识别模块吗?2015-09-15 8240

-

新唐指纹识别2015-01-27 5265

全部0条评论

快来发表一下你的评论吧 !